Wir betrachten UDB weiterhin auf der Grundlage der von Cypress geschützten Dokumentation, nämlich nützlicher Trivia in Bezug auf Datapath.

Der allgemeine Inhalt des Zyklus „UDB. Was ist das? "

Teil 1. Einführung. Pld.Teil 2. Datenpfad.Teil 3. Datenpfad-FIFO.Teil 4. Datenpfad ALU.Teil 5. Datenpfad. Nützliche Kleinigkeiten. (Aktueller Artikel)

Teil 6. Management- und Statusmodul.Teil 7. Steuermodul für Timing und ResetTeil 8. Adressierung von UDB21.3.2.6 CRC / PRS-Unterstützung

Datapath unterstützt die Generierung der CRC- (Cyclic Redundancy Checking) und Pseudozufallssequenzen (Pseudo Random Sequence, PRS). Verkettete Signale werden zwischen Datenpfadblöcken verfolgt, um CRC / PRS länger als 8 Bit zu unterstützen.

Die Nummer des höchstwertigen Bits (English Most Significant Bit, MSB) des höchsten CRC / PRS-Blocks wird ausgewählt und zu den unteren Blöcken verfolgt (und mit anderen Blöcken zu einer Kette verbunden). Danach wird die XOR-Operation mit Eingangsdaten (SI-Daten) auf das MSB angewendet und liefert ein Rückkopplungssignal (Rückkopplung, FB). Danach wird das Rückkopplungssignal zu den unteren Blöcken verfolgt (und in einer Kette mit anderen Blöcken verbunden). Dieser Rückkopplungswert wird für alle Blöcke verwendet, um die

XOR- Operation des Polynoms (aus dem Register Data0 oder Data1) mit dem aktuellen Batteriewert durchzuführen.

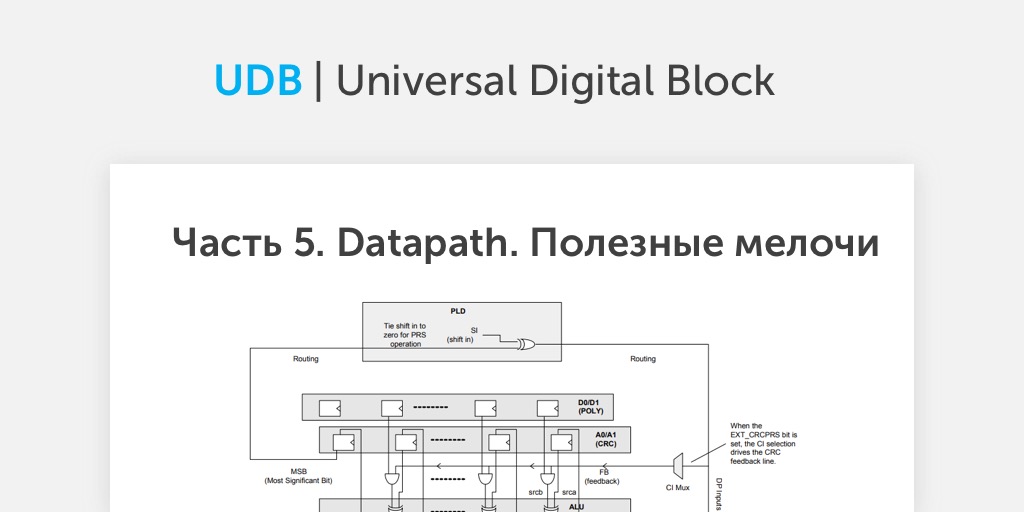

Abbildung 21-18 zeigt die strukturelle Konfiguration der CRC-Operation. Die PRS-Konfiguration ist identisch, aber der Verschiebungseingang (SI) wird auf 0 gezogen. Im PRS-Modus enthält D0 oder D1 den Polynomwert und A0 oder A1 den Anfangswert (Startwert) und den nach der Berechnung erhaltenen CRC-Wert.

Hinweis des Übersetzers.Anscheinend gibt es in der proprietären Dokumentation in diesem Satz einen Tippfehler, da im PRS-Modus eine Zufallszahl erhalten werden sollte. Informationen zu CRC finden Sie direkt darunter. Abbildung 21-18. Funktionsstruktur von CRC.

Abbildung 21-18. Funktionsstruktur von CRC.Um die CRC-Unterstützung zu aktivieren, müssen Sie das Bit

CFB_EN im RAM der dynamischen Konfiguration auf 1 setzen. Dadurch wird die

UND- Verknüpfung in Bezug auf den SRCB-ALU-Eingang und das CRC-Rückkopplungssignal aktiviert. Wenn dieses Bit auf Null gesetzt ist, wird das Rückkopplungssignal Eins zugewiesen, wodurch normale arithmetische Operationen ausgeführt werden können. Durch die dynamische Steuerung dieses Bits in jedem Zyklus können Sie CRC / PRS-Operationen mit anderen arithmetischen Operationen abwechseln.

Verkettung von CRC / PRS

Abbildung 21-19 zeigt ein Beispiel für die Bindung von CRC / PRS in Ketten zwischen drei UDBs. Dieses Szenario unterstützt den Betrieb in Modi mit einer Auflösung von 17 bis 24 Bit. Die Steuerbindungsbits in den Ketten werden entsprechend der Position des Datenpfads in der Kette gesetzt (siehe Abbildung).

Abbildung 21-19. Kettenbindung von CRC / PRS.

Abbildung 21-19. Kettenbindung von CRC / PRS.Wie das CRC / PRS-Rückkopplungssignal (cfbo, cfbi) in einer Kette verbunden ist:

- Wenn der ausgewählte Block der jüngste ist, wird das Rückkopplungssignal auf diesem Block aus der eingebauten Logik erzeugt, die den Verschiebungseingang nach rechts nimmt (Sir) und eine XOR- Operation mit dem höchstwertigen Bit an ihnen ausführt. (Bei PRS wird das Signal "sir" auf "0" gesetzt).

- Wenn der ausgewählte Block kein Block niedriger Ordnung ist, muss das Konfigurationsbit CHAIN FB gespannt werden, und die Rückmeldung wird in einer Kette vom vorherigen Block übertragen.

Wie funktioniert die CRC / PRS-MSB-Signalkette (cmsbo, cmsbi):

- Wenn der ausgewählte Block hoch ist, wird das MSB-Konfigurationsbit (gemäß dem ausgewählten Polynom) unter Verwendung der MSB_SEL- Konfigurationsbits konfiguriert.

- Wenn der ausgewählte Block nicht hoch ist, muss das CHAIN MSB- Konfigurationsbit gespannt werden, und das MSB-Signal wird vom nächsten Block entlang der Kette gesendet.

Polynomspezifikation CRC / PRS

Betrachten Sie als Beispiel für die Konfiguration des Polynoms zum Schreiben in das entsprechende Register D0 / D1 das

CCITT CRC-16- Polynom mit der Form x

16 + x

12 + x

5 + 1. Das Verfahren zum Extrahieren des Datenformats aus dem Polynom ist in Abbildung 21-20 dargestellt. Der Begriff X0 ist per Definition immer 1, daher muss er nicht geschrieben werden. Für alle anderen Elemente des Polynoms wird die Einheit auf die erforderlichen Positionen eingestellt, wie in der Abbildung gezeigt.

Abbildung 21-20. Das Format des CCITT CRC16-Polynoms.

Abbildung 21-20. Das Format des CCITT CRC16-Polynoms.Bitte beachten Sie, dass sich das Format des Polynoms geringfügig von dem im klassischen Hexadezimalformat angegebenen Format unterscheidet. Beispielsweise wird das

CCITT- Polynom

CRC16 üblicherweise als

1021H bezeichnet . Um es in das für Datapath erforderliche Format zu konvertieren, müssen Sie eine Rechtsverschiebung um eine Position durchführen und dem MSB-Bit 1 hinzufügen. In diesem Fall ist der korrekte Polynomwert, der in D0 oder in D1 geschrieben werden soll,

8810H .

Beispiel für eine CRC / PRS-Konfiguration

Das Folgende ist eine kurze Beschreibung der CRC / PRS-Konfigurationsanforderungen, vorausgesetzt, D0 ist ein Polynom und CRC / PRS wird in A0 berechnet:

- Wählen Sie ein geeignetes Polynom (Beispiel oben) und schreiben Sie es in D0.

- Wählen Sie den entsprechenden Startwert aus (z. B. alle Nullen für CRC oder alle Einsen für PRS) und schreiben Sie ihn in A0.

- Konfigurieren Sie gegebenenfalls die Verkettung wie oben beschrieben.

- Wählen Sie ein MSB-Element wie oben beschrieben aus.

- Konfigurieren Sie dynamische RAM-RAM-Felder:

a. Wählen Sie D0 als ALU “SRCB” (ALU B Datenquelle)

b. Wählen Sie A0 als ALU „SRCA“ (ALU A-Datenquelle).

c. Wählen Sie

XOR für den ALU-Betrieb

d. Wählen Sie

SHIFT LEFT für den SHIFT-Betrieb

e. Wählen Sie

CFB_EN , um die CRC / PRS-Unterstützung zu aktivieren.

f. Wählen Sie ALU als Aufnahmequelle A0

Wenn Sie CRC auswählen, müssen Sie die

Verschiebung im rechten Feld für die Eingabedaten konfigurieren und bei jedem Schritt Daten zu dieser Eingabe senden. Bei Auswahl von PRS müssen Sie die

Verschiebung nach rechts auf 0 setzen.

Diese Konfiguration von UDB erzeugt die erforderliche CRC oder erzeugt das höchstwertige Bit, das nach außen weitergeleitet werden kann, wobei eine pseudozufällige Sequenz daraus entfernt wird.

Externer Modus CRC / PRS

Um die externe CRC- oder PRS-Berechnung zu aktivieren, können Sie ein statisches Konfigurationsbit (

EXT CRCPRS )

angeben . Wie in Abbildung 21-21 dargestellt, wird die CRC-Rückkopplungsberechnung im PLD-Block durchgeführt. Wenn das Bit gespannt ist, wird das CRC-Rückkopplungssignal direkt vom Eingangsmultiplexer CI (Carry In) übertragen, wobei interne Berechnungen umgangen werden. Die Abbildung zeigt eine einfache Konfiguration, die CRC oder PRS bis zu 8 Bit unterstützt. Normalerweise werden eingebaute elektronische Schaltungen verwendet. Mit diesem Parameter können Sie jedoch komplexere Konfigurationen implementieren, z. B. 16-Bit-CRC / PRS-Funktionen in einer UDB mithilfe von Zeitmultiplex.

Abbildung 21-21. Externer Modus CRC / PRS.

Abbildung 21-21. Externer Modus CRC / PRS.In diesem Modus steuert das

CFB_EN- Bit des dynamischen Konfigurations-RAM auch, ob die

UND- Verknüpfung für das CRC-Rückkopplungssignal am CRCB-ALU-Eingang verwendet wird oder nicht. Somit kann diese Funktion wie im Fall des internen CRC / PRS-Modus bei Bedarf mit anderen Funktionen abwechseln.

21.3.2.7 Datenpfadausgänge und Multiplexing

Bedingungen werden aus Batterietriggerwerten, ALU-Ausgängen und dem FIFO-Status generiert. Diese Bedingungen können über digitale Verfolgungskanäle an andere UDBs übertragen werden, um Interrupt-Anforderungen entweder an den DMA oder an die "Beine des Chips" zu bilden. 16 mögliche Bedingungen sind in der folgenden Tabelle aufgeführt.

Tabelle 21-16. Generierung von Datenpfadbedingungen.

Es gibt sechs Ausgänge von Datapath. Wie in Abbildung 21-22 dargestellt, verfügt jeder Ausgang über einen 16-in-1-Multiplexer, mit dem Sie 16 Signale an einen beliebigen Datenpfadausgang weiterleiten können.

Abbildung 21-22. Verbindungen zum Ausgangsmultiplexer.

Abbildung 21-22. Verbindungen zum Ausgangsmultiplexer.Vergleiche

Es gibt zwei Vergleiche, von denen einer feste Quellen hat (

Vergleiche 0 ) und der andere dynamisch ausgewählt wird (

Vergleiche 1 ). Jeder Vergleich verfügt über ein statisches 8-Bit-Maskierungsregister, das Vergleiche im angegebenen Bitfeld ermöglicht. Standardmäßig ist die Maskierung deaktiviert (alle Bits werden verglichen) und muss manuell aktiviert werden.

Vergleiche 1 Eingänge werden dynamisch konfiguriert. Wie in der folgenden Tabelle gezeigt, gibt es vier Compare 1-Parameter, die für die Bedingungen "weniger" und "gleich" gelten. Die Konfigurationsbits

CMP SELA und

CMP SELB bestimmen die möglichen Vergleichskonfigurationen. Die RAM-Bits der dynamischen Konfiguration geben in jedem Zyklus eine der Konfigurationen (A oder B) an.

Tabelle 21-17. Vergleichskonfiguration.

Vergleiche 0 und

Vergleiche 1 sind unabhängig voneinander (in der Reihenfolge der Behandlung) mit den im vorherigen Datenpfad generierten Bedingungen verknüpft. In den UDB-Konfigurationsregistern wird statisch angegeben, ob Vergleiche verkettet werden sollen oder nicht. Abbildung 21-23 zeigt die Verknüpfung von "gleich" mit der Vergleichskette, wodurch die

UND- Operation auf den "gleichen" Vergleich dieses Blocks und auf die Eingabe aus dem vorherigen Block angewendet wird.

Abbildung 21-23. Die Verknüpfung mit der Vergleichskette ist "gleich".

Abbildung 21-23. Die Verknüpfung mit der Vergleichskette ist "gleich".Abbildung 21-24 zeigt die Verknüpfung mit der weniger Vergleichskette. In diesem Fall wird das Ausgabeergebnis (cl0) für einen gegebenen Block von der Vergleichsschaltung "kleiner als" erzeugt und ist bedingungslos. Dieses Signal wird

ODER mit dem eingehenden Ergebnis der Kette kombiniert, wenn die Bedingung dem aktuellen Block entspricht und der Verknüpfungsmodus eingeschaltet ist.

Abbildung 21-24. Link weniger als

Abbildung 21-24. Link weniger alsErkennung aller Nullen und aller Einsen

Jede Batterie hat einen Detektor aller Nullen und einen Detektor aller Einheiten. Diese Bedingungen können statisch verkettet werden, wie in den UDB-Konfigurationsregistern angegeben. Der Bindungsmodus wird in den UDB-Konfigurationsregistern eingestellt. Die Verknüpfung in der Erkennungskette von Nullen erfolgt nach dem gleichen Konzept wie der Vergleich "gleich". Wenn die Verkettung aktiviert ist, wird die

UND- Verknüpfung auf erfolgreich verknüpfte Daten angewendet.

Überlauf

Ein Überlauf ist definiert als eine

XOR- Übertragungsoperation in einem MSB und eine Übertragung von einem MSB. Berechnungen werden mit dem aktuellen MSB durchgeführt, wie in den

MSB_SEL- Bits angegeben. Diese Bedingung kann nicht verkettet werden. Die Berechnung ist jedoch korrekt, wenn die Gesamtkapazitätsfunktion auf dem höheren Datenpfad ausgeführt wird, bis die Übertragung zwischen den Blöcken verbunden ist.

21.3.2.8 Datenpfad für parallele Ein- und Ausgänge

Wie in Abbildung 21-25 dargestellt, bieten die Signale

Parallel In (PI) und

Parallel Out (PO) eine eingeschränkte Möglichkeit, Daten bereitzustellen und Ressourcen an Datapath zu verfolgen und Daten von diesem auszugeben. PO-Signale stehen immer zur Verfolgung als Wahl von ALU asrc zwischen A0 und A1 zur Verfügung.

Hinweis des Übersetzers.Dies ist ein äußerst wichtiger Mechanismus, mit dem UDB nicht nur mit seriellen, sondern auch mit parallelen Daten arbeiten kann. Aus irgendeinem Grund wird dies in diesem Dokument nicht hervorgehoben, aber Sie können es nebenbei in einem der Anwendungshinweise lesen. Abbildung 21-25. Parallele In / Out-Datenpfadsignale.

Abbildung 21-25. Parallele In / Out-Datenpfadsignale.Um Daten in die ALU einzugeben, müssen Sie

Parallel In auswählen. Es gibt zwei Modi: statisch und dynamisch. Im statischen Modus

konvertiert das

PI SEL- Bit

den asrc- ALU-

Wert in PI. Das

PI DYN- Bit wird verwendet, um den dynamischen PI-Modus bereitzustellen. Wenn es gespannt ist und auch vorausgesetzt, dass

PI SEL 0 ist, kann der PI-Multiplexer das dynamische

Steuerbit CFB_EN steuern . Die Hauptfunktion des

CFB_EN- Bits besteht darin, PRS / CRC-Funktionalität bereitzustellen.

21.3.2.9 Verketten des Datenpfads

Jeder Datenpfadblock verfügt über eine 8-Bit-ALU, mit der Bindestriche, Verschiebungen, Erfassungsauslöser und bedingte Signale an den nächstgelegenen benachbarten Datenpfad gekettet werden können, um arithmetische Funktionen und Verschiebungsregister mit höheren Bittiefen zu erstellen. Diese in Ketten geschalteten Signale sind isoliert und ermöglichen es Ihnen, 16-24- und 32-Bit-Funktionen in einem einzigen Zyklus effektiv zu implementieren, ohne Rennen und andere Probleme aufgrund von Verzögerungen in den Trace-Kanälen. Darüber hinaus unterstützen Verkettungsgriffe das atomare Ablesen von Batterien in verbundenen Blöcken. Wie in Abbildung 21-21 dargestellt, sind alle generierten Bedingungs- und Erfassungssignale in einer Kette verbunden, die sich vom jüngsten zum ältesten Block bewegt. Eine Verschiebung nach links wird ebenfalls von Junior zu Senior durchgeführt. Eine Verschiebung nach rechts wird vom ältesten zum jüngsten durchgeführt. Das CRC / PRS-Verkettungssignal für die Rückkopplung wird von hoch nach niedrig geleitet, und der MSB-Ausgang wird von hoch nach niedrig gesendet.

Abbildung 21-26. Datenpfad-Einfädelkette.

Abbildung 21-26. Datenpfad-Einfädelkette.21.3.2.10 Dynamische RAM-Konfiguration

Jeder Datenpfad enthält einen dynamischen Konfigurations-RAM mit 8 Wörtern zu je 16 Bit (siehe Abbildung 21-27). Der Zweck eines solchen RAM besteht darin, die Bits der Datenpfadkonfiguration in jedem Zyklus basierend auf dem für diesen Datenpfad ausgewählten Takt zu steuern. Der RAM verfügt über synchrone Lese- und Schreibports zum Herunterladen von Konfigurationen über den Systembus.

Um diese 16-Bit-Wörter schnell an Datapath auszugeben, wird ein zusätzlicher asynchroner Leseport als Steuerbit bereitgestellt. Asynchrone Adresseneingänge werden von Multiplexern aus Datenpfadeingängen ausgewählt, die aus beliebigen Signalen entnommen werden können, einschließlich Mikroschaltungszweigen, PLD-Ausgängen, Steuereinheitsausgängen oder beliebigen Datenpfadausgängen.

Der Hauptzweck eines asynchronen Leseports besteht darin, eine schnelle Decodierung von Datenpfad-Steuerbits in einem einzigen Zyklus bereitzustellen.

Abbildung 21-27. RAM-E / A-Konfiguration.

Abbildung 21-27. RAM-E / A-Konfiguration.Die Felder des RAM-Wortes der dynamischen Konfiguration werden in den folgenden Tabellen zusammen mit einer Beschreibung der Verwendung jedes Felds gezeigt.

Tabelle 21-18. Dynamische Konfigurationsreferenz.

(a. - Für die CI-, SI- und CMP-Felder können Sie in den RAM-Feldern eine von zwei vordefinierten Optionen auswählen. Siehe Konfiguration des statischen Registers.)

Fortsetzung folgt…