Wir werden weiterhin in Betracht ziehen, Interrupts von externen Geräten im x86-System zu konfigurieren.

In Teil 1 (Die

Entwicklung von Interrupt-Controllern ) haben wir die theoretischen Grundlagen von Interrupt-Controllern und allgemeine Begriffe untersucht. In Teil 2 (

Linux-Kernel-Boot-Optionen ) haben wir untersucht, wie das Betriebssystem in der Praxis zwischen Controllern wählt. In diesem Teil werden wir uns ansehen, wie das BIOS das IRQ-Routing für Interrupt-Controller im Chipsatz konfiguriert.

Keine modernen BIOS-Entwicklungsunternehmen (AwardBIOS / AMIBIOS / Insyde) legen den Quellcode ihrer Programme offen. Aber zum Glück gibt es

Coreboot , ein Projekt, das das proprietäre BIOS durch freie Software ersetzt. In seinem Code werden wir sehen, wie das Interrupt-Routing im Chipsatz konfiguriert ist.

Theorie

Erfrischen und ergänzen Sie zunächst unser theoretisches Wissen. In

Teil 1 haben wir einen gemeinsamen Interrupt-Pfad für den Fall von PIC und APIC identifiziert.

Bild: APIC:

APIC:

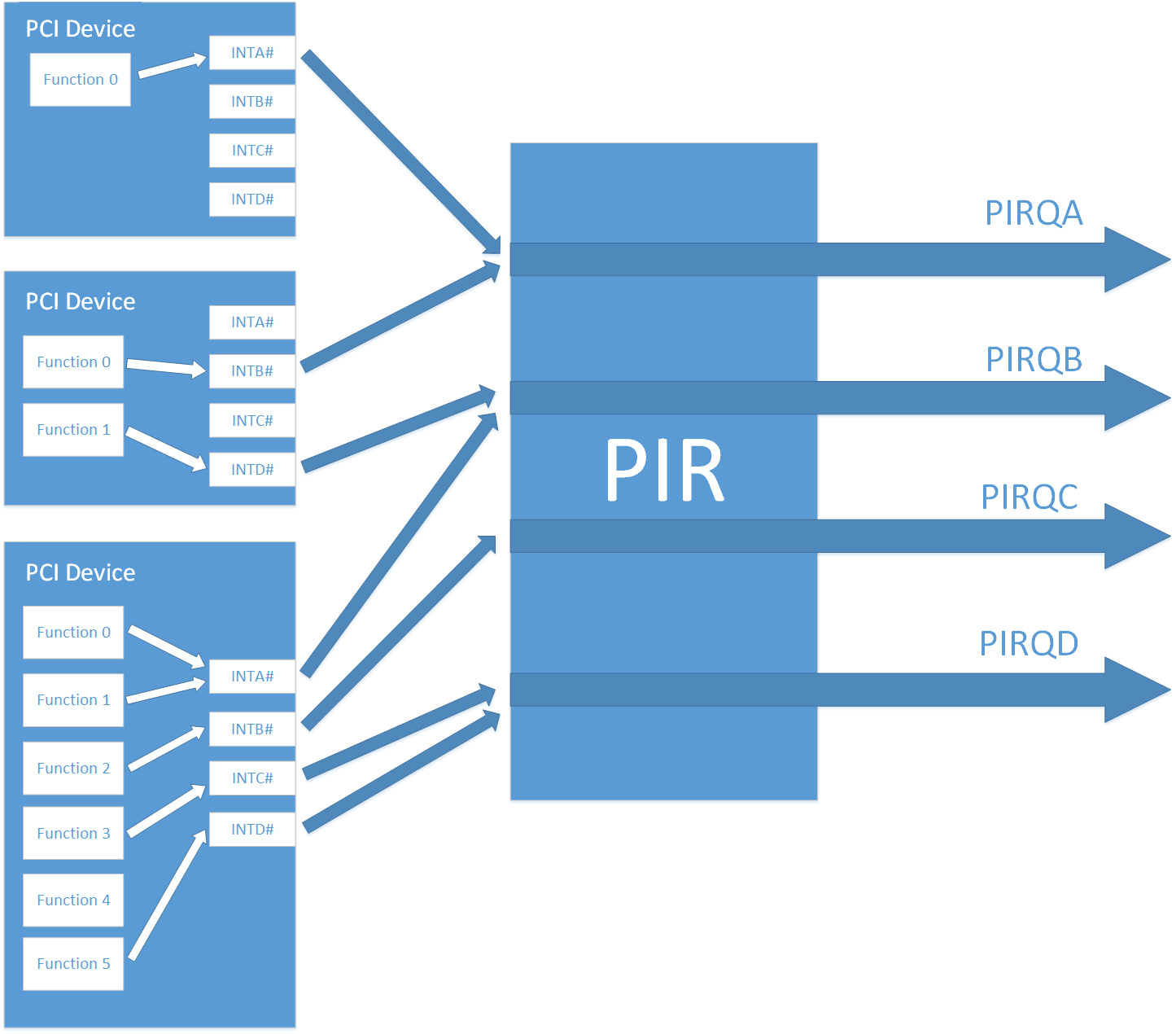

In diesen Figuren ist das PCI-Gerät → PIR-Mapping abstrakt dargestellt, tatsächlich ist es etwas komplizierter. In Wirklichkeit hat jedes PCI-Gerät 4 Interrupt-Leitungen (INTA #, INTB #, INTC #, INTD #). Jedes PCI-Gerät kann bis zu 8 Funktionen haben und jede Funktion hat bereits einen INTx # Interrupt. Welche Zeile von INTx # jede Funktion des Geräts abruft, ist entweder in der Hardware festgelegt oder wird durch die Konfiguration des Geräts bestimmt.

Funktionen sind im Wesentlichen separate logische Blöcke. Beispielsweise kann in einem PCI-Gerät eine Smbus-Controller-Funktion, eine SATA-Controller-Funktion oder eine LPC-Bridge-Funktion vorhanden sein. Auf der Betriebssystemseite ist jede Funktion ein separates Gerät mit einem eigenen Konfigurationsbereich für die PCI-Konfiguration.

Im einfachsten (und häufigsten) Fall eines PCI-Geräts gibt es nur eine Funktion, deren Interrupt über die INTA # -Leitung erfolgt. Im Allgemeinen verfügt das Gerät jedoch möglicherweise sogar über mehr als 4 Funktionen (wie bereits erwähnt, 8). Einige davon müssen dann auf einer INTx # -Leitung platziert werden (PCI-Interrupts können die Leitung gemeinsam nutzen). Außerdem kann bei PCI-Geräten, die im Chipsatz enthalten sind, durch Schreiben in spezielle Register häufig angegeben werden, welche Funktionen welche INTx # -Leitungen verwenden (und ob sie überhaupt verwendet werden).

Wir systematisieren unser Wissen und bezeichnen den Pfad (Routing) von Unterbrechungen von jeder PCI-Funktion über INTx # → PIRQy → IRQz, wobei:

- INTx # - Zeile INT # (INTA #, INTB #, INTC #, INTD #) des PCI-Geräts, das die Funktion verwenden wird

- PIRQy - die PIRQ-Leitung (PIRQA, PIRQB, ...) von der PIR, mit der die INTx # -Leitung verbunden ist

- IRQz - IRQ-Leitung (0, 1, 2, ...) am Interrupt-Controller (APIC / PIC), der mit der PIRQy-Leitung verbunden ist

Warum können Sie nicht einfach überall eine Verbindung herstellen? INTA # → PIRQA, INTB # → PIRQB, ...?

Warum überhaupt Routing einrichten? Angenommen, wir möchten nicht alle Interrupt-Leitungen von allen PCI-Geräten auf die gleichen PIRQ-Leitungen übertragen. Sagen wir Folgendes:

- INTA # → PIRQA

- INTB # → PIRQB

- INTC # → PIRQC

- INTD # → PIRQD

Wie oben erwähnt, ist der häufigste Fall, wenn ein PCI-Gerät eine Funktion hat und seine Unterbrechung mit der INTA # -Leitung verbunden ist (warum sollte der Geräteentwickler es anders starten?). Wenn wir uns also plötzlich dazu entschließen, alle Zeilen so zu starten, wie wir sie geschrieben haben, werden fast alle Interrupts von Geräten in PIRQA-Zeilen unterteilt. Nehmen wir an, sie ist auf IRQ16 gelandet. Jedes Mal, wenn der Prozessor darüber informiert wird, dass ein Interrupt auf der IRQ16-Leitung aufgetreten ist, muss er die Treiber aller an die IRQ16-Leitung (PIRQA) angeschlossenen Geräte abfragen, ob sie einen Interrupt dafür haben. Wenn es viele solcher Geräte gibt, beschleunigt dies natürlich nicht die Systemreaktion auf Unterbrechungen. Und die PIRQB-PIRQD-Leitungen sind in diesem Fall größtenteils inaktiv. Zur Verdeutlichung die Abbildung, die das Problem veranschaulicht:

Aber alles könnte so gemacht werden:

Das Bild ist etwas verwirrend, aber der Punkt ist, dass wir einfach die INTx # -Linien mit PIRQy mit Round-Robin verbinden (PIRQA, PIRQB, PIRQC, PIRQD, PIRQA, PIRQB, PIRQC, PIRQD, PIRQA, PIRQB, PIRQC, PIRQD). ..)

Es ist zu beachten, dass hier nicht nur berücksichtigt werden muss, dass auf jeder PIRQ-Leitung die gleiche Anzahl von PCI-Funktionen geladen ist. Schließlich können einige Funktionen sehr selten und einige dauerhaft Interrupts erzeugen (z. B. Ethernet-Controller). In diesem Fall kann sogar die Zuweisung einer separaten PIRQ-Leitung für Interrupts mit einer solchen Funktion durchaus gerechtfertigt sein.

Auf der Grundlage des Vorstehenden hat der BIOS-Entwickler unter anderem die Aufgabe sicherzustellen, dass die PIRQ-Leitungen gleichmäßig mit Interrupts geladen werden.

Was soll das BIOS überhaupt tun?

Wir systematisieren in der Abbildung:

- 1) Geben Sie an, welche INTx # -Zeile jede Funktion von PCI-Geräten abruft

Bei externen PCI-Geräten wird dieser Punkt nicht ausgeführt, bei den im Chipsatz enthaltenen Funktionen von PCI-Geräten jedoch möglicherweise. - 2) Konfigurieren Sie die INTx # → PIRQy-Zuordnung für jedes PCI-Gerät

Es ist erwähnenswert, dass es mehr als vier Standard-PIRQy-Signale geben kann (PIRQA, PIRQB, PIRQC, PIRQD). Zum Beispiel 8: PIRQA-PIRQH.

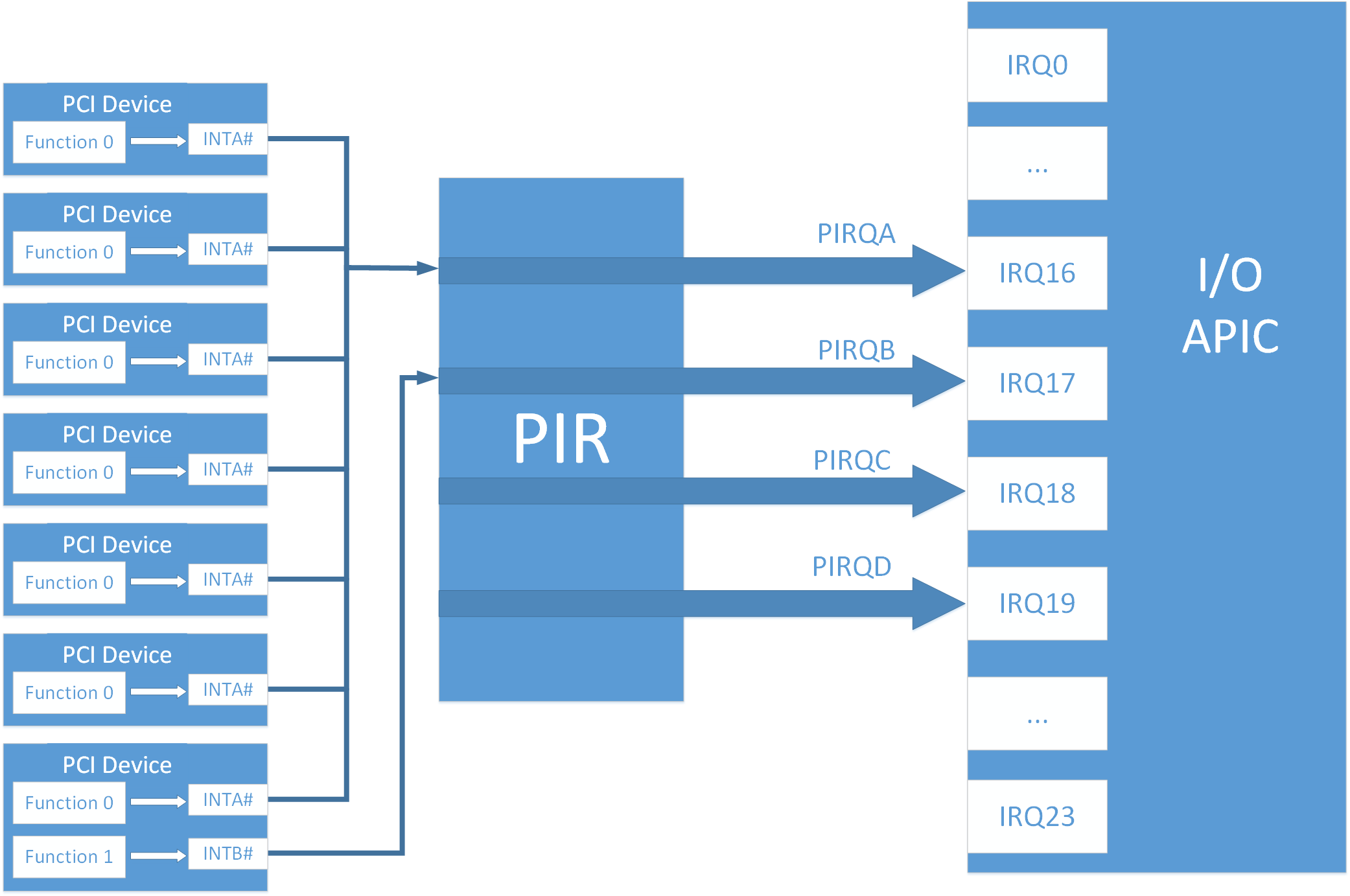

PIRQy-Signale gehen auf die IRQz-Leitung des ausgewählten Interrupt-Controllers (APIC / PIC). Da wir alle möglichen Lademethoden unterstützen möchten (siehe

Teil 2 ), müssen wir beide Zuordnungen ausfüllen:

- 3a) Füllen Sie das Mapping PIRQy → IRQz1 für die Kommunikation PIR → I / O APIC aus

In der Regel ist dies jedoch nicht erforderlich, da die PIRQy-Leitungen auf der APIC-Leitung festgelegt sind. Die übliche Lösung ist PIRQA → IRQ16, PIRQB → IRQ17, ... Die einfachste Lösung, weil Wenn Sie PIRQy-Leitungen auf Controller-Leitungen ≥ 16 platzieren, müssen Sie sich keine Gedanken über Konflikte mit untrennbaren Interrupts von ISA-Geräten machen. - 3b) Füllen Sie das Mapping PIRQy → IRQz2 für die Kommunikation PIR → PIC

Dies muss angegeben werden, wenn wir das Routing über den PIC-Controller verwenden. Es gibt keine so eindeutige Lösung wie im Fall von APIC, da im Fall von PIC die Möglichkeit von Konflikten mit untrennbaren Interrupts von ISA-Geräten bekannt sein sollte.

Der letzte vierte Punkt ist erforderlich, um das Betriebssystem bei der Bestimmung des Interrupt-Routings zu unterstützen. Das Gerät selbst verwendet diese Register normalerweise nicht.

- 4) Füllen Sie die Interrupt Line / Interrupt Pin-Register für jede PCI-Funktion aus

Im Allgemeinen wird das Interrupt-Pin-Register automatisch ausgefüllt und ist normalerweise schreibgeschützt. Daher muss beim Ausfüllen höchstwahrscheinlich nur das Interrupt-Line-Register ausgefüllt werden. Dies muss bereitgestellt werden, wenn wir das Routing über den PIC-Controller verwenden, ohne dem Betriebssystem eine Tabelle zu Routing-Interrupts zur Verfügung zu stellen (siehe erneut Teil 2 ). Wenn Tabellen bereitgestellt werden und diese Zuordnung mit Routing-Tabellen ($ PIR / ACPI) übereinstimmt, verlässt das Betriebssystem diese häufig.

Es ist zu beachten, dass wir die Tabellen $ PIR / MPtable / ACPI noch nicht berühren und überlegen, wie die Chipsatzregister in Bezug auf Routing-Interrupts konfiguriert werden, bevor die Steuerung an den Systemloader übertragen wird. Interrupt-Tabellen sind ein Thema für einen separaten Artikel (möglicherweise einen zukünftigen).

Also werden die theoretischen Grundlagen studiert, endlich fangen wir an zu üben!

Übe

Als Beispiel für Artikel in dieser Serie verwende ich ein benutzerdefiniertes Board mit einem Intel Haswell i7-Prozessor und einem LynxPoint-LP-Chipsatz. Auf diesem Board habe ich Coreboot in Verbindung mit SeaBIOS gestartet. Coreboot bietet eine hardwarespezifische Initialisierung, und die SeaBIOS-Nutzdaten bieten eine BIOS-Schnittstelle für Betriebssysteme. In diesem Artikel werde ich nicht den Prozess der Konfiguration von Coreboot beschreiben, sondern nur anhand eines Beispiels zeigen, welche BIOS-Einstellungen im Chipsatz vorgenommen werden sollten, um IRQ-Interrupts von externen Geräten weiterzuleiten.

Da sich das Coreboot-Projekt aktiv entwickelt, sodass der Artikel immer auf dem neuesten Stand ist, werden wir den Code am Beispiel der neuesten festen Version

4.9 (Release 2018-12-20) betrachten.

Das Motherboard, das meinem am nächsten kommt, ist Google Beltino mit Panther-Variante. Der

Hauptordner für dieses Motherboard ist der Ordner

"src \ mainboard \ google \ bearino" . Alle Einstellungen sind hier und der für diese Karte spezifische Code konzentriert.

Beginnen wir also damit, herauszufinden, wo die oben genannten Elemente konfiguriert sind:

1) Geben Sie an, welche INTx # -Zeile jede Funktion von PCI-Geräten abruft

Diese Informationen werden in der Datei

„src / mainboard / google / bearino / romstage.c“ in der Struktur rcba_config über die DxxIP-Register (Device xx Interrupt Pin Register (IP)) definiert. Dieses Register zeigt an, welcher Pin INTx # (A / B / C / D) jede der Gerätefunktionen einen Interrupt ausgibt.

Mögliche Optionen (siehe Datei

"src / southbridge / intel / lynxpoint / pch.h" ):

0h = No interrupt 1h = INTA# 2h = INTB# 3h = INTC# 4h = INTD#

Es wird angenommen, dass mehrere Funktionen denselben Pin verwenden.

Es wird angenommen, dass Funktionen den Pin möglicherweise nicht für Unterbrechungen verwenden (keine Unterbrechung).

Alles, wie wir in der Abbildung am Anfang des Artikels gesehen haben.

Der vollständige Code ist für den von uns bezeichneten Artikel verantwortlich:

RCBA_SET_REG_32(D31IP, (INTC << D31IP_TTIP) | (NOINT << D31IP_SIP2) | (INTB << D31IP_SMIP) | (INTA << D31IP_SIP)), RCBA_SET_REG_32(D29IP, (INTA << D29IP_E1P)), RCBA_SET_REG_32(D28IP, (INTA << D28IP_P1IP) | (INTC << D28IP_P3IP) | (INTB << D28IP_P4IP)), RCBA_SET_REG_32(D27IP, (INTA << D27IP_ZIP)), RCBA_SET_REG_32(D26IP, (INTA << D26IP_E2P)), RCBA_SET_REG_32(D22IP, (NOINT << D22IP_MEI1IP)), RCBA_SET_REG_32(D20IP, (INTA << D20IP_XHCI)),

Betrachten Sie zum besseren Verständnis einige Beispiele:

Beispiel 1:Das Gerät 0x1d (29 in Dezimalzahl) hat eine Funktion (EHCI-Controller).

Weisen Sie in diesem Fall INTA # einen Interrupt zu.

00: 1d.0 - INTA #

RCBA_SET_REG_32(D29IP, (INTA << D29IP_E1P)),

Beispiel 2:Das Gerät 0x1f (31 in Dezimalzahl) hat die Funktionen Thermosensor-Controller (00: 1f.6), SATA-Controller 2 (00: 1f.2), SMBus-Controller (00: 1f.3), SATA-Controller 1 (00: 1f) .2). Wir möchten nur den SMBus-Controller, den SATA-Controller 1 und den Thermosensor-Controller verwenden.

00: 1f.2 - INTA # (SATA-Controller 1)

00: 1f.3 - INTB # (SMBus-Controller)

00: 1f.2 - Kein Interrupt (SATA-Controller 2 wird nicht verwendet)

00: 1f.6 - INTC # (Thermosensorregler)

Für diese Konfiguration sollten Sie schreiben:

RCBA_SET_REG_32(D31IP, (INTC << D31IP_TTIP) | (NOINT << D31IP_SIP2) | (INTB << D31IP_SMIP) | (INTA << D31IP_SIP)),

Beispiel 3:In einem Gerät sind mehr als 4 Funktionen erforderlich. Im 0x1c-Gerät ist jede Funktion für den PCI Express-Port verantwortlich. Damit die Ports 0-5 funktionieren und Interrupts gleichmäßig auf die Leitungen verteilt werden, können Sie Folgendes konfigurieren:

00: 1c.0 - INTA # (PCI Express Port 0)

00.1c.1 - INTB # (PCI Express Port 1)

00.1c.2 - INTC # (PCI Express Port 2)

00.1c.3 - INTD # (PCI Express Port 3)

00.1c.4 - INTA # (PCI Express Port 4)

00.1c.5 - INTB # (PCI Express Port 5)

00.1c.6 - Kein Interrupt (Port nicht verwendet)

00.1c.7 - Kein Interrupt (Port nicht verwendet)

RCBA_SET_REG_32(D28IP, (INTA << D28IP_P1IP) | (INTB << D28IP_P2IP) | (INTC << D28IP_P3IP) | (INTD << D28IP_P4IP) | (INTA << D28IP_P5IP) | (INTB << D28IP_P6IP) | (NOINT << D28IP_P7IP) | (NOINT << D28IP_P8IP)),

2) Konfigurieren Sie die INTx # → PIRQy-Zuordnung für jedes PCI-Gerät

Diese Informationen sind auch in der Datei

"src \ mainboard \ google \ bearino \ romstage.c" definiert.in der Struktur rcba_config, jedoch bereits über die Register DxxIR (Device xx Interrupt Route Register).

Die Informationen in diesem Register zeigen, mit welcher PIRQx-Leitung (A / B / C / D / E / F / G / H) jede INTx # -Unterbrechungsleitung verbunden ist.

RCBA_SET_REG_32(D31IR, DIR_ROUTE(PIRQG, PIRQC, PIRQB, PIRQA)), RCBA_SET_REG_32(D29IR, DIR_ROUTE(PIRQD, PIRQD, PIRQD, PIRQD)), RCBA_SET_REG_32(D28IR, DIR_ROUTE(PIRQA, PIRQB, PIRQC, PIRQD)), RCBA_SET_REG_32(D27IR, DIR_ROUTE(PIRQG, PIRQG, PIRQG, PIRQG)), RCBA_SET_REG_32(D22IR, DIR_ROUTE(PIRQA, PIRQA, PIRQA, PIRQA)), RCBA_SET_REG_32(D21IR, DIR_ROUTE(PIRQE, PIRQF, PIRQF, PIRQF)), RCBA_SET_REG_32(D20IR, DIR_ROUTE(PIRQC, PIRQC, PIRQC, PIRQC)), RCBA_SET_REG_32(D23IR, DIR_ROUTE(PIRQH, PIRQH, PIRQH, PIRQH)),

Beispiel 1:Das 0x1c-Gerät (28 im Dezimalsystem) sind die PCIe-Ports, wie wir bereits herausgefunden haben.

Wir stellen eine "direkte" Verbindung her:

- INTA # → PIRQA

- INTB # → PIRQB

- INTC # → PIRQC

- INTD # → PIRQD

RCBA_SET_REG_32(D28IR, DIR_ROUTE(PIRQA, PIRQB, PIRQC, PIRQD))

Beispiel 2:Gerät 0x1d (29 in Dezimalzahl) - Eine Funktion (EHCI-Controller) auf INTA #, andere Zeilen werden nicht verwendet.

Verbinden Sie die INTA # -Leitung mit PIRQD:

RCBA_SET_REG_32(D29IR, DIR_ROUTE(PIRQD, PIRQD, PIRQD, PIRQD))

In diesem Fall ist nur der erste PIRQD-Datensatz (für INTA #) sinnvoll, der Rest macht keinen Sinn.

3a) Füllen Sie das Mapping PIRQy → IRQz1 (PIR → APIC) aus.

Wie bereits erwähnt, wird die Zuordnung hier häufig behoben, und dieser Fall ist keine Ausnahme.

- PIRQA → IRQ16

- PIRQB → IRQ17

- ...

- PIRQH → IRQ23

3b) Füllen Sie das Mapping PIRQy → IRQz2 (PIR → PIC) aus.

In coreboot wird der Inhalt zum Füllen dieser Register in der Datei

devicetree.cb im Motherboard-Ordner "src \ mainboard \ google \ bearino \" definiert.

devicetree.cb (der Name devicetree für die Kommunikation mit einem ähnlichen Konzept im Linux-Kernel und "cb" steht für coreboot) ist eine spezielle Datei, die die Konfiguration dieses Motherboards widerspiegelt: Welcher Prozessor, welcher Chipsatz werden verwendet, welche Geräte sind in welchen enthalten? aus usw. Darüber hinaus können in dieser Datei spezielle Informationen zur Konfiguration des Chipsatzes angegeben werden. Dies ist genau der Fall, den wir brauchen:

register "pirqa_routing" = "0x8b" register "pirqb_routing" = "0x8a" register "pirqc_routing" = "0x8b" register "pirqd_routing" = "0x8b" register "pirqe_routing" = "0x80" register "pirqf_routing" = "0x80" register "pirqg_routing" = "0x80" register "pirqh_routing" = "0x80"

Diese Zeilen geben die Zuordnung PIRQy → IRQz2 an. Im Code werden sie nach dem Parsen der Datei devicetree.cb in die Variablen "config-> pirqX_routing" umgewandelt.

Die Variable "config-> pirqa_routing = 0x8b" bedeutet, dass die PIRQA mit der IRIC11-Interrupt-Leitung (0x0b = 11) des PIC-Controllers verbunden ist. Das höhere Bit (0x80) bedeutet jedoch, dass kein Interrupt-Routing durchgeführt wird. Meiner Erfahrung nach ist dies ein Fehler. Standardmäßig lohnt es sich, das PIC-Routing zu aktivieren. Das Betriebssystem selbst kann zu E / A-APIC wechseln, indem dieses Bit bei Bedarf auf 1 gesetzt wird.

Das heißt, in diesem Fall wäre es korrekter zu schreiben:

register "pirqa_routing" = "0x0b" register "pirqb_routing" = "0x0a" register "pirqc_routing" = "0x0b" register "pirqd_routing" = "0x0b" register "pirqe_routing" = "0x80"

Wir haben die letzten 4 Interrupts nicht aktiviert, weil Der IRQ0-Interrupt wird immer unter dem System-Timer verwendet und ist eindeutig nicht verfügbar (siehe

Allgemeine Informationen zu IBM-PC-kompatiblen Interrupts ).

Wenn wir uns jedoch Punkt 2) genauer ansehen, werden wir feststellen, dass einige PCI-Geräte die PIRQE-PIRQH-Leitungen verwenden. Wenn Sie sie also nicht angeschlossen lassen, ist dies der richtige Weg, um Geräte zu beschädigen.

Es ist also besser, so etwas zu schreiben:

register "pirqa_routing" = "0x03" register "pirqb_routing" = "0x04" register "pirqc_routing" = "0x05" register "pirqd_routing" = "0x06" register "pirqe_routing" = "0x0a" register "pirqf_routing" = "0x0b" register "pirqg_routing" = "0x0e" register "pirqh_routing" = "0x0f"

Das eigentliche Füllen der entsprechenden Register erfolgt in der Datei

src \ southbridge \ intel \ lynxpoint \ lpc.c in der Funktion pch_pirq_init.

Code-Snippet, das für das Ausfüllen des Registers verantwortlich ist:

config_t *config = dev->chip_info; pci_write_config8(dev, PIRQA_ROUT, config->pirqa_routing); pci_write_config8(dev, PIRQB_ROUT, config->pirqb_routing); pci_write_config8(dev, PIRQC_ROUT, config->pirqc_routing); pci_write_config8(dev, PIRQD_ROUT, config->pirqd_routing); pci_write_config8(dev, PIRQE_ROUT, config->pirqe_routing); pci_write_config8(dev, PIRQF_ROUT, config->pirqf_routing); pci_write_config8(dev, PIRQG_ROUT, config->pirqg_routing); pci_write_config8(dev, PIRQH_ROUT, config->pirqh_routing);

Registeradresskonstanten werden in derselben

pch.h- Datei beschrieben

#define PIRQA_ROUT 0x60 #define PIRQB_ROUT 0x61 #define PIRQC_ROUT 0x62 #define PIRQD_ROUT 0x63 #define PIRQE_ROUT 0x68 #define PIRQF_ROUT 0x69 #define PIRQG_ROUT 0x6A #define PIRQH_ROUT 0x6B

Die Zuordnung von PIRQy → IRQz2 für diesen Chipsatz wird in die PIRQy_ROUT-Register auf das LPC-PCI-Gerät (Adresse 00: 1f.0) geschrieben. Es ist zu beachten, dass häufig nicht alle 15 IRQz2-Leitungen pro PIC verwendet werden dürfen, sondern nur ein Teil (z. B. 3,4,5,6,7,9,10,11,12,14,15). Die Beschreibung dieser Register sollte Informationen darüber enthalten, welche IRQs verfügbar sind, um ihnen Interrupts von PIRQ-Leitungen zuzuweisen. Das von uns oben vorgeschlagene Mapping ist also nur möglich, wenn die Zuordnung von PIRQ auf der Leitung IRQ3, IRQ4, IRQ5, IRQ6, IRQ10, IRQ11, IRQ14, IRQ15 verfügbar ist. Wenn wir uns jedoch den Kommentar vor der Funktion pch_pirq_init genau ansehen, werden wir feststellen, dass es sich um Folgendes handelt:

4) Füllen Sie die Interrupt Line / Interrupt Pin-Register für jede PCI-Funktion aus

Im PCI-Konfigurationsraum (jede PCI hat Funktionen gemäß dem Standard) gibt es 2 Register, die für uns von Interesse sind:

- 3Ch: Interrupt Line - Hier müssen Sie die IRQz2-Nummer (eine Nummer von 0 bis 15) schreiben, die Interrupt-Nummer, die die Funktion bei Verwendung des PIC-Controllers eventuell abruft

- 3Dh: Interrupt Pin - Zeigt an, welche Zeile INTx # (A / B / C / D) die Funktion verwendet

Beginnen wir mit dem letzten. Das Interrupt-Pin-Register wird basierend auf den von uns in Absatz 1 vorgenommenen Chipsatzeinstellungen (DxxIP-Registern) automatisch gefüllt und ist schreibgeschützt.

Sie müssen also nur noch das Interrupt Line-Register mit einem IRQz2-Interrupt für jede PCI-Funktion füllen.

Wenn Sie das Mapping PIRQy → IRQz2 (Punkt 3b) und das Mapping INTx # → PIRQy (Punkt 2) kennen, können Sie das Interrupt Line-Register für jede Funktion einfach ausfüllen und wissen, welchen INTx # Interrupt es verwendet (Punkt 1).

In Coreboot werden die Interrupt Line-Register auch in der

Datei src \ southbridge \ intel \ lynxpoint \ lpc.c in der Funktion pch_pirq_init gefüllt:

for (irq_dev = all_devices; irq_dev; irq_dev = irq_dev->next) { u8 int_pin=0, int_line=0; if (!irq_dev->enabled || irq_dev->path.type != DEVICE_PATH_PCI) continue; int_pin = pci_read_config8(irq_dev, PCI_INTERRUPT_PIN); switch (int_pin) { case 1: int_line = config->pirqa_routing; break; case 2: int_line = config->pirqb_routing; break; case 3: int_line = config->pirqc_routing; break; case 4: int_line = config->pirqd_routing; break; } if (!int_line) continue; pci_write_config8(irq_dev, PCI_INTERRUPT_LINE, int_line); }

Aus irgendeinem Grund impliziert dieser Code, dass die Zuordnung auf jeden Fall INTA # → PIRQA, INTB # → PIRQB, INTC # → PIRQC, INTD # → PIRQD ist. Obwohl wir in der Praxis gesehen haben, dass es anders sein kann (siehe Absatz 2).

Im Allgemeinen "Eric Biederman hat einmal gesagt", und wir haben es überall kopiert:

$ grep "Eric Biederman once said" -r src/ src/southbridge/intel/fsp_bd82x6x/lpc.c: /* Eric Biederman once said we should let the OS do this. src/southbridge/intel/i82801gx/lpc.c: /* Eric Biederman once said we should let the OS do this. src/southbridge/intel/i82801ix/lpc.c: /* Eric Biederman once said we should let the OS do this. src/southbridge/intel/lynxpoint/lpc.c: /* Eric Biederman once said we should let the OS do this. src/southbridge/intel/sch/lpc.c: /* Eric Biederman once said we should let the OS do this.

Im Allgemeinen kümmert sich Coreboot nicht wirklich um die Unterstützung älterer Interrupts. Sie sollten sich also nicht über diesen Fehler wundern. Wenn Sie ein modernes Betriebssystem laden, wird Sie dies nicht stören. Wenn Sie jedoch plötzlich Linux mit den Optionen "acpi = off nolapic" laden müssen, ist dies kaum möglich.

Fazit

Abschließend wiederholen wir die typischen Informationen, die im Chipsatz für das Routing von PCI-Interrupts konfiguriert werden müssen:

- Geben Sie an, welche INTx # -Zeile jede PCI-Funktion zieht

- Konfigurieren Sie die INTx # → PIRQy-Zuordnung für jedes PCI-Gerät

- Füllen Sie die Zuordnung PIRQy → IRQz1 (PIR → APIC) und die Zuordnung PIRQy → IRQz2 (PIR → PIC).

- Füllen Sie für jede PCI-Funktion die Register Interrupt Line / Interrupt Pin des PCI-Konfigurationsbereichs aus.