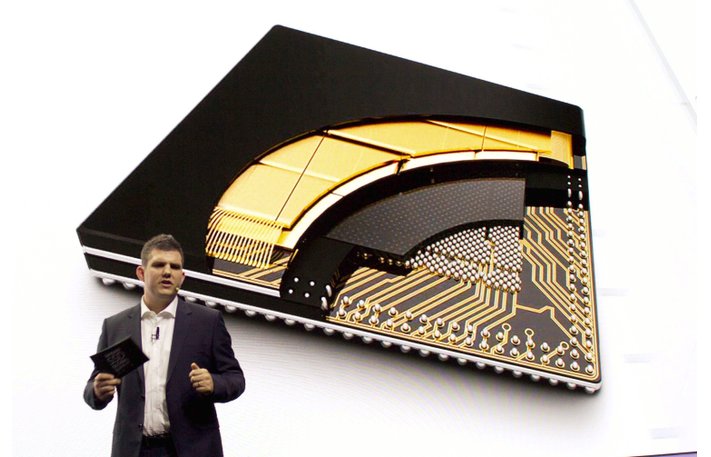

Intel Foveros 3D

Intel Foveros 3DDa das Mooresche Gesetz nicht mehr gilt, müssen Chipdesigner nach anderen Möglichkeiten suchen, um die Leistung zu verbessern. Eine geeignete Technologie hierfür ist das 3D-Chipstapeln. Dies ist eine dreidimensionale Stapelarchitektur von Chips, bei deren Entwicklung Intel führend ist. Vor zwei Monaten stellte Intel die

3D- Architektur von

Foveros vor : eine dreidimensionale Struktur mit einer 10-nm-CPU, einem E / A-Chip und vertikalen elektrischen TSV-Verbindungen (Through Silicon Via) in der Mitte des Chips sowie einem Speicherchip auf dem gesamten Chip.

Auf der HPC-Hochleistungs-Computerkonferenz von Rice Oil and Gas

versicherte AMD

, an einer eigenen Version der 3D-Chip-Architektur zu arbeiten.

Forrest Norrod, Senior Vice President und General Manager, sagte, das Unternehmen entwickle verschiedene Technologien, um die Rendite zu steigern und Probleme zu umgehen, die mit der Beendigung des Moore'schen Gesetzes und den Folgen des Stopps des Wachstums der Transistordichte und der Taktfrequenz verbunden sind. Dies sind unvermeidbare Konsequenzen für Hersteller, die sich der Grenze nähern, wo die Größe des Transistors nur wenige Atome beträgt (die Größe eines Siliziumatoms beträgt 0,2 Nanometer). Das Wachstum der Computerleistung in den letzten Jahren ist nicht so sehr auf eine Erhöhung der Rechengeschwindigkeit zurückzuführen, sondern auf eine Erhöhung der Parallelität.

Wie andere Unternehmen hat AMD eine Beschränkung der Chipfläche von etwa 700 mm² und ist gezwungen, eine 3D-Architektur zu entwickeln. Das Unternehmen verfolgt diesen Ansatz bereits und platziert den HBM2-Speicher neben dem GPU-Substrat, dh im selben Fall wie der Prozessor. In Zukunft plant das Unternehmen jedoch, auf ein fortschrittlicheres 3D-Stapeln umzusteigen.

Laut Norrod arbeitet AMD daran, SRAM und DRAM direkt auf Computerkomponenten (wie Prozessoren und GPUs) zu platzieren, um noch mehr Bandbreite und Leistung bereitzustellen.

Samsung Polaris

Samsung PolarisDieser Ansatz unterscheidet sich von den üblichen PoP-Implementierungen (Package-on-Package), bei denen einfach zwei fertige Gehäuse übereinander gelegt werden, wie Norrod am Beispiel des Samsung Polaris-Chips gezeigt hat. In diesem Beispiel ist das DRAM-Gehäuse über zwei zusätzliche Reihen von BGA-Anschlüssen verbunden, die den Basischip umgeben. Diese BGA-Anschlüsse übertragen Daten zwischen zwei Chips. Wie bei jedem Standarddesign befindet sich die Logik am unteren Rand des Stapels, da mehr Anschlüsse erforderlich sind, die beiden Kristalle jedoch nicht direkt miteinander verbunden sind. Somit bietet der PoP-Ansatz maximale Dichte, dies ist jedoch nicht die schnellste Option.

Beim echten 3D-Stapeln befinden sich zwei Chips (in diesem Fall Speicher und Prozessor) übereinander und sind durch vertikale TSV-Verbindungen verbunden, die sie direkt miteinander verbinden. Diese TSV-Verbindungen übertragen Daten zwischen den Kristallen mit der höchstmöglichen Geschwindigkeit und befinden sich normalerweise in der Mitte des Chips, wie wir bei Intel Foveros 3D gesehen haben. Diese direkte Kopplung verbessert die Leistung und reduziert den Stromverbrauch (alle Datenbewegungen erfordern Strom, aber direkte Verbindungen optimieren den Prozess). 3D-Stapelung erhöht auch die Dichte.

Norrod ging nicht auf die Details der in der Entwicklung befindlichen Projekte ein, aber dies könnte sich als grundlegende Änderung im Design des AMD-Prozessors herausstellen.

Die neue Intel Foveros 3D-Technologie könnte sich als entscheidender Moment für die Branche herausstellen. Daher ist es nicht verwunderlich, dass AMD sich in diese Richtung bewegt,

schreibt Tom's Hardware .

Bisher gibt es keine technischen Details zur 3D-Stapeltechnologie von AMD, außer dem, was Forrest Norrod bei einer Präsentation mit dem Titel "Working Beyond Moore's Law" sagte (siehe Video unten).

Welche anderen Alternativen gibt es, um zu der von Gordon Moore vorhergesagten exponentiellen Wachstumskurve zurückzukehren? Es gibt keine einheitliche Antwort auf diese Frage. Die Halbleiterindustrie experimentiert mit Materialien, die anstelle von Silizium verwendet werden können. Einige III-V-Halbleitermaterialien können

bei niedrigeren Spannungen und höheren Frequenzen als Silizium arbeiten , aber sie machen Atome nicht kleiner oder langsamer. Es gelten weiterhin körperliche Einschränkungen.

Es bleibt die Frage, wie sich zukünftige 3D-Chips abkühlen werden. Wie kann man einen solchen Chip effektiv kühlen, wenn Energie darin verteilt wird? Der Mikrokreis kann nicht alle Stromkreise gleichzeitig ohne Überhitzung mit Strom versorgen. Wahrscheinlich muss sie einige Teile die meiste Zeit getrennt lassen und jedes Teil nur während des Gebrauchs mit Strom versorgen.