Die Linux Foundation hat eine neue Richtung eingeschlagen - die CHIPS Alliance. Im Rahmen dieses Projekts wird die Organisation ein kostenloses RISC-V-Befehlssystem und Technologien zur Erstellung darauf basierender Prozessoren entwickeln. Wir werden detaillierter erzählen, was in diesem Bereich passiert.

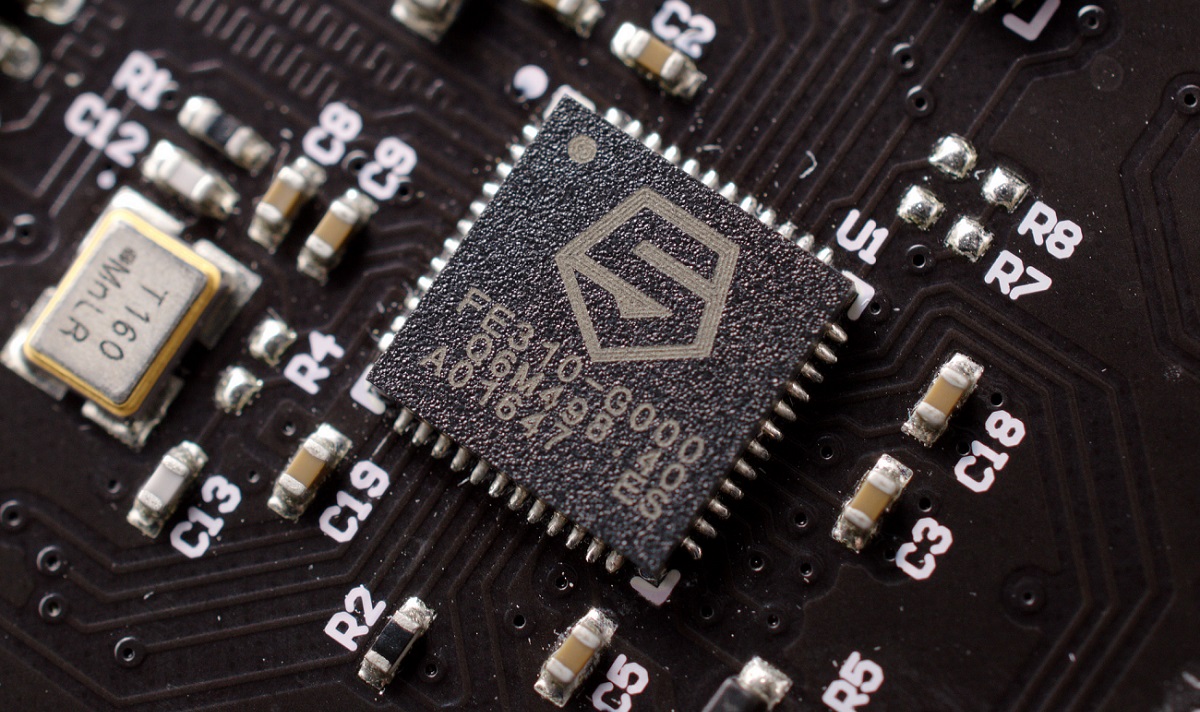

/ Foto Gareth Halfacree CC BY-SA

/ Foto Gareth Halfacree CC BY-SAWarum die CHIPS Alliance erschien

Patches, die vor Meltdown und Spectre schützen,

reduzieren in einigen Fällen

die Serverleistung um 50%. Gleichzeitig treten immer noch neue Varianten von Sicherheitslücken auf, die mit der spekulativen Ausführung von Befehlen verbunden sind. Einer von ihnen

wurde Anfang März bekannt - Experten für Informationssicherheit nannten ihn Spoiler. Diese Situation wirkt sich auf die

Diskussion über die Notwendigkeit aus, vorhandene Hardwarelösungen und Ansätze für deren Entwicklung zu überprüfen. Insbesondere

bereitet Intel

bereits eine neue Architektur für seine Prozessoren vor, die von Meltdown und Spectre nicht betroffen ist.

Sie standen in der Linux Foundation nicht beiseite. Die Organisation startete eine eigene Initiative - die CHIPS Alliance - deren Mitglieder an der Entwicklung von Prozessoren auf der Basis von RISC-V beteiligt sein werden.

Welche Projekte entwickeln sich bereits?

Die Mitgliederliste der CHIPS Alliance umfasst Google, Western Digital (WD) und SiFive. Jeder von ihnen präsentierte seine eigenen Entwicklungen. Lassen Sie uns über einige von ihnen sprechen.

RISCV-DV

Der Such-IT-Riese wechselte auf die Open-Source-Plattform, um Prozessoren auf Basis von RISC-V zu testen. Die Lösung

generiert zufällig Befehle,

mit denen Sie die Funktionsfähigkeit des Geräts überprüfen können: Testübergangsprozesse, Aufrufstapel,

CSR- Register usw.

Hier ist zum Beispiel

eine Klasse , die für die Durchführung eines einfachen Tests von Rechenanweisungen verantwortlich ist:

class riscv_arithmetic_basic_test extends riscv_instr_base_test; `uvm_component_utils(riscv_arithmetic_basic_test) `uvm_component_new virtual function void randomize_cfg(); cfg.instr_cnt = 10000; cfg.num_of_sub_program = 0; cfg.no_fence = 1; cfg.no_data_page = 1'b1; cfg.no_branch_jump = 1'b1; `DV_CHECK_RANDOMIZE_WITH_FATAL(cfg, init_privileged_mode == MACHINE_MODE; max_nested_loop == 0;) `uvm_info(`gfn, $sformatf("riscv_instr_gen_config is randomized:\n%0s", cfg.sprint()), UVM_LOW) endfunction endclass

Laut

den Entwicklern unterscheidet sich die Plattform von Analoga dadurch, dass Sie alle Komponenten des Chips, einschließlich des Speicherblocks, konsistent überprüfen können.

OmniXtend-Protokoll

Dies ist ein Netzwerkprotokoll von WD, das bei der Datenübertragung über Ethernet Cache-Kohärenz bietet.

Mit OmniXtend können

Sie Nachrichten direkt mit dem Prozessor-Cache austauschen und verschiedene Beschleuniger verbinden: GPU oder FPGA. Es eignet sich auch zum Erstellen von Systemen, die auf mehreren RISC-V-Chips basieren.

Das Protokoll wird bereits von

SweRV-Chips unterstützt, die sich auf die Datenverarbeitung in Rechenzentren konzentrieren. SweRV ist ein superskalarer 32-Bit-Dual-Pipeline-Prozessor, der auf einer 28-Nanometer-Prozesstechnologie basiert. Jede Pipeline hat neun Ebenen, wodurch mehrere Befehle gleichzeitig geladen und ausgeführt werden können. Das Gerät arbeitet mit einer Frequenz von 1,8 GHz.

Raketen-Chip-Generator

Eine Lösung von SiFive, die von den Entwicklern der RISC-V-Technologie gegründet wurde.

Rocket Chip ist ein RISC-V-Prozessorkerngenerator in Chisel. Es

ist eine Sammlung parametrisierter Bibliotheken, die zum Erstellen von

SoC verwendet werden .

Bei

Chisel handelt es sich um eine Scala-basierte Hardwarebeschreibungssprache. Es generiert auf Verilog Low-Level-Code, der für die Verarbeitung auf ASIC und FPGA

geeignet ist . Somit ermöglicht es die Verwendung von OOP-Prinzipien bei der Entwicklung von

RTL .

Allianz-Perspektiven

Experten sagen, dass die Linux Foundation-Initiative den Prozessormarkt demokratischer und offener für neue Akteure machen wird. IDC

stellt fest, dass sich die wachsende Beliebtheit solcher Projekte positiv auf die Entwicklung von Technologien für maschinelles Lernen und KI-Systemen im Allgemeinen auswirken wird.

/ Foto Fritzchens Fritz PD

/ Foto Fritzchens Fritz PDDurch die Entwicklung von Open Source-Prozessoren werden auch die Kosten für die Entwicklung kundenspezifischer Chips gesenkt. Dies wird jedoch nur geschehen, wenn es der Linux Foundation-Community gelingt, genügend Entwickler anzuziehen.

Ähnliche Projekte

Andere Organisationen entwickeln Projekte im Zusammenhang mit offener Hardware. Ein Beispiel wäre das CXL-Konsortium, das Mitte März den Compute Express Link-Standard einführte. Die Technologie ist ein Analogon von OmniXtend und verbindet auch CPU, GPU, FPGA. Für den Datenaustausch verwendet der Standard den PCIe 5.0-Bus.

Ein weiteres Projekt zur Entwicklung von Prozessortechnologien ist MIPS Open, das im Dezember 2018 erschien. Die Initiative wurde vom Startup Wave Computing ins Leben gerufen. Entwickler planen,

die neuesten 32-Bit- und 64-Bit-MIPS-Befehlssätze für die IT-Community zu

öffnen . Der Start des Projekts

wird in den kommenden Monaten

erwartet .

Im Allgemeinen wird der Open-Source-Ansatz nicht nur für Software, sondern auch für Hardware allgemein akzeptiert. Solche Projekte werden von großen Unternehmen unterstützt. Daher können wir davon ausgehen, dass in naher Zukunft weitere Geräte auf den Markt kommen werden, die auf offenen Hardwarestandards basieren.

Neue Beiträge aus unserem Unternehmensblog:

Beiträge aus unserem Telegrammkanal: