Neulich warf die

japanische Automatikstation Hayabusa-2 eine Bombe auf den Asteroiden Ryugu . Das Raumschiff wird von einem strahlungsstabilen HR5000-Chipsystem (JAXA2010 / 101) mit einem 64-Bit-MIPS-5Kf-Prozessorkern gesteuert. Auf dem Bordcomputer wird das Echtzeitbetriebssystem uITRON ausgeführt, eines aus der TRON-Standard-RTOS-Familie, das in den 1980er Jahren in Japan erschien

und einen separaten Beitrag verdient .

In diesem Hinweis werde ich kurz beschreiben, was im HR5000 SoC und seinem Prozessorkern enthalten ist. Ich werde Fotos von zwei der wichtigsten Entwickler der MIPS 4K- und 5K-Leitungen zeigen und auch erklären, wie Sie mit dem „Nachkommen eines jüngeren Bruders“ dieses Computers zu Hause auf dem FPGA spielen können. Der 32-Bit-MIPS microAptiv UP-Kernel, dessen Code in der Verilog-Hardwarebeschreibungssprache auf MIPS 4KEc basierte.

Die japanische Luft- und Raumfahrtagentur JAXA hat den MIPS 5Kf-Prozessorkern von MIPS Technologies, einem amerikanischen Unternehmen, lizenziert. Dies geschah bereits in den 2000er Jahren. Die Gruppe, die diesen Kern entwickelt hat, existiert seit 40 Jahren in verschiedenen Konfigurationen:

- Erstens war MIPS 1978-1984 ein Projekt in Stanford, das von John Hennessey geleitet wurde. Nach dem Erfolg dieses Projekts wurde Hennessey Autor des berühmtesten Lehrbuchs über Computerarchitektur und irgendwann Präsident von Stanford.

- Dann, im Jahr 1984, wurde MIPS ein Handelsunternehmen - MIPS Computer Systems. Im selben Jahr wurde auch ARM kommerzialisiert. 1991 veröffentlichte MIPS den weltweit ersten 64-Bit-Mikroprozessor - MIPS R4000.

- Danach wurde MIPS von Silicon Graphics übernommen und in den 1990er Jahren in Grafikstationen verwendet, in denen die ersten Filme mit realistischen Grafiken in Hollywood (Jurassic Park) gedreht wurden.

- In den 2000er Jahren trennte sich die Gruppe von MIPS Technologies und entwarf insbesondere einen Prozessor für JAXA. MIPS hatte seinen Hauptsitz in Kalifornien, einige der MIPS 5Kf-Entwickler befanden sich bei MIPS Europe in Kopenhagen.

- Im Jahr 2012 wurde MIPS Technologies von der britischen Firma Imagination Technologies gekauft, die als GPU-Entwickler im frühen Apple iPhone berühmt wurde.

- Im Jahr 2017 warf Apple Imagination und nach einigen Störungen die Technologie und einen Teil der MIPS-Gruppe in Wave Computing, ein Startup, das einen Chip zur Beschleunigung neuronaler Netze entwickelt.

- Der Wave Computing-Chip ist eine Kombination aus einem Cluster von 64-Bit-MIPS I6500-Prozessoren, einem Matrixmultiplikator basierend auf einem systolischen Array a la Google TPU und einem Datenprozessorprozessor basierend auf einem Gerät mit einer grobkörnigen rekonfigurierbaren Architektur - CGRA ) Klassische Prozessoren im I6500-Cluster laden den Matrixmultiplikator und den Datenstromprozessor, der Matrixmultiplikator stellt die Rechendichte bereit, und der Taskdatenstromprozessor befindet sich in der Mitte zwischen den klassischen Prozessoren und dem Matrixmultiplikator - er ist flexibler als der Multiplikator und produktiver als die klassische CPU.

Also machte ich ein Foto mit einem der beiden Hauptentwickler der MIPS 4K- und 5K-Linie - Larry Hudepohl, Larry Huedepol (rechts in einem roten Hemd). Larry begann seine Karriere bei der Digital Equipment Corporation (DEC) als Prozessordesigner für MicroVAX. Dann arbeitete Larry für eine kleine Firma Cyrix, die Ende der 1980er Jahre Intel herausforderte und einen FPU-Coprozessor herstellte, der mit Intel 80387 kompatibel und 50% schneller war. Dann entwarf Larry MIPS-Chips bei Silicon Graphics. Als sich MIPS Technologies von Silicon Graphics trennte, brachten Larry und Ryan Quinter gemeinsam das erste unabhängige MIPS-Produkt auf den Markt, MIPS 4K, das das Rückgrat der Linie bildete, die die Heimelektronik der 2000er Jahre dominierte (DVD-Player, Kameras, Digitalfernseher). Dann flog MIPS 5K ins All - es wurde von der japanischen Raumfahrtagentur JAXA genutzt. Dann leitete Larry als VP Hardware Engineering die Entwicklung der folgenden Linien und arbeitet jetzt an neuen Wave Accelerator-Architekturen:

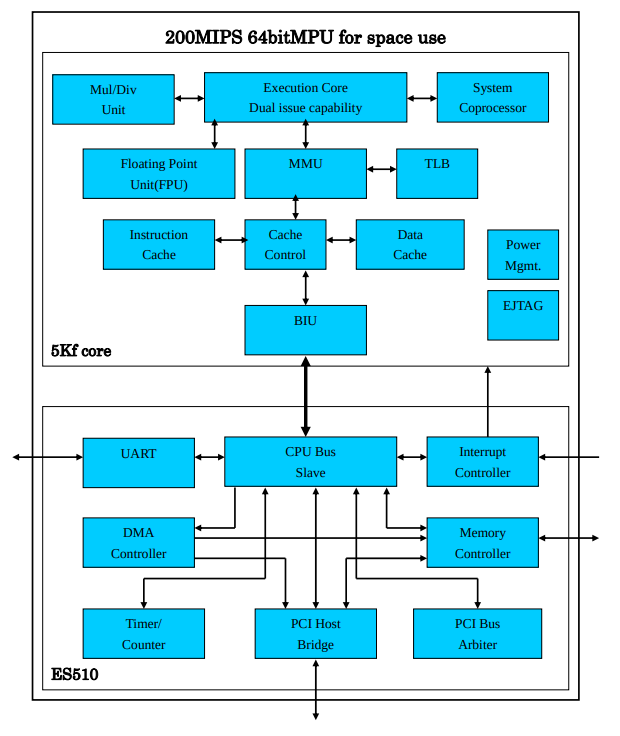

Nun zurück zum Prozessor in Hayabusa-2 (in Hayabusa-1 ist das anders). Hier ist ein

Datenblatt für den MIPS64 5Kf-Prozessorkern und eine

Seite mit Systemdaten auf einem HR5000-Chip . Beachten Sie einige interessante Punkte.

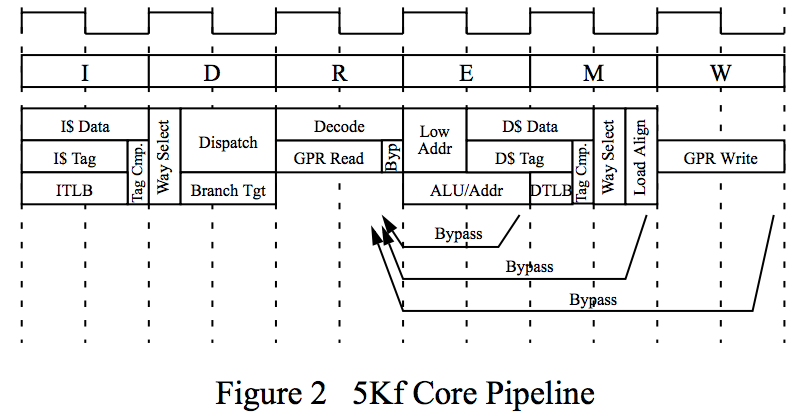

Zunächst einmal ist MIPS 5Kf ein Pipeline-Prozessor. Wenn Sie mit der Funktionsweise nicht vertraut sind, können Sie sich am einfachsten kennenlernen, indem Sie das siebte Kapitel des Buches „Digitale Schaltkreise und Computerarchitektur“ von David M. Harris und Sarah L. Harris lesen, dessen neueste Version

hier oder

hier auf Russisch heruntergeladen werden kann. . Der Förderer in MIPS 5Kf unterscheidet sich vom klassischen MIPS-Förderer von Harris & Harris. Diejenigen unter Ihnen, die X & X gelesen haben, können sich die Unterschiede ansehen und raten, warum:

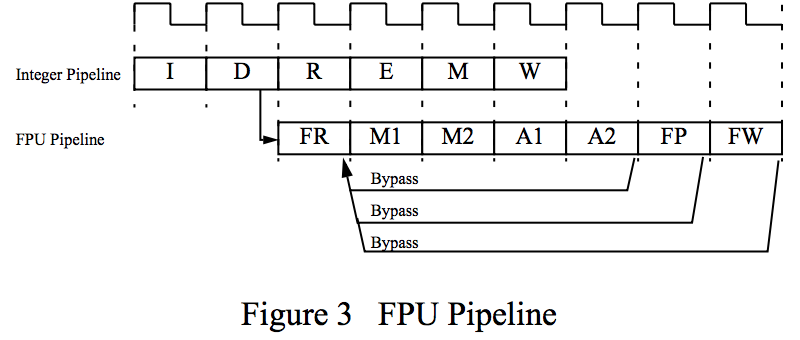

Natürlich hat MIPS 5Kf nicht fünf Pipeline-Stufen, sondern sechs mit einer zusätzlichen Versandstufe. Diese Stufe wird benötigt, um MIPS 5Kf begrenzt superskalar zu machen. Es kann nicht nur Operationen nacheinander in der Pipeline ausführen, sondern auch gleichzeitig mit einer Ganzzahloperation oder einer Speicheroperation (Laden oder Speichern) eine Gleitkommaoperation ausführen. Stage Dispatch startet einen Gleitkomma-Coprozessor mit einer eigenen siebenstufigen Pipeline:

Und hier rechts auf dem Foto ist Darren Jones, Darren Jones, FPU-Entwickler bei MIPS 5Kf. Der Buchstabe "f" in "5Kf" bedeutet genau, dass er einen Gleitkomma hat:

Hier in dieser Tabelle können Sie sehen, wie viele Zyklen unterschiedliche Operationen in der FPU erfordern und wie oft (Wiederholungsrate) sie in der Pipeline ausgeführt werden können. Beispielsweise erfordert die Multiplikation mit einfacher Genauigkeit vier Zyklen, Sie können jedoch bei jedem Zyklus eine neue Multiplikation in der Pipeline starten. Somit kann die FPU in jeder Verarbeitungsstufe gleichzeitig vier Multiplikationen mit einfacher Genauigkeit verarbeiten. Die Multiplikation mit doppelter Genauigkeit erfordert jedoch fünf Zyklen, und Sie können sie nur mit einer Pause im Zyklus starten. Die komplexe Operation, die Quadratwurzel mit doppelter Genauigkeit zu ziehen, erfordert bis zu 32 Zyklen, und Sie können erst nach 29 Zyklen mit einer neuen Quadratwurzelentnahme beginnen. So wird die Berechnung der Koordinaten des Schiffes und seiner Bewegungsformeln im Weltraum optimiert:

Hayabusa-2 verwendet die MIPS 5Kf-Konfiguration mit separaten 32-Kilobyte-Befehls- und Datencaches. Gleichzeitig ist aus der

kurzen Beschreibung von HR5000 nicht ersichtlich, ob es einen Vierkanal-Cache von 8 Kilobyte oder einen Zweikanal-Cache von 16 Kilobyte verwendet. Sie können lesen, wie diese Caches sowohl in X & X als auch in

meiner alten Präsentation über Caches funktionieren, sowie in dem nützlichen Buch

Siehe MIPS Run Linux 2nd Edition von Dominic Sweetman:

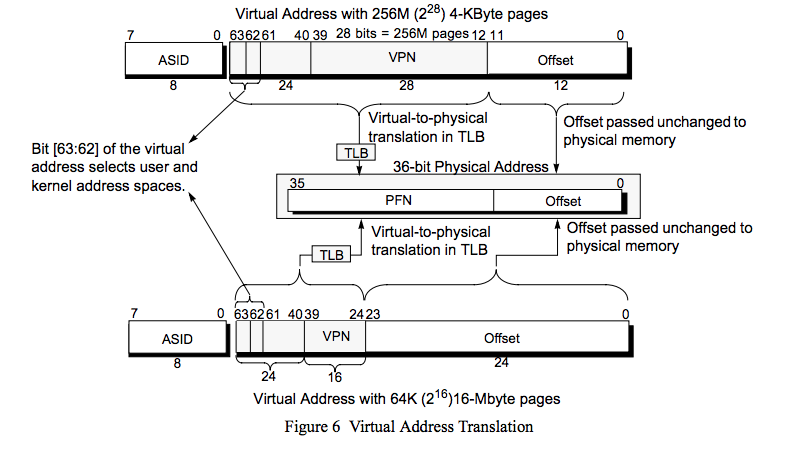

Hayabusa-2 verfügt außerdem über eine Memory Management Unit (MMU) mit einem Translation Lookaside Buffer (TLB). TLB ist ein universelles Tool zum schnellen Konvertieren von Adressen von virtuell zu physisch. Mit TLB können Sie:

Verstecken Sie den Betriebssystemspeicher vor nicht privilegiertem Code.

Schützen Sie Benutzerprogramme voreinander.

Bieten Sie Programmzugriff auf die Menge an virtuellem Speicher, die die Menge an physischem RAM überschreitet.

Adressieren Sie einen größeren physischen Speicher als virtuelle Adressen.

Platzieren Sie das Programm in einem beliebigen Teil des physischen Speichers.

Ermöglicht es mehreren Speicherbereichen, wie ein sequentielles Stück auszusehen.

Ermöglicht das Laden von Programmteilen von einem externen Gerät nach Bedarf.

Der TLB ordnet der Adresse auch verschiedene Attribute zu: Lesen, Schreiben und Ausführen sowie Cache- und Kohärenzattribute.

Das Cache-Attribut wird benötigt, um dem Prozessor anzuzeigen, wo sich der Adressraum für die nächste Cache-Ebene befindet und wo sich die E / A-Widerstände befinden, die nicht zwischengespeichert werden können.

Kohärenzattribute werden benötigt, damit mehrere Prozessorkerne zusammenarbeiten, jeder mit seinem eigenen Cache der ersten Ebene, und zusammen verwenden sie einen gemeinsamen Cache der zweiten Ebene.

TLB kann einen Indikator speichern, dass eine Seite mit einer bestimmten Adresse aufgezeichnet wurde. Dies hilft beim Austauschen, Laden und Entladen von Speicherseiten auf Systemen mit weniger physischem Speicher, als die Anwendung benötigt, um alle Teile ihres Codes und Daten mit virtuellen Adressen zu adressieren.

So sieht die Übersetzung einer virtuellen 64-Bit-Adresse in eine physische 36-Bit-Adresse auf MIPS 5Kf aus. Warum auf Hayabusa-2 ein 64-Bit-Prozessor mit physischen 36-Bit-Adressen? Ich vermute, dass Hayabusa-2 Fotos macht und Bilder verarbeiten muss, was viel Speicher erfordert. Für einige Algorithmen verbessern 64-Bit-Arithmetik- und 64-Bit-Cache-Austausche (oder 64-Bit-nicht-zwischenspeicherbare Speicheraustausche) möglicherweise etwas, und es stellt sich heraus, dass es im Weltraum nützlich ist. Aber ich weiß es nicht genau, ich muss wahrscheinlich

Zelenyikot und die

Amartologie fragen, die mehr über den Weltraum wissen als ich.

Sie können über TLB in X & X und See MIPS Run lesen, aber es gibt eine Nuance: Beide Bücher beschreiben, wie TLB aus Sicht eines Programmierers aussieht. Aus Sicht des Hardwareentwicklers täuschen die Prozessordesigner den Programmierer, indem sie ihm den TLB als eine assoziative Übersetzungstabelle zeigen, obwohl es tatsächlich drei Tabellen in der TL gibt: Es gibt drei Mikro-TLB-Anweisungen, Mikro-TLB-Daten und eine gemeinsame (gemeinsame TLB). Zuerst durchsucht das Speicherverwaltungsgerät ITLB und DTLB, und nur wenn es es nicht findet, nimmt es es von JTLB. Dies kostet den Prozessor zusätzliche 2 Zyklen. Siehe auch

meine alte Präsentation auf TLB :

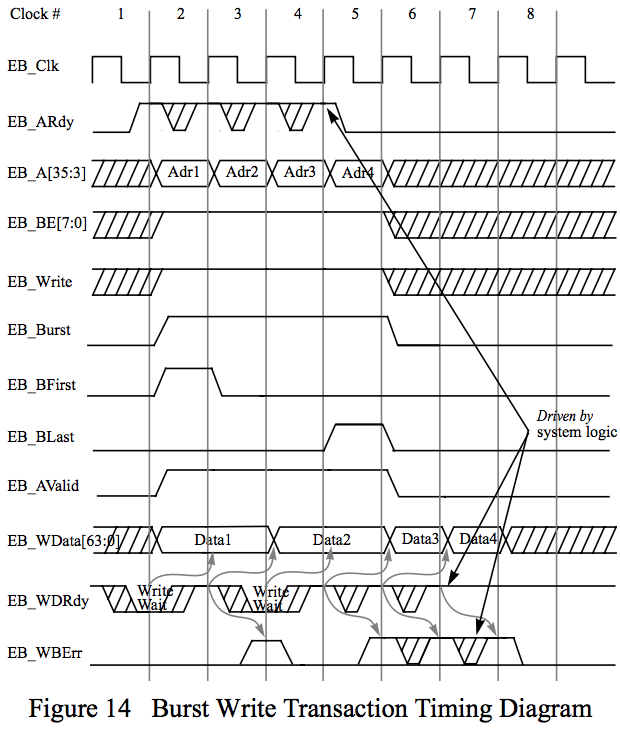

Die Schnittstelle zwischen den Caches der ersten Ebene und dem Speichercontroller in MIPS 5Kf in Hayabusa-2 heißt EB (ausgesprochen IB). Dies ist die Abkürzung für External Bus. Es ähnelt AHB und AXI und ermöglicht es Ihnen, mithilfe von Übertragungen in sequentiellen Schleifen zu platzen, aus dem Cache zu sichern oder die gesamte Zeile mit dem Cache zu füllen.

Außerhalb des Prozessorkerns verfügt der HR5000 über einen Interrupt-Controller, ein UART-Modul, einen Controller für den direkten Speicherzugriff, Timer und einen PCI-Controller:

Um im Weltraum arbeiten zu können, muss der Chip vor Strahlung geschützt werden. Ich bin kein Spezialist für Strahlenschutz, dafür gibt es auf Habré eine

Amartologie , aber ich weiß, dass ein solcher Schutz sowohl auf der Ebene der physischen Produktionstechnologie als auch auf der Ebene verschiedener ECC-Prüfungen und sogar auf der Ebene der Architektur mit Dreifach usw. erfolgen kann. Die Entwickler des HR5000-Kristallsystems entschieden sich für die in kommerziellen Anwendungen übliche RTL2GDSII-Route, die Synthese eines Graphen aus logischen Elementen aus Code in der Verilog-Hardwarebeschreibungssprache. Nachdem sie ein solches Diagramm (Netzliste) erhalten haben, ändern sie es mithilfe einer speziellen Bibliothek von Grundelementen (Hardness-by-Design, HBD) (dies wurde nie verwendet, daher ist jede Klarstellung in den Kommentaren willkommen):

Da MIPS 5Kf in Verilog geschrieben ist, kann es nicht nur in eine Netzliste und nicht nur in eine Maske zur Herstellung eines Chips in einer Fabrik, sondern auch in eine FPGA-Konfiguration umgewandelt werden. Leider sind die Quellen von MIPS 5Kf nicht gemeinfrei, aber gemeinfrei ist der Quellcode eines Nachkommen seines "jüngeren Bruders", eines 32-Bit-MIPS 4K-Prozessors. Dieser "Nachkomme" heißt MIPS microAptiv UP und seine Grundkonfiguration ist im MIPSfpga-Paket enthalten. Der MIPS 4K / 4KEc / microAptiv UP / M5150-Code (dies sind alles progressive Versionen der Linie) wurde ebenfalls von Larry, Ryan und Darren geschrieben.

Sie können mit der Pipeline, den Caches, dem Speicherverwaltungsgerät und den MIPS microAptiv UP-Kernel-Interrupts spielen, sie auf einem Simulator oder einer Karte mit FPGA / FPGA ausführen. Laden Sie dazu einfach das

MIPS Open ™ FPGA-Einstiegspaket zusammen mit den

MIPS Open ™ FPGA Labs herunter und ergänzen Sie es mit

MIPSfpga + (dies ist wichtig!). In letzterem gibt es

Labore über die Pipeline, den Cache und das Speicherverwaltungsgerät .

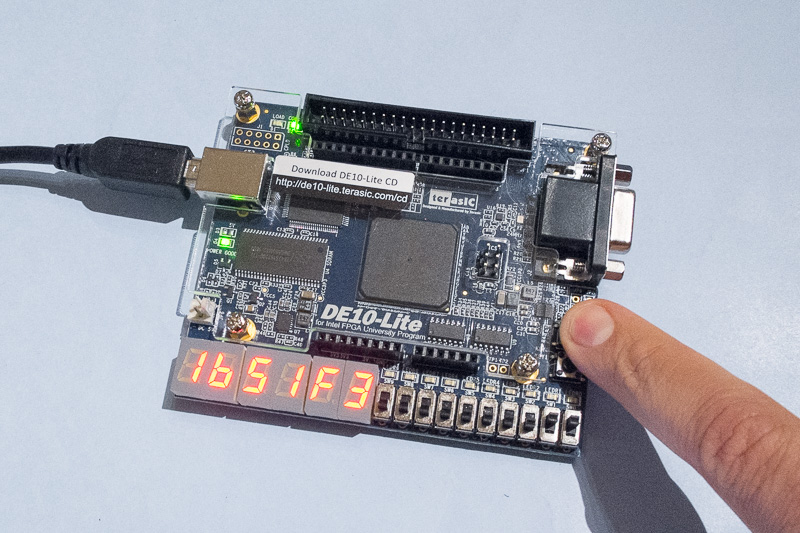

Sie können den MIPS microAptiv UP-Prozessor für 85 US-Dollar (akademischer Preis 55 US-Dollar) auf einem kostengünstigen Board synthetisieren und ausführen:

Um mit dem MIPSfpga / MIPSfpga + -Paket arbeiten zu können, benötigen Sie Kenntnisse der Verilog-Hardwarebeschreibungssprache, der Entwurfsprinzipien auf Registerübertragungsebene und der Fähigkeit, in MIPS-Assembler zu schreiben.

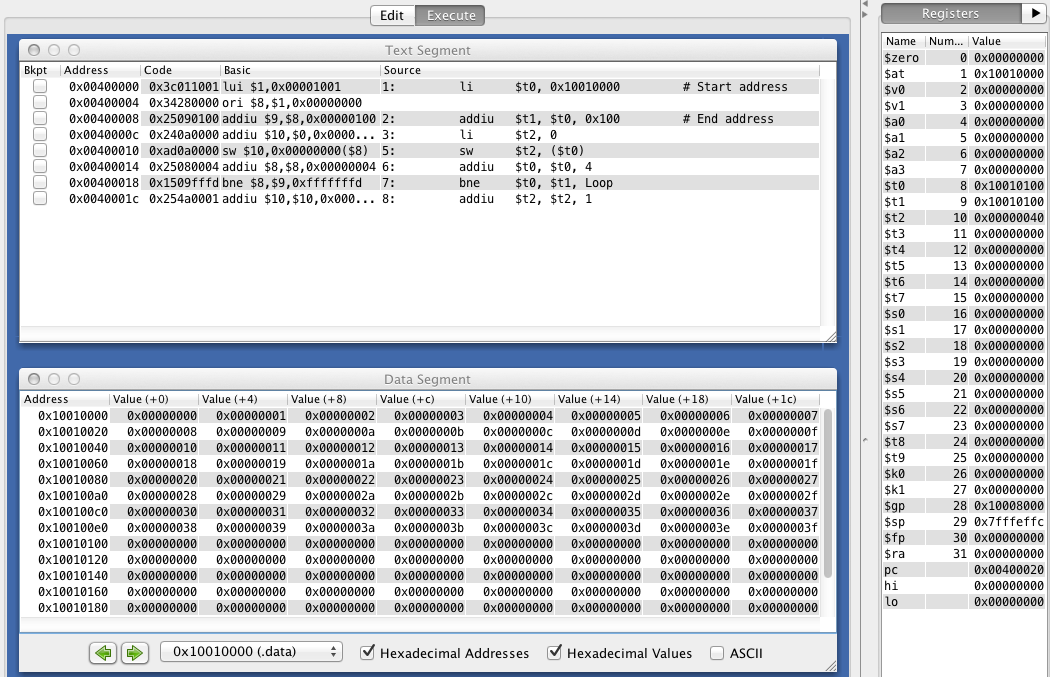

Der MIPS-Assembler ist am einfachsten zu erlernen. Dazu können Sie

den MARS-Simulator (MIPS Assembler und Runtime Simulator) herunterladen . Sie können in 5 Minuten lernen, wie man es benutzt. Tatsächlich gibt es drei Schaltflächen - zusammenbauen, ausführen, Schritt für Schritt ausführen:

Dann können Sie den Tag damit verbringen, das Schreiben in Assemblersprache für die Bücher

Harris & Harris und

See MIPS Run Linux zu üben.

Wenn Sie überhaupt nichts über die Entwicklung digitaler Schaltkreise im Allgemeinen und in der Sprache zur Beschreibung von Geräten im Besonderen wissen, können Sie mit dem Rosnanov-Onlinekurs für Schulkinder beginnen, der aus drei Teilen besteht:

„Vom Transistor zum Mikroschaltkreis“ ,

„Die logische Seite der digitalen Schaltkreise“ ,

„Die physikalische Seite digitale Schaltung " ). Dann können Sie Verilog auf X & X studieren und verstehen, dass der vereinfachte

schoolMIPS- Prozessor einen Prozessor

enthält .

Wenn Sie an diesem Thema interessiert sind und an der Arbeit an

MIPS Open teilnehmen möchten (in deren Rahmen der MIPS microAptiv UP-Kernel geöffnet wurde), schreiben Sie in die Kommentare. Rosnanovtsy veranstaltet

vom 17. bis 19. April ein

Seminar für Schüler zum Thema digitales Design , das unter anderem diesen Raumprozessor umfasst. Hayabusa-2 bombardierte Ryuga nicht umsonst - dies ist auch eine Gelegenheit für russische Schüler und Schüler, herauszufinden, was in ihr steckt.