Das nächste Kapitel aus der offiziellen Cypress-Dokumentation zu Timing und Reset-Management. Wie bereits im ersten Artikel dieser Serie erwähnt, bietet dieses Modul eine Timing-Auswahl und -Auflösung sowie eine Reset-Auswahl innerhalb der UDB. Weitere Details - unter dem Schnitt.

Der allgemeine Inhalt des Zyklus „UDB. Was ist das? "

Teil 1. Einführung. Pld.Teil 2. Datenpfad.Teil 3. Datenpfad-FIFO.Teil 4. Datenpfad ALU.Teil 5. Datenpfad. Nützliche Kleinigkeiten.Teil 6. Management- und Statusmodul.Teil 7. Steuermodul für Timing und Reset. (Aktueller Artikel)

Teil 8. Adressierung von UDB21.3.4 Modul zurücksetzen und steuern

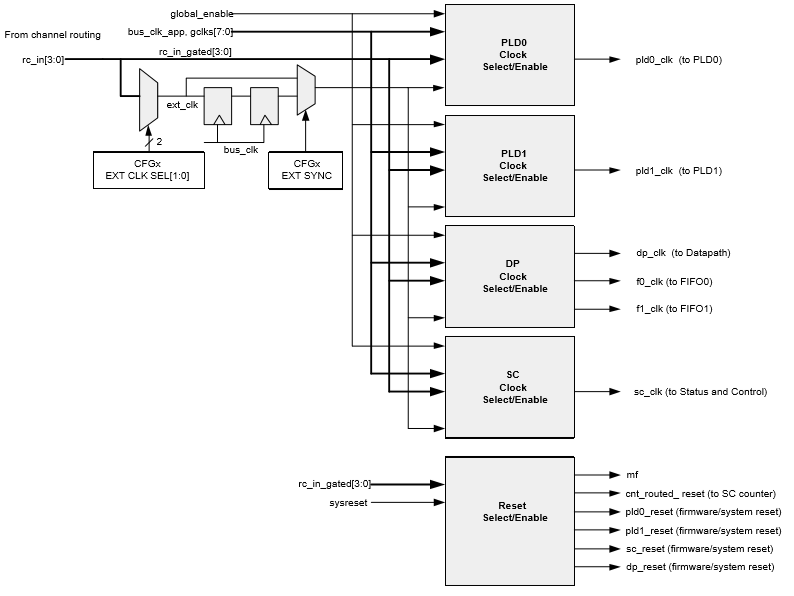

Die Hauptfunktion dieses Moduls besteht darin, Uhren aus den verfügbaren globalen Uhren oder Bustakten für jede PLD, jeden Datenpfad sowie jedes Steuerungs- und Statusmodul auszuwählen. Das Modul unterstützt auch dynamische und Software-UDB-Block-Resets. Wie in Abbildung 21-38 dargestellt, gibt es vier Taktsteuereinheiten und eine Rücksetzsteuereinheit. Für die Weiterleitung aus der globalen Trace-Matrix stehen vier Eingänge (RC_IN [3: 0]) zur Verfügung. Jede Taktsteuereinheit kann aus diesen Trace-Eingängen eine Quelle für den Clock-Freigabeeingang auswählen, und es gibt auch einen Multiplexer, mit dem Sie einen der Trace-Eingänge zur Verwendung als externe Clock-Quelle auswählen können. Wie Sie in der Abbildung sehen können, kann die Auswahl einer externen Taktquelle synchronisiert werden. Für jede UDB-Komponente stehen 10 Takte zur Auswahl: 8 globale Digitaluhren, ein Bustakt und ein ausgewählter externer Takt (ext clk). Jedes der verfolgten Eingangssignale (rc_in) kann entweder als pegelsensitiver Aktivator oder als flankensensitiver Aktivator verwendet werden. Die Rücksetzfunktion dieses Blocks bietet ein nachverfolgtes Zurücksetzen der PLD-Blöcke und des SC-Zählers sowie die Möglichkeit, jeden Block programmgesteuert zurückzusetzen, um die Rekonfiguration zu unterstützen.

Der auf den Takt und das Rücksetzsteuermodul angewendete Bustakt unterscheidet sich vom Systembustakt. Dieses Signal heißt "bus_clk_app" und ist wie andere digitale Taktsignale gesperrt. Der Systembustakt wird nur für Eingabe-Ausgabe-Operationen verwendet und bei jedem Zugriff automatisch entsperrt. Der Datenpfad-Taktgenerator erzeugt drei Takte: einen für den Datenpfad und ein Signal für jeden FIFO.

Abbildung 21-38. Steuermodul takten und zurücksetzen.

21.3.4.1 Taktsteuerung

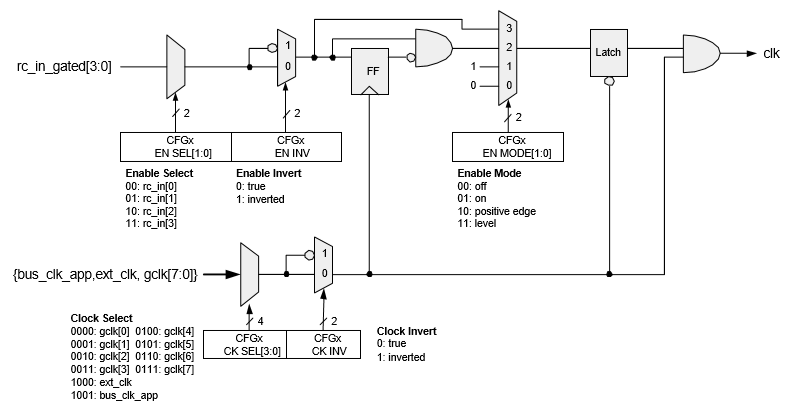

Abbildung 21-39 zeigt ein Beispiel für ein Timing-Auswahl- und Auflösungsschema. Jede UDB verfügt über vier solcher Schemata: eines für jeden PLD-Block, eines für den Datenpfad und eines für den Steuerungs- und Statusblock. Die Hauptkomponenten dieser Schaltung sind der globale Taktwählmultiplexer, der Taktinverter, der Taktfreigabesignalmultiplexer, der Taktfreigabesignalumrichter und die Differentialerfassungslogik.

Abbildung 21-39. Auswahl / Aktivierung des Timings verwalten.

Uhr AuswahlEs gibt acht globale Digitaluhren, die an alle UDBs weitergeleitet werden. Jeder von ihnen kann ausgewählt werden. Globale Digitaluhren sind Ausgänge von Frequenzteilern, die vom Benutzer ausgewählt werden. Siehe „Zeitmesssystem“ auf Seite 109 des Originals. Eine weitere Option ist die Bustaktung mit der höchsten Frequenz im System. Dieses Signal heißt "bus_clk_app" und wird getrennt von der Systembustaktung verfolgt. Um Funktionen mit einem direkten Taktsignal (z. B. SPI) zu unterstützen, kann zusätzlich eine externe Trace-Leitung als Eingangstaktsignal ausgewählt werden. Da Anwendungsfunktionen an beliebige Grenzen innerhalb der UDB gebunden sind, trägt die Auswahl eines individuellen Taktsignals für jede UDB-Unterkomponente zu einer präzisen Granularität bei der Programmierung bei.

Clock InversionDas ausgewählte Taktsignal kann invertiert werden. Dies begrenzt die maximale Häufigkeit der Arbeit aufgrund des Vorhandenseins von Abschnitten mit einem Halbzykluszyklus. Gleichzeitige Busaufzeichnung und interne Aufzeichnungen (z. B. Programmaufzeichnung eines neuen Zählerwerts während des Betriebs) werden nicht unterstützt, wenn der interne Takt invertiert ist und dieselbe Frequenz wie der Bustakt hat. Diese Einschränkung betrifft A0, A1, D0, D1 sowie das Steuerregister im Zählermodus.

Clock Enable SelectionDas Taktfreigabesignal kann an ein beliebiges synchrones Signal weitergeleitet und an einem der vier Eingänge der für diesen Block verfügbaren Trace-Matrix ausgewählt werden.

Clock Enable InversionDas Taktfreigabesignal kann invertiert werden. Aufgrund dessen kann dieses Signal in jeder Polarität erzeugt werden.

Clock Enable ModeStandardmäßig ist der Taktauflösungsmodus AUS. Nach dem Einstellen des Betriebs der Zieleinheit kann die Software mithilfe des in Abbildung 21-39 gezeigten Registers CFGxEN MODE [1: 0] einen der unten beschriebenen Betriebsmodi einstellen.

Tabelle 21-23. Timing-Auflösungsmodi.

Verwenden der UhrenberechtigungEs gibt zwei häufige Anwendungsfälle für Timing-Berechtigungen.

Software Enable (Firmware Enable) : Es wird davon ausgegangen, dass für die meisten Funktionen eine Software Clock Enable erforderlich ist, um die Funktion zu starten und zu stoppen. Da die Grenze der an das UDB-Array gebundenen Funktion bedingt ist, kann die Funktion mehrere UDBs und / oder Teile der UDBs umfassen. Daher ist ein Weg erforderlich, um jede Funktion atomar einzuschließen. Dies wird normalerweise unter Verwendung eines Bits im Steuerregister implementiert, das an einen oder mehrere Taktfreigabeeingänge weitergeleitet wird. Dieses Szenario unterstützt auch den Fall, dass Anwendungen mehrere nicht verwandte Blöcke gleichzeitig ausführen müssen.

Emulierte lokale Taktgenerierung : Mit dieser Funktion können UDBs lokale Uhren generieren und diese mithilfe der Implementierungsvorlage für die Aktivierung des Synchronisationstakts an andere UDBs im Array verteilen, anstatt jede UDB direkt zu takten. Durch die Verwendung der Positive Edge-Funktion zum Aktivieren der Auflösung werden Einschränkungen des Arbeitszyklus des Auflösungssignals aufgehoben.

Spezielles FIFO-TimingFIFO-Datenpfadblöcke verfügen über Zeitsteuerungsfunktionen. Standardmäßig hat die FIFO-Taktung dieselbe Konfiguration wie die Datenpfad-Taktung. FIFO-Blöcke haben jedoch spezielle Steuerbits, die die Taktkonfiguration ändern:

- Jeder FIFO-Takt kann relativ zur Polarität des ausgewählten Datenpfad-Takts invertiert werden.

- Wenn der FIFO-FAST-Modus ausgewählt ist, ersetzt der Bustakt die Auswahl des Datenpfadtakts, der normalerweise FIFO verwendet.

21.3.4.2 Verwaltung zurücksetzen

Es gibt zwei Reset-Verwaltungsmodi: geerbt und Standard. Der Modus wird mit dem

ALT RES- Bit in jedem Konfigurationsregister der UDB CFG31 gesetzt. Standardmäßig ist der Bitwert 0 (Legacy-Modus). Es wird empfohlen, den Wert 1 zuzuweisen (Standardmodus). Der Standardmodus weist einen höheren Grad an Granularität auf - einzelne Blöcke in UDB können nachverfolgte Spülungen verwenden. Informationen zum Legacy-Modus erhalten Sie von Cypress.

PLD Reset ControlAbbildung 21-40 zeigt das PLD-Rücksetzsystem.

Abbildung 21-40. Struktur PLD zurücksetzen.Datenpfad-Reset-Steuerung

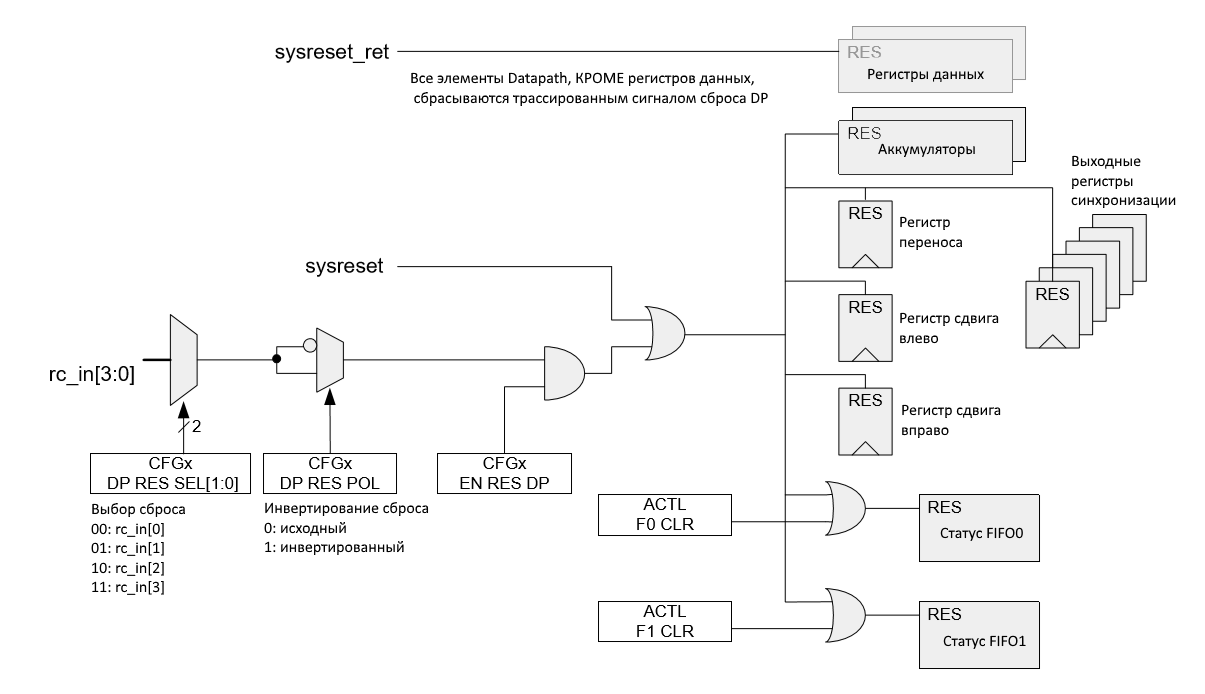

Abbildung 21-40. Struktur PLD zurücksetzen.Datenpfad-Reset-SteuerungAbbildung 21-41 zeigt das Datenpfad-Rücksetzsystem. Traced Flush gilt für alle Datenpfadregister und -zustände mit Ausnahme der Datenregister D0 und D1. Datenregister sind persistente Register. Der Inhalt des FIFO wird nach dem Zurücksetzen nicht definiert, da er sich im RAM befindet.

Abbildung 21-41. Datenpfad-Reset-Struktur.Status und Steuerung Steuerung zurücksetzen

Abbildung 21-41. Datenpfad-Reset-Struktur.Status und Steuerung Steuerung zurücksetzenAbbildung 21-42 zeigt das Steuerungs- und Statusrücksetzsystem. Die Steuer- / Zähler- und Statusregister haben einen gemeinsamen Trace-Reset, sind jedoch separat aktiviert. Die Masken- / Periodenüberlappungsregister und Hilfssteuerungen sind Sicherungsregister.

Abbildung 21-42. Reset-Management und Status-Management.

Abbildung 21-42. Reset-Management und Status-Management.21.3.4.3 UDB-Initialisierung beim Einschalten (POR)

Register- und StatusinitialisierungTabelle 21-24. Initialisierung von UDB-Status, wenn aktiviert

Trace-InitialisierungWenn diese Option aktiviert ist, weist der Status der Trace-Ein- und Ausgänge die folgenden Funktionen auf:

- Alle UDB-Ausgänge, die Daten an die Trace-Matrix leiten, werden auf '0' gehalten.

- Alle Treiber, die aus dem Trace kommen und die UDB-Eingänge eingeben, werden anfänglich auf Null gesetzt.

Diese Initialisierung vermeidet widersprüchliche Zustände während der Ablaufverfolgung, und die Erstkonfiguration erfolgt in einer Reihenfolge, in der die Reihenfolge keine Rolle spielt.

Das Ende folgt. Wir bereiten die

neueste Übersetzung des verbleibenden Abschnitts der proprietären Dokumentation von Cypress zu UDB vor, nämlich der UDB-Adressierung.