Die vorgeschlagene RAM-Erweiterungskarte für den Apple IIgs-Computer basiert auf NEC uPD424400-70-Chips aus mehreren 1-Megabyte-SIMM-Modulen. Jeder dieser Mikrochips speichert 1 M Knabbereien und ist in einem 26-poligen SOJ-Gehäuse untergebracht.

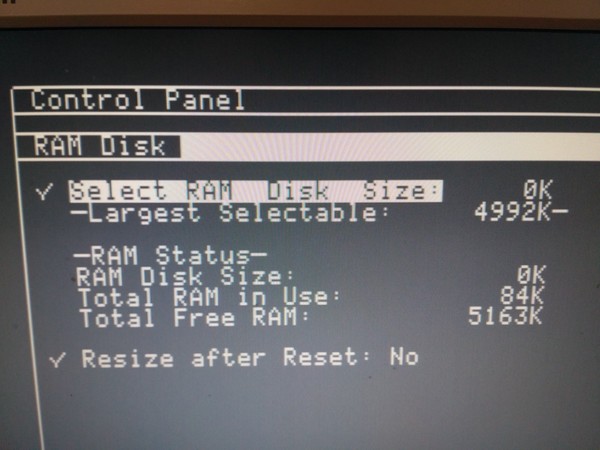

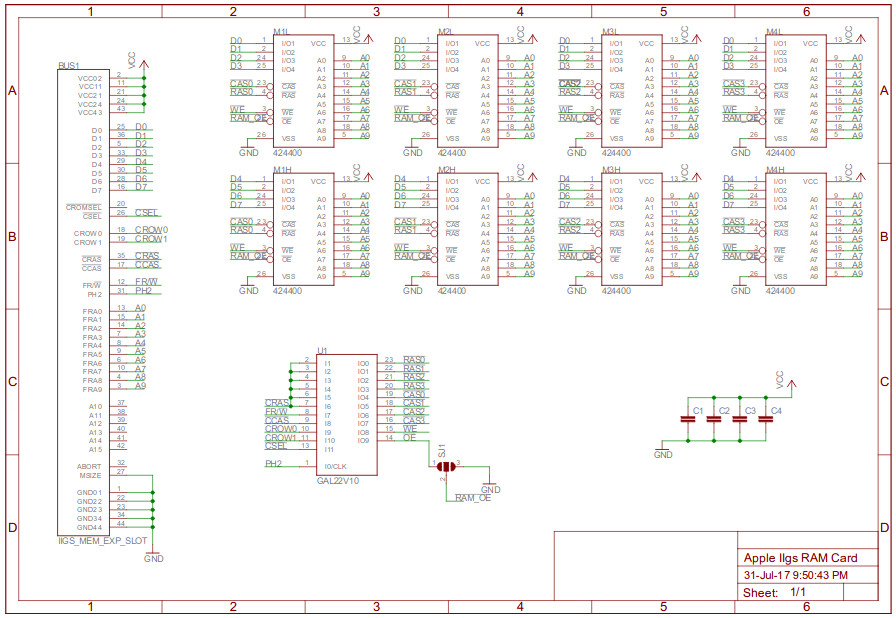

Der Apple IIgs-Computer wird von einem 65C816-Prozessor mit 16 Bit betrieben, jedoch mit einem 8-Bit-Datenbus. Die Erweiterungskarte enthält 4 MB RAM. Der Speicher ist in vier Zeilen mit jeweils 1 MB unterteilt. Die Linie besteht aus zwei Chips mit 1 M Knabbereien, sodass insgesamt acht Chips erforderlich waren.

Der Computer verfügt bereits über einen Steckplatz für die RAM-Erweiterungskarte. Es zeigt alle notwendigen Signale an, der Computer kümmert sich auch um die Regeneration des dynamischen RAM. Daher ist die Erweiterungskarte recht einfach. Der Autor hat beschlossen, die Platine klein zu machen, da die Herstellungskosten davon abhängen, und auch die gesamte Logik in das GAL22V10-FPGA zu integrieren.

Die folgenden Signale sind im RAM-Erweiterungssteckplatz vorhanden:

FRA0-FRA9 - 10-Bit-Multiplex-Zellenadresse, die direkt an die Adresseingänge dynamischer RAM-Chips geliefert wird

CROW0, 1 - zwei Bits zur Auswahl einer der vier Zeilen

/ CRAS - Signal-Strobe-Adresszeile des dynamischen RAM

/ CCAS - Signal-Gating-Spaltenadresse des dynamischen RAM

FR / W - Schreibberechtigung im RAM, dieses Signal erfordert zusätzliche Verarbeitung, siehe unten

D0-D7 - Datenbus, der direkt an die Eingangs- / Ausgangsleitungen der RAM-Chips angeschlossen ist

/ CSEL - Beim Lesen aus dem RAM erscheint in dieser Zeile eine logische Einheit, die invertiert und den Eingängen / OE der RAM-Chips zugeführt werden muss

MSIZE - teilt dem Computer die Lautstärke der Leitung mit: eins - 256 kB, null - 1 MB, hier ist diese Leitung mit einem gemeinsamen Kabel verbunden

14M, PH2CLK, A10-A15 - sind nicht an der vorgeschlagenen Karte beteiligt

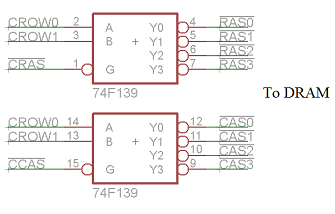

Die / CRAS- und / CCAS-Signale müssen demultiplext werden, um separate / RAS- und / CAS-Signale für jede Leitung zu erhalten. Hierfür ist der 74F139-Chip geeignet (im Folgenden versteht es sich, dass sich keine separaten Chips auf der Platine befinden, stattdessen gibt es ein gemeinsames FPGA).

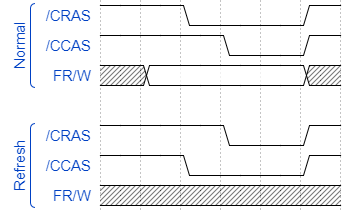

Das FR / W-Signal kann nicht direkt in den / WE-Eingang der dynamischen RAM-Chips eingespeist werden, weshalb. Bei einer normalen Lese- / Schreiboperation wird zuerst die / RAS-Leitung aktiv (was einer logischen Null entspricht), dann die / CAS-Leitung. Während eines dynamischen RAM-Regenerationszyklus wird im Gegensatz dazu zuerst die / CAS-Leitung aktiv, dann wird / RAS aktiv. Für die verwendeten Chips muss jedoch eine Einheit auf der / WE-Leitung erscheinen, bevor die / RAS-Leitung aktiv wird. Und das von Apple IIgs kommende FR / W-Signal erfüllt diese Anforderung nicht. Der Zustand von FR / W während des Regenerationszyklus ist undefiniert. Daher ist eine Schaltung erforderlich, die einen Regenerationszyklus erkennt und eine Einheit / WE zuführt.

Der erste Schritt besteht darin, den Regenerationszyklus zu identifizieren. Unten ist das Zeitdiagramm:

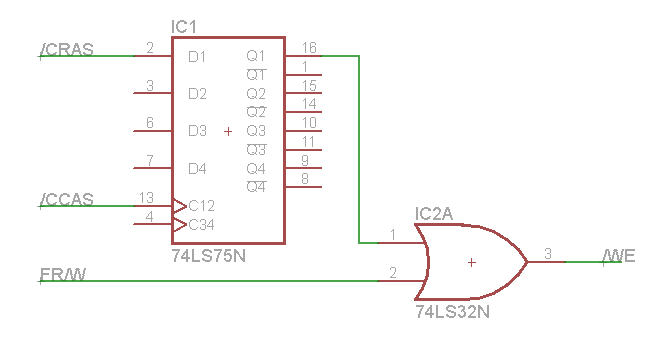

Die Idee des Autors ist es, einen „transparenten“ Riegel zu verwenden. Das / CRAS-Signal dafür ist das Eingangssignal, / CCAS ist das Latch-Signal. Wenn das Gerät eingeschaltet ist / CCAS, leitet das Gerät das Eingangssignal durch sich selbst: Der Zustand des Ausgangs ändert sich nach dem Zustand des Eingangs. Wenn / CCAS von eins auf null geht, merkt sich der Latch das Signal am Eingang und ändert sich jetzt am Ausgang nicht. Bei einer normalen Lese- / Schreiboperation auf / CRAS ist zum Zeitpunkt des Umschaltens von / CCAS von Eins auf Null Null vorhanden. Und während des Regenerationszyklus an / CRAS gibt es auch im Moment des Umschaltens von / CCAS auf Null einen. Wenn dann / CCAS auf eins zurückschaltet, wird der Latch wieder transparent. Es erinnert an eine fantastische Blume aus "Secrets of the Third Planet", die sowohl ein "Spiegel" als auch eine "Kamera" sein kann.

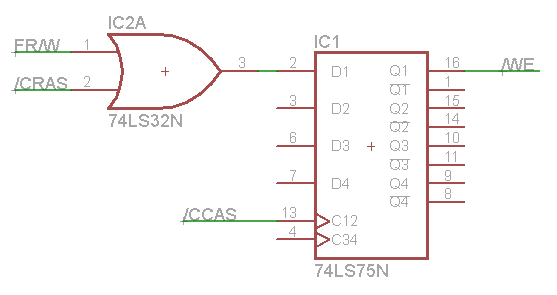

Der Autor hat zunächst folgendes Schema erstellt:

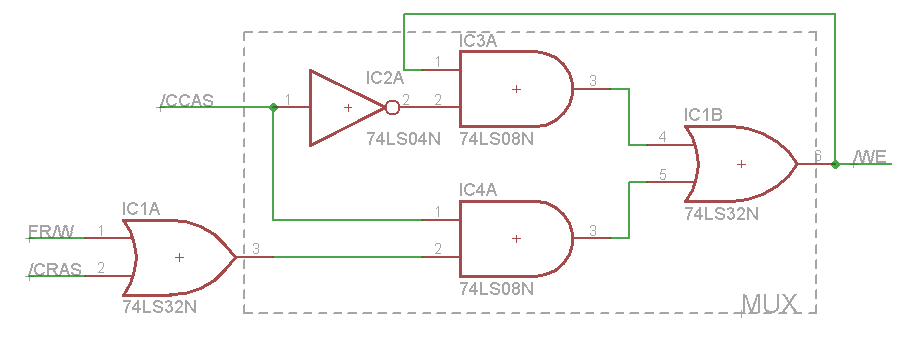

Für die Übertragung auf das FPGA GAL22V10 sind jedoch zwei Ausgangspins erforderlich. Daher musste das Schema vereinfacht werden. Während des normalen Betriebs nimmt das FR / W-Signal den gewünschten Wert an, bis es klickt. Dies ist also auch möglich.

Ein "transparenter" Latch kann aus einem Multiplexer und wiederum aus logischen Elementen hergestellt werden. Das Schema sieht folgendermaßen aus:

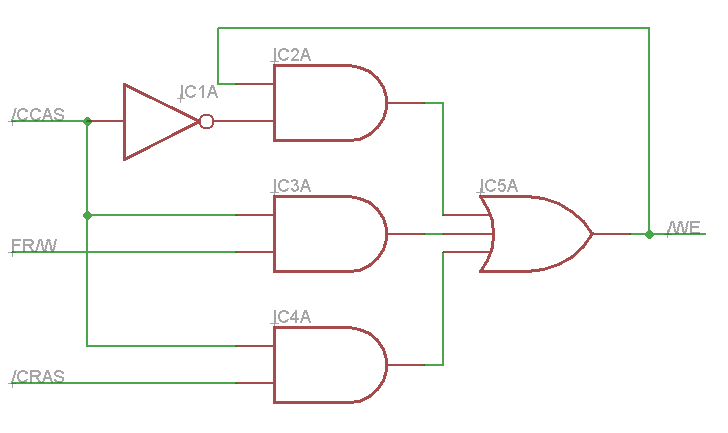

Und nach der Vereinfachung - so:

Diese Option wird auf das FPGA übertragen. Für die Kompilierung verwendete der Autor WinCUPL. Dieses Programm befindet sich auf der Atmel-Website. Es ist roh und fliegt ständig, aber es hat die Aufgabe perfekt gemeistert. Programmierer - Genius G540.

Der Jumper SJ1 auf dem Board verhält sich so. Wenn die Pins 1 und 2 verbunden sind, wird das / OE-Signal durch das FPGA geleitet. Wenn die Pins 2 und 3 verbunden sind, ist sie mit einem gemeinsamen Draht verbunden. Der Autor war sich nicht sicher, ob das Schema zur Identifizierung des Regenerationszyklus funktionieren würde. Daher fügte er diesen Jumper hinzu, falls die FPGA-Konfiguration erneuert werden musste.

Da sich herausstellte, dass alles funktioniert, müssen Sie die Stifte nicht löten, sondern nur die Klemmen 1 und 2 mit einem Tropfen Lötmittel verbinden.

Um die Größe der Platine zu verringern, hat der Autor einen Leistungskondensator pro vier RAM-Chips angelegt und die Chips selbst auf beiden Seiten der Platine platziert.

Mikrochips in SOJ-Fällen sind mit einem Lötkolben schwer zu löten und insbesondere zu löten. Der Autor empfiehlt die Verwendung eines Haartrockners.

Erweitern Sie die Chips richtig. Unter dem Strich sind sie invertiert. Pin 1 schaut nach unten.

Einige Durchgangslöcher befinden sich zu nahe an den Pads. Schließen Sie sie nicht mit Lötmittel kurz.

Und die Plattformen 1 und 2 für den Jumper schließen sich dagegen.

Die Kondensatoren C1 - C3 haben eine Kapazität von 0,1 μF, C4 - 10 μF.

Der Autor bestellte die Boards im OSH Park. Die ENIG-Beschichtung wird aufgetragen - Gold, aber sehr dünn. Für Spielekassetten ist es nicht geeignet - es wird schnell gelöscht. Und hier wurde das Brett einmal in den Schlitz gelegt und wird dort nicht mehr entfernt.

Der Autor dankt

GGLabs für die Schaltung eines ähnlichen Boards, es hat sehr geholfen, danke!

Die fertige Schaltung stellte sich wie folgt heraus:

Dateien:

FPGA-Firmware GAL22V10 , WinCUPL-Programm Version 5.30.4 angewendet

Board , Eagle Version 7.1 Software angewendet

PDF-GliederungVerdient!