Übersetzung des ersten Teils der Präsentation zum Tesla Autonomy Investor Day über die Entwicklung eines voll selbstfahrenden Computers für den Tesla-Autopiloten. Wir füllen die Lücke zwischen den Reviews der Dissertation für die Präsentation und deren Inhalt.Der Text der Präsentation wird nahe am Original übersetzt. Fragen an den Sprecher - selektiv mit Abkürzungen.Gastgeber: Hallo an alle. Verzeihen Sie mir für die Verspätung. Willkommen zu unserem ersten Tag des autonomen Fahrens. Ich hoffe, wir können dies regelmäßiger tun, um Sie über unsere Entwicklungen auf dem Laufenden zu halten.

Vor ungefähr drei Monaten haben wir uns mit Ilon und anderen Führungskräften auf den Ergebnisbericht für das vierte Quartal vorbereitet. Ich sagte dann, dass die größte Lücke in den Gesprächen mit Investoren zwischen dem, was ich im Unternehmen sehe und der Wahrnehmung von außen, unser Fortschritt beim autonomen Fahren ist. Und das ist verständlich. In den letzten Jahren haben wir über die Steigerung der Produktion von Modell 3 gesprochen, um das es viele Kontroversen gab. Tatsächlich ist im Hintergrund viel passiert.

Wir haben an einem neuen Chip für den Autopiloten gearbeitet, das neuronale Bildverarbeitungsnetzwerk komplett neu gestaltet und schließlich mit der Veröffentlichung des Full Self-Driving Computer (FSDC) begonnen. Wir hielten es für eine gute Idee, einfach den Schleier zu öffnen, alle einzuladen und über alles zu erzählen, was wir in den letzten zwei Jahren getan haben.

Vor ungefähr drei Jahren wollten wir den besten Chip für autonomes Fahren finden. Wir haben festgestellt, dass es keinen Chip gibt, der von Grund auf für neuronale Netze entwickelt wurde. Deshalb haben wir meinen Kollegen Pete Bannon, Vizepräsident für Design integrierter Schaltkreise, eingeladen, einen solchen Chip für uns zu entwickeln. Er hat ungefähr 35 Jahre Erfahrung in der Chipentwicklung. Darunter 12 Jahre bei PASemi, das später von Apple übernommen wurde. Er arbeitete an Dutzenden verschiedener Architekturen und Implementierungen und war der Chefdesigner des Apple iPhone 5, kurz bevor er zu Tesla kam. Begleitet uns auch auf Elon Musk. Vielen Dank.

Ilon: Eigentlich wollte ich Pete vorstellen, aber da sie dies bereits getan haben, möchte ich hinzufügen, dass er einfach der beste System- und integrierte Schaltungsarchitekt der Welt ist, den ich kenne. Es ist eine Ehre, dass Sie und Ihr Team bei Tesla. Bitte erzählen Sie uns einfach von der unglaublichen Arbeit, die Sie geleistet haben.

Pete: Danke Ilon. Ich freue mich, heute Morgen hier zu sein, und es ist wirklich schön, Ihnen von all der Arbeit zu erzählen, die meine Kollegen und ich hier in Tesla in den letzten drei Jahren geleistet haben. Ich werde Ihnen ein wenig darüber erzählen, wie alles begann, und dann werde ich Ihnen den FSDC-Computer vorstellen und Ihnen ein wenig erzählen, wie es funktioniert. Wir werden uns mit dem Chip selbst befassen und einige Details betrachten. Ich werde beschreiben, wie der von uns entworfene spezialisierte Beschleuniger für neuronale Netze funktioniert, und dann einige Ergebnisse zeigen, und ich hoffe, dass Sie zu diesem Zeitpunkt noch nicht einschlafen werden.

Ich wurde im Februar 2016 eingestellt. Ich fragte Ilon, ob er bereit sei, so viel wie nötig für die Schaffung dieses spezialisierten Systems auszugeben. Er fragte: "Werden wir gewinnen?", Ich antwortete: "Nun ja, natürlich", dann sagte er "Ich bin im Geschäft" und alles begann . Wir stellten eine Menge Leute ein und begannen darüber nachzudenken, wie ein Chip aussehen würde, der speziell für vollständig autonomes Fahren entwickelt wurde. Wir haben achtzehn Monate damit verbracht, die erste Version zu entwickeln, und sie im August 2017 für die Produktion freigegeben. Wir haben den Chip im Dezember bekommen, er hat funktioniert und beim ersten Versuch tatsächlich sehr gut funktioniert. Im April 2018 haben wir mehrere Änderungen vorgenommen und Version B zero Rev. veröffentlicht. Im Juli 2018 wurde der Chip zertifiziert und wir begannen mit der Serienproduktion. Im Dezember 2018 wurde der autonome Fahrstapel für neue Geräte eingeführt, und wir konnten mit der Umrüstung von Dienstwagen und Tests in der realen Welt fortfahren. Im März 2019 Wir haben mit der Installation eines neuen Computers in den Modellen S und X und im April begonnen - in Modell 3.

Das gesamte Programm, von der Einstellung der ersten Mitarbeiter bis zur vollständigen Einführung aller drei Modelle unserer Autos, dauerte etwas mehr als drei Jahre. Dies ist vielleicht das schnellste Systementwicklungsprogramm, an dem ich jemals teilgenommen habe. Und es spricht wirklich von den Vorteilen einer hohen vertikalen Integration, die es Ihnen ermöglicht, parallel zu entwerfen und die Bereitstellung zu beschleunigen.

In Bezug auf die Ziele haben wir uns ausschließlich auf die Anforderungen von Tesla konzentriert, was das Leben erheblich vereinfacht. Wenn Sie einen einzelnen Kunden haben, müssen Sie sich keine Sorgen um andere machen. Eines der Ziele war es, die Leistung unter 100 Watt zu halten, damit wir vorhandene Maschinen umrüsten können. Wir wollten auch die Kosten senken, um Redundanz für mehr Sicherheit zu gewährleisten.

Zu der Zeit, als wir unsere Finger in den Himmel steckten, argumentierte ich, dass das Autofahren eine Leistung des neuronalen Netzwerks von mindestens 50 Billionen Operationen pro Sekunde erfordern würde. Deshalb wollten wir mindestens genauso viel und besser mehr. Die Stapelgrößen bestimmen die Anzahl der Artikel, mit denen Sie gleichzeitig arbeiten. Beispielsweise haben Google TPUs eine Paketgröße von 256 und Sie müssen warten, bis 256 Elemente verarbeitet werden müssen, bevor Sie beginnen können. Wir wollten nicht warten und entwickelten unseren Motor mit einer Packungsgröße von eins. Sobald das Bild angezeigt wird, verarbeiten wir es sofort, um Verzögerungen zu minimieren und die Sicherheit zu erhöhen.

Wir brauchten einen Grafikprozessor für die Nachbearbeitung. Anfangs nahm es ziemlich viel ein, aber wir gingen davon aus, dass es mit der Zeit kleiner werden würde, da neuronale Netze immer besser werden. Und es ist wirklich passiert. Wir sind Risiken eingegangen, indem wir einen eher bescheidenen Grafikprozessor in das Design integriert haben, und das hat sich als gute Idee herausgestellt.

Sicherheit ist sehr wichtig. Wenn Sie kein geschütztes Auto haben, können Sie kein sicheres Auto haben. Daher wird der Sicherheit und natürlich der Sicherheit viel Aufmerksamkeit geschenkt.

In Bezug auf die Chiparchitektur gab es, wie Ilon bereits erwähnte, 2016 keinen Beschleuniger, der ursprünglich für neuronale Netze entwickelt wurde. Jeder fügte einfach Anweisungen zu seiner CPU, GPU oder DSP hinzu. Niemand hat mit 0 entwickelt. Deshalb haben wir beschlossen, es selbst zu machen. Für andere Komponenten haben wir Standard-IP-Industrie-CPUs und -GPUs gekauft, wodurch wir die Entwicklungszeit und die Risiken reduzieren konnten.

Eine andere Sache, die für mich etwas unerwartet war, war die Möglichkeit, vorhandene Befehle in Tesla zu verwenden. Tesla verfügte über hervorragende Entwicklerteams für Netzteile, Signalintegritätsanalyse, Gehäusedesign, Firmware, Systemsoftware, Leiterplattenentwicklung und ein wirklich gutes Systemvalidierungsprogramm. All dies konnten wir nutzen, um das Programm zu beschleunigen.

So sieht es aus. Rechts sehen Sie die Anschlüsse für Videos, die von den Kameras des Autos stammen. Links zwei autonome Fahrcomputer in der Mitte der Platine - die Netzteil- und Steueranschlüsse. Ich liebe es, wenn eine Lösung auf ihre Grundelemente hinausläuft. Sie haben ein Video, einen Computer und Strom, einfach und klar. Hier ist die vorherige Hardware 2.5-Lösung, die den Computer enthielt und die wir in den letzten zwei Jahren installiert haben. Hier ist ein neues Design für einen FSD-Computer. Sie sind sehr ähnlich. Dies ist natürlich auf die Einschränkungen des Programms zur Fahrzeugmodernisierung zurückzuführen. Ich möchte darauf hinweisen, dass dies eigentlich ein eher kleiner Computer ist. Es befindet sich hinter dem Handschuhfach und nimmt nicht die Hälfte des Kofferraums ein.

Wie ich bereits sagte, befinden sich zwei völlig unabhängige Computer auf der Platine. Sie sind blau und grün hervorgehoben. Auf den Seiten jedes SoC sehen Sie DRAM-Chips. Unten links sehen Sie FLASH-Chips, die das Dateisystem darstellen. Es gibt zwei unabhängige Computer, die unter ihrem eigenen Betriebssystem gestartet und ausgeführt werden.

Ilon: Das allgemeine Prinzip ist, dass sich die Maschine weiter bewegen kann, wenn ein Teil ausfällt. Die Kamera, der Stromkreis und einer der Tesla-Computerchips fallen aus - die Maschine bewegt sich weiter. Die Wahrscheinlichkeit eines Ausfalls dieses Computers ist erheblich geringer als die Wahrscheinlichkeit, dass der Fahrer das Bewusstsein verliert. Dies ist ein Schlüsselindikator, mindestens eine Größenordnung.

Pete: Ja, eines der Dinge, die wir tun, um den Computer am Laufen zu halten, sind redundante Netzteile. Der erste Chip läuft auf einer Stromquelle und der zweite auf einer anderen. Gleiches gilt für Kameras. Die Hälfte der Kameras am Netzteil ist blau und die andere Hälfte grün markiert. Beide Chips empfangen das gesamte Video und verarbeiten es unabhängig voneinander.

Unter dem Gesichtspunkt des Fahrens besteht die Sequenz darin, viele Informationen aus der Welt um Sie herum zu sammeln. Wir haben nicht nur Kameras, sondern auch Radar, GPS, Karten, Kreiselstabilisator (IMU) und Ultraschallsensoren rund um das Auto. Wir haben einen Lenkwinkel, wir wissen, wie die Beschleunigung eines Autos sein sollte. All dies kommt zusammen, um einen Plan zu bilden. Wenn der Plan fertig ist, tauschen die beiden Computer ihre Versionen des Plans aus, um sicherzustellen, dass sie übereinstimmen.

Unter der Annahme, dass der Plan derselbe ist, geben wir Steuersignale aus und fahren. Jetzt, da Sie mit den neuen Steuerelementen arbeiten, möchten Sie sie auf jeden Fall testen. Wir überprüfen, ob die übertragenen Steuersignale mit dem übereinstimmen, was wir an die Aktuatoren im Auto senden wollten. Sensoren werden verwendet, um zu überprüfen, ob die Steuerung tatsächlich stattfindet. Wenn Sie das Auto bitten, zu beschleunigen oder zu verlangsamen oder nach rechts oder links abzubiegen, können Sie auf die Beschleunigungsmesser schauen und sicherstellen, dass dies wirklich geschieht. Sowohl unsere Daten als auch unsere Datenüberwachungsfunktionen sind erheblich redundant und doppelt vorhanden.

Reden wir über den Chip. Es ist in einem 37,5-mm-BGA mit 1600 Pins verpackt, von denen die meisten Strom und Masse sind. Wenn Sie die Abdeckung entfernen, sehen Sie das Substrat und den Kristall in der Mitte. Wenn Sie den Kristall trennen und umdrehen, sehen Sie 13.000 C4-Unebenheiten auf der Oberfläche. Unten sind die zwölf Metallschichten der integrierten Schaltung aufgeführt. Dies ist ein 14-Nanometer-FinFET-CMOS-Prozess mit einer Größe von 260 mm², einer kleinen Schaltung. Zum Vergleich ist ein herkömmlicher Handy-Chip etwa 100 mm2 groß. Ein Hochleistungsgrafikprozessor hat eine Größe von ca. 600-800 mm.kv. Wir sind also in der Mitte. Ich würde es das goldene Mittel nennen, dies ist eine bequeme Größe für die Montage. Es gibt 250 Millionen Logikelemente und 6 Milliarden Transistoren, die mich, obwohl ich die ganze Zeit daran gearbeitet habe, in Erstaunen versetzen. Der Chip wird gemäß der Automobilnorm AEC Q100 hergestellt und getestet.

Ich würde einfach um den Chip herumgehen und alle seine Teile erklären. Ich gehe in der gleichen Reihenfolge wie das Pixel, das von der Kamera kommt. In der oberen linken Ecke sehen Sie die Kameraoberfläche. Wir können 2,5 Milliarden Pixel pro Sekunde aufnehmen, was für alle verfügbaren Sensoren mehr als ausreichend ist. Ein Netzwerk, das Daten von einem Speichersystem an Speichercontroller am rechten und linken Rand des Chips verteilt. Wir verwenden Standard-LPDDR4 mit einer Geschwindigkeit von 4266 Gigabit pro Sekunde. Dies ergibt einen maximalen Durchsatz von 68 Gigabyte pro Sekunde. Dies ist eine ziemlich gute Bandbreite, aber nicht übermäßig. Wir versuchen, im Mittelweg zu bleiben. Der Bildverarbeitungsprozessor verfügt über eine interne 24-Bit-Pipeline, mit der wir die im Auto befindlichen HDR-Sensoren voll nutzen können. Es führt eine erweiterte Tonzuordnung durch, die dazu beiträgt, Details und Schatten besser hervorzuheben, und führt eine erweiterte Rauschunterdrückung durch, die einfach die Gesamtqualität der Bilder verbessert, die wir in einem neuronalen Netzwerk verwenden.

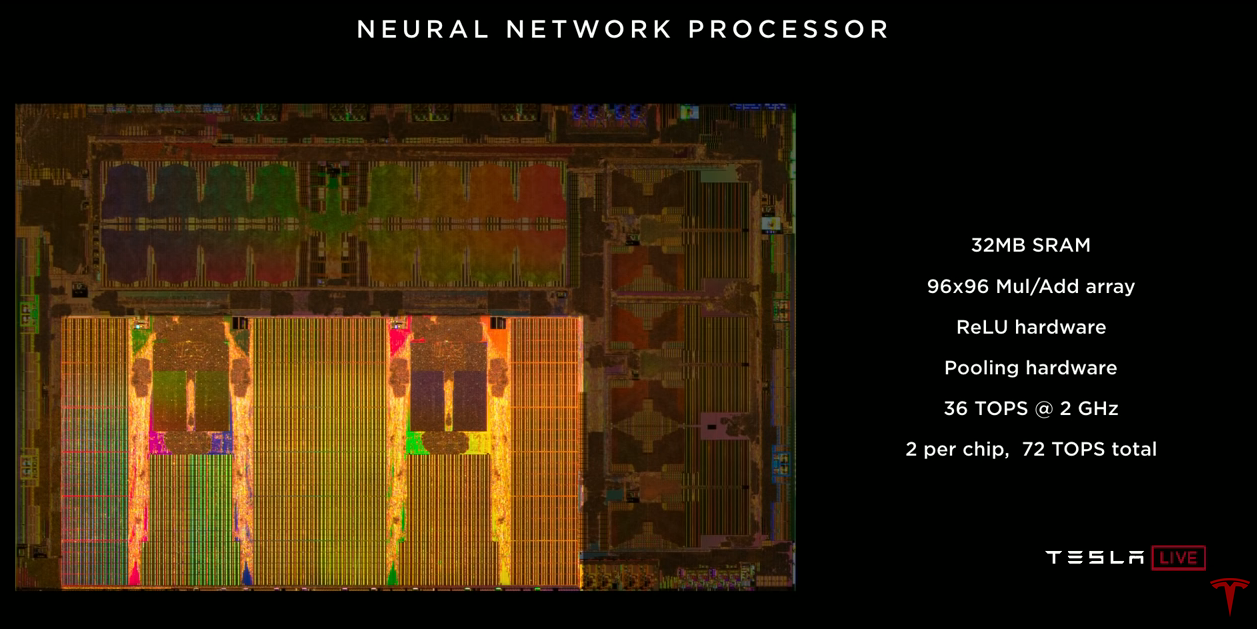

Der neuronale Netzwerkbeschleuniger selbst. Es gibt zwei auf dem Chip. Jeder von ihnen verfügt über 32 Megabyte SRAM zum Speichern temporärer Ergebnisse. Dies minimiert die Datenmenge, die wir auf den Chip übertragen müssen, und umgekehrt, wodurch der Stromverbrauch gesenkt wird. Jedes enthält ein Array von 96x96-Multiplikatoren mit Akkumulation, mit denen wir fast 10.000 MUL / ADD-Operationen pro Zyklus ausführen können. Es gibt einen dedizierten ReLU-Beschleuniger, einen Pooling-Beschleuniger. Jeder von ihnen liefert 36 Billionen Operationen pro Sekunde bei einer Frequenz von 2 GHz. Zwei Beschleuniger auf einem Chip ergeben 72 Billionen Operationen pro Sekunde, was deutlich über dem Ziel von 50 Billionen liegt.

Der Video-Encoder, das Video, das wir im Auto für viele Aufgaben verwenden, einschließlich der Ausgabe von Bildern von der Rückfahrkamera, der Videoaufzeichnung sowie der Aufzeichnung von Daten in die Cloud, werden Stuart und Andrew später besprechen. Auf dem Chip befindet sich ein eher bescheidener Grafikprozessor. Es unterstützt 32- und 16-Bit-Gleitkommazahlen. Außerdem 12 64-Bit-Allzweck-A72-Prozessoren. Sie arbeiten mit einer Frequenz von 2,2 GHz, was ungefähr dem 2,5-fachen der Leistung der vorherigen Lösung entspricht. Das Sicherheitssystem enthält zwei Prozessoren, die im Lockstep-Modus arbeiten. Dieses System trifft die endgültige Entscheidung, ob es sicher ist, Steuersignale an die Antriebe des Fahrzeugs zu übertragen. Hier kommen die beiden Flugzeuge zusammen und wir entscheiden, ob es sicher ist, vorwärts zu kommen. Und schließlich ein Sicherheitssystem, dessen Aufgabe es ist, sicherzustellen, dass auf diesem Chip nur kryptografisch signierte Tesla-Software verwendet wird.

Ich habe Ihnen viele verschiedene Leistungsindikatoren genannt, und ich denke, es wäre nützlich, in die Zukunft zu schauen. Wir werden ein neuronales Netzwerk von unserer (schmalen) Kamera aus betrachten. Es dauert 35 Milliarden Operationen. Wenn wir alle 12 CPUs verwenden, um dieses Netzwerk zu verarbeiten, können wir 1,5 Bilder pro Sekunde erstellen, es ist sehr langsam. Absolut nicht genug, um ein Auto zu fahren. Wenn wir GPUs mit 600 GFLOPs für dasselbe Netzwerk verwenden würden, würden wir 17 Bilder pro Sekunde erhalten, was immer noch nicht ausreicht, um ein Auto mit 8 Kameras zu fahren. Unser neuronaler Netzwerkbeschleuniger kann 2100 Bilder pro Sekunde erzeugen. Sie können sehen, dass der Rechenaufwand in der CPU und der GPU im Vergleich zum Beschleuniger für neuronale Netze vernachlässigbar ist.

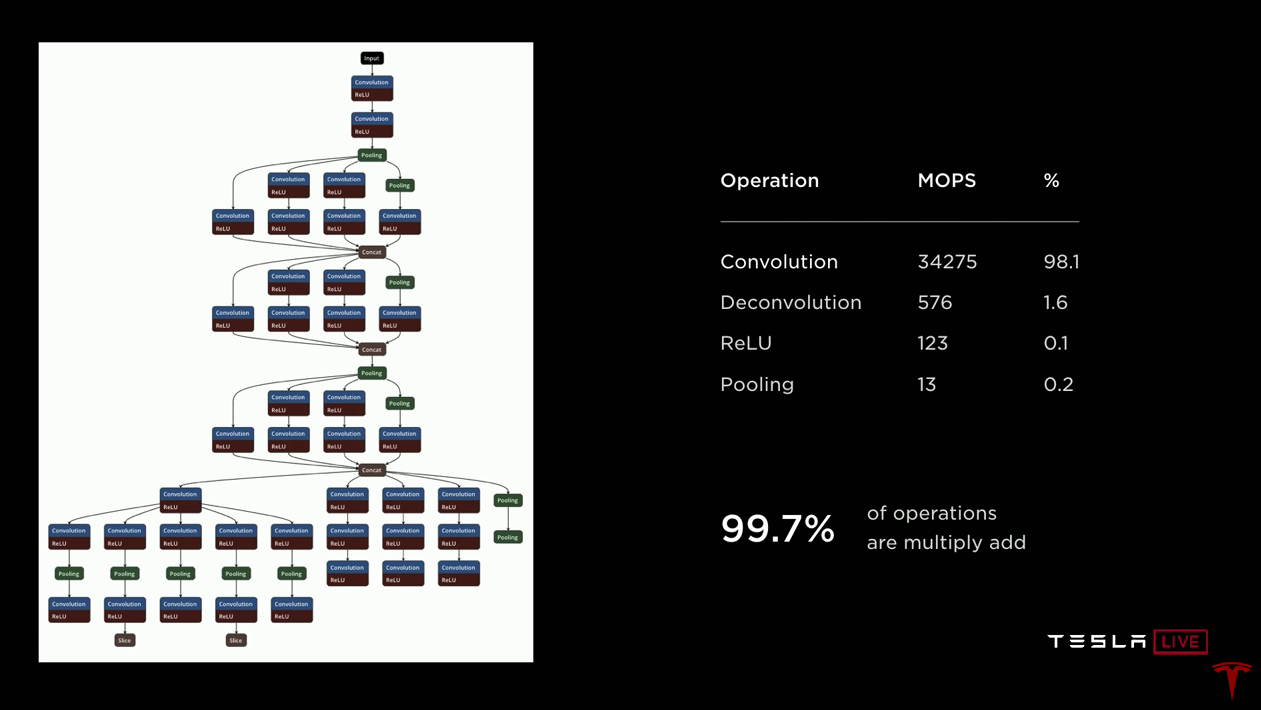

Lassen Sie uns weiter über einen Beschleuniger für neuronale Netze sprechen. Ich trinke nur etwas Wasser. Auf der linken Seite sehen Sie eine Zeichnung eines neuronalen Netzwerks, um Ihnen eine Vorstellung davon zu geben, was los ist. Die Daten kommen oben an und durchlaufen jeden der Blöcke. Daten werden entlang der Pfeile an verschiedene Blöcke übertragen, bei denen es sich normalerweise um Faltungen oder umgekehrte Faltungen mit Aktivierungsfunktionen (ReLUs) handelt. Grüne Blöcke kombinieren Schichten. Es ist wichtig, dass die von einem Block empfangenen Daten dann vom nächsten Block verwendet werden und Sie sie nicht mehr benötigen - Sie können sie wegwerfen. Alle diese temporären Daten werden beim Durchlaufen des Netzwerks erstellt und zerstört. Es ist nicht erforderlich, sie außerhalb des Chips im DRAM zu speichern. Daher speichern wir sie nur in SRAM, und in wenigen Minuten werde ich erklären, warum dies sehr wichtig ist.

Wenn Sie auf die rechte Seite schauen, werden Sie sehen, dass in diesem Netzwerk von 35 Milliarden Operationen fast alle Faltungen sind, im Wesentlichen skalare Produkte, der Rest Entfaltung (umgekehrte Faltungen), ebenfalls basierend auf dem skalaren Produkt, und dann ReLU und Pooling relativ einfach sind Operationen. Wenn Sie einen Beschleuniger entwickeln, konzentrieren Sie sich daher darauf, skalare Produkte basierend auf Addition mit Akkumulation zu implementieren und zu optimieren. Stellen Sie sich jedoch vor, Sie beschleunigen diesen Vorgang um das 10.000-fache und 100% werden zu 0,1%. Plötzlich werden ReLU- und Pooling-Operationen sehr bedeutsam. Daher umfasst unsere Implementierung dedizierte Beschleuniger für die ReLU-Verarbeitung und das Pooling.

Der Chip arbeitet mit einem begrenzten Wärmebudget. Wir mussten sehr vorsichtig sein, wie wir Strom verbrennen. Wir wollen die Menge an Arithmetik maximieren, die wir tun können. Daher haben wir die 32-Bit-Ganzzahladdition gewählt, die 9-mal weniger Energie verbraucht als die Gleitkommaaddition. Und wir haben uns für eine 8-Bit-Ganzzahlmultiplikation entschieden, die auch deutlich weniger Energie verbraucht als andere Multiplikationsoperationen und wahrscheinlich genau genug ist, um gute Ergebnisse zu erzielen. Wie für die Erinnerung. Der Zugriff auf einen externen DRAM ist im Hinblick auf den Stromverbrauch etwa hundertmal teurer als die Verwendung eines lokalen SRAM. Es ist klar, dass wir das lokale SRAM optimal nutzen wollen.

Aus Managementsicht sind hier die Daten, die in einem Artikel von Mark Horowitz veröffentlicht wurden, in dem er kritisch untersuchte, wie viel Energie erforderlich ist, um einen einzelnen Befehl auf einem regulären Ganzzahlprozessor auszuführen. Und Sie sehen, dass der Additionsvorgang nur 0,15% der Gesamtleistung verbraucht. Alles andere ist Overhead für das Management und mehr. Deshalb bemühen wir uns in unserem Design, all dies so weit wie möglich loszuwerden. Was uns wirklich interessiert, ist die Arithmetik.

Hier ist also das Design, das wir fertiggestellt haben. Sie können sehen, dass darin der Hauptplatz von 32 Megabyte SRAM belegt ist, sie befinden sich links, rechts, in der Mitte und unten. Alle Berechnungen werden im oberen Mittelteil durchgeführt. In jedem Zyklus lesen wir 256 Bytes Aktivierungsdaten aus dem SRAM-Array, 128 Bytes Gewichte aus dem SRAM-Array und kombinieren sie in einem 96x96-Array, das 9000 Additionen mit Akkumulation pro Zyklus bei 2 GHz ausführt. Das sind nur 36,8 Billionen. Operationen. Nachdem wir mit dem Skalarprodukt fertig sind, laden wir die Daten hoch, leiten sie durch die dedizierte ReLU, optional durch Ziehen, und legen sie schließlich in den Schreibpuffer, wo alle Ergebnisse aggregiert werden. Und dann schreiben wir 128 Bytes pro Takt zurück in den SRAM. Und das alles passiert ununterbrochen. Wir arbeiten mit skalaren Produkten, während wir frühere Ergebnisse entladen, ziehen und die Ergebnisse zurück in den Speicher schreiben.

Wenn Sie alles mit 2 GHz stapeln, benötigen Sie 1 Terabyte pro Sekunde SRAM-Bandbreite, um den Betrieb zu unterstützen. Und Eisen liefert dies. Ein Terabyte pro Sekunde Bandbreite pro Beschleuniger, zwei Beschleuniger pro Chip - zwei Terabyte pro Sekunde.Der Beschleuniger hat einen relativ kleinen Befehlssatz. Es gibt eine DMA-Leseoperation zum Laden von Daten aus dem Speicher, eine DMA-Schreiboperation zum Hochladen von Ergebnissen zurück in den Speicher. Drei Faltungsanweisungen (Faltung, Entfaltung, inneres Produkt). Zwei relativ einfache Operationen sind die Verschiebung und die elementweise Operation (eltwise). Und natürlich die Stoppoperation, wenn die Berechnungen abgeschlossen sind.Wir mussten einen Compiler für neuronale Netze entwickeln. Wir haben ein von unserem Entwicklungsteam geschultes neuronales Netzwerk in der Form verwendet, in der es in der alten Hardware verwendet wurde. Wenn Sie es für die Verwendung auf einem neuen Beschleuniger kompilieren, führt der Compiler eine Fusion von Ebenen durch, wodurch wir die Anzahl der Berechnungen für jeden Aufruf von SRAM erhöhen können. Es führt auch eine Glättung der Speicherzugriffe durch. Wir führen Kanalauffüllungen durch, um Konflikte zwischen Speicherbänken zu reduzieren. Die Speicherzuweisung berücksichtigt auch SRAM-Banken. Dies ist der Fall, wenn die Konfliktverarbeitung in Hardware implementiert werden könnte. Bei der Softwareimplementierung sparen wir jedoch aufgrund der Komplexität der Software Hardware. Wir fügen auch automatisch DMA-Operationen ein, damit die Daten pünktlich zur Berechnung eintreffen, ohne die Verarbeitung zu stoppen. Am Ende generieren wir den Code,Gewichtet Daten, komprimiert und fügt eine CRC-Prüfsumme hinzu, um die Zuverlässigkeit zu gewährleisten. Das neuronale Netzwerk wird beim Start in den SRAM geladen und ist ständig vorhanden.Um das Netzwerk zu starten, geben Sie die Adresse des Eingabepuffers an, der das neue Bild enthält, das gerade von der Kamera angekommen ist. Stellen Sie die Adresse des Ausgabepuffers ein. Setzen Sie den Zeiger auf das Netzwerkgewicht. lass uns gehen Der Beschleuniger "geht in sich selbst" und durchläuft nacheinander das gesamte neuronale Netzwerk, normalerweise für ein oder zwei Millionen Taktzyklen. Nach Abschluss erhalten Sie eine Unterbrechung und können die Ergebnisse nachbearbeiten.Wenden wir uns den Ergebnissen zu. Unser Ziel war es, 100 Watt zu erreichen. Messungen an Autos, die mit einem vollen Stapel Autopiloten fahren, haben gezeigt, dass wir 72 Watt verbrauchen. Dies ist etwas größer als im vorherigen Projekt, aber eine signifikante Leistungsverbesserung ist eine gute Ausrede. Von diesen 72 Watt werden in neuronalen Netzen etwa 15 Watt verbraucht. Die Kosten für diese Lösung betragen ungefähr 80% der Kosten, die wir zuvor bezahlt haben. In Bezug auf die Leistung haben wir das neuronale Netzwerk (eng) der Kamera, das ich bereits erwähnt habe, mit 35 Milliarden Operationen verwendet, es mit alten Geräten gestartet und 110 Bilder pro Sekunde empfangen. Wir haben dieselben Daten und dasselbe Netzwerk für den neuen FSD-Computer zusammengestellt und können mit allen vier Beschleunigern 2300 Bilder pro Sekunde verarbeiten.Ilon:Ich denke, dies ist vielleichtPetes bedeutendste Folie : Ich habe noch nie an einem Projekt gearbeitet, bei dem die Produktivitätsverbesserung über 3 lag. Es hat also ziemlich viel Spaß gemacht. Im Vergleich zur nvidia Drive Xavier-Lösung liefert der Chip dort 21 Billionen. Operationen, während unser FSDC mit zwei Chips - 144 Billionen. Operationen.Zusammenfassend denke ich, dass wir eine Lösung geschaffen haben, die eine hervorragende Leistung von 144 Billionen liefert. Operationen zum Verarbeiten eines neuronalen Netzwerks. Es hat hervorragende Leistungseigenschaften. Wir haben es geschafft, all diese Produktivität in das Wärmebudget zu stecken, das wir hatten. Auf diese Weise können Sie eine Duplizierungslösung implementieren. Der Computer hat moderate Kosten, und was wirklich wichtig ist, das FSDC bietet ein neues Maß an Sicherheit und Autonomie in Tesla-Fahrzeugen, ohne deren Kosten und Kilometerleistung zu beeinträchtigen. Wir freuen uns alle darauf.Ilon: Wenn Sie Fragen zu Geräten haben, stellen Sie diese jetzt.Der Grund, warum ich Pete gebeten habe, ein detailliertes, viel detaillierteres zu machen, als es die meisten Leute vielleicht gerne in einen Tesla FSD-Computer getaucht hätten, ist folgender. Auf den ersten Blick scheint es unglaublich, wie es passieren kann, dass Tesla, das noch nie zuvor solche Chips entwickelt hatte, den besten Chip der Welt geschaffen hat. Aber genau das ist passiert. Und nicht nur das Beste mit kleinem Vorsprung, sondern das Beste mit großem Abstand. Alle Tesla, die derzeit hergestellt werden, haben diesen Computer. Wir haben vor ungefähr einem Monat von der Nvidia-Lösung für S und X gewechselt und vor ungefähr zehn Tagen Modell 3 gewechselt. Alle produzierten Autos verfügen über die notwendige Hardware und alles, was für ein völlig autonomes Fahren erforderlich ist. Ich werde es noch einmal sagen: Alle Tesla-Autos, die jetzt produziert werden,Sie haben alles, was Sie für ein voll autonomes Fahren benötigen. Sie müssen lediglich die Software verbessern. Später heute können Sie Autos mit einer Version für Entwickler verbesserter autonomer Fahrsoftware fahren. Sie werden es selbst sehen. Fragen.

F: Können Sie andere Aktivierungsfunktionen als ReLU verwenden?Pete: Ja, wir haben ein Sigmoid, zum BeispielF: Vielleicht hat es sich gelohnt, auf einen kompakteren Herstellungsprozess umzusteigen, vielleicht 10 nm oder 7 nm?Pete: Zu der Zeit, als wir mit dem Design begannen, waren nicht alle IPs, die wir erhalten wollten, in 10 nm verfügbar.Ilon: Es ist erwähnenswert, dass wir dieses Design vor ungefähr anderthalb Jahren fertiggestellt und die nächste Generation gestartet haben. Heute sprechen wir nicht über die nächste Generation, aber wir sind schon auf halbem Weg. All das ist für den Chip der nächsten Generation offensichtlich.F: Der Computer ist für die Arbeit mit Kameras ausgelegt. Kann ich es mit Lidar verwenden?Ilon:Lidar ist eine katastrophale Entscheidung, und jeder, der sich auf Lidar verlässt, ist zum Scheitern verurteilt. Zum Scheitern verurteilt. Teuer

Liebe Sensoren, die nicht benötigt werden. Es ist wie eine Menge teurer unnötiger Apps. Ein kleiner ist nichts, aber ein Haufen ist schon ein Albtraum. Das ist dumm, du wirst sehen.F: Können Sie die Auswirkungen des Energieverbrauchs auf die Kilometerleistung bewerten?Pete: Für Modell 3 beträgt der Zielverbrauch 250 Watt pro Meile.Ilon: Kommt auf die Art des Fahrens an. In der Stadt wird der Effekt viel größer sein als auf der Autobahn. Sie fahren eine Stunde in der Stadt und haben eine hypothetische Lösung, die 1 kW verbraucht. Bei Modell 3 verlieren Sie 6 km. Wenn die Durchschnittsgeschwindigkeit 25 km / h beträgt, verlieren Sie 25%. Der Verbrauch des Systems hat einen enormen Einfluss auf die Kilometerleistung in einer Stadt, in der wir glauben, dass es einen großen Teil des Robotax-Marktes geben wird. Daher ist Leistung äußerst wichtig.F:Wie zuverlässig ist Ihre Technologie in Bezug auf IP? Werden Sie IP nicht kostenlos ausgeben?Pete: Wir haben ein Dutzend Patente für diese Technologie angemeldet. Dies ist im Wesentlichen eine lineare Algebra, die Sie meiner Meinung nach nicht patentieren können. (Ilon lacht)F: Ihre Mikroschaltung kann etwas tun, vielleicht alle Gewichte verschlüsseln, damit Ihr geistiges Eigentum im Inneren bleibt, und niemand kann es einfach stehlen.Ilon: Oh, ich würde gerne jemanden treffen, der dies kann. Ich würde ihn sofort einstellen. Dies ist ein sehr schwieriges Problem. Selbst wenn Sie die Daten extrahieren können, benötigen Sie eine große Menge an Ressourcen, um sie irgendwie zu verwenden.Der große nachhaltige Vorteil für uns ist die Flotte. Niemand hat eine Flotte. Die Gewichte werden basierend auf Milliarden von zurückgelegten Kilometern ständig aktualisiert und verbessert. Tesla hat hundertmal mehr Autos mit der für das Training erforderlichen Hardware als alle anderen zusammen. Bis Ende dieses Quartals werden wir 500.000 Fahrzeuge mit 8 Kameras und 12 Ultraschallsensoren haben. In einem Jahr werden wir mehr als eine Million Autos mit FSDC haben. Dies ist nur ein großer Datenvorteil. Dies ähnelt dem großen Vorteil der Google-Suchmaschine, da die Nutzer sie verwenden und Google tatsächlich mit ihren Suchanfragen schulen.Gastgeber:Eine Sache, an die Sie sich bei unserem FSD-Computer erinnern sollten, ist, dass er mit viel komplexeren neuronalen Netzen für eine viel genauere Bilderkennung arbeiten kann. Es ist Zeit darüber zu sprechen, wie wir diese Bilder tatsächlich erhalten und wie wir sie analysieren. Hier haben wir einen Senior Director von AI - Andrey Karpaty, der Ihnen das alles erklären wird. Andrei ist Doktor der Stanford University, wo er Informatik mit Schwerpunkt auf Anerkennung und tiefem Lernen studierte.Ilon: Andrey, warum fängst du nicht einfach an? Viele Ärzte kamen aus Stanford, das spielt keine Rolle. Andrey unterrichtet in Stanford einen Computer-Vision-Kurs, der viel wichtiger ist. Bitte erzähle von dir.

(Die Übersetzung erwies sich als eher nicht schnell, ich weiß nicht, ob ich für den zweiten Teil genug über das Trainingssystem für neuronale Netze habe, obwohl es mir am interessantesten erscheint.)