Eine kleine Einführung:

Die Idee, einen eigenen Kern zu schreiben, kam nach einem Schulseminar über digitale Schaltkreise in der Stadt Tomsk . Bei dieser Veranstaltung wurde eine Einführung in die aktuellen Hardwarebeschreibungssprachen (Verilog HDL und VHDL) sowie in den kleinen SchoolMIPS- Prozessorkern gegeben. Um die Struktur der Kerne zu verstehen, wurde beschlossen, ein eigenes Fahrrad zu erfinden, das dem Entwicklungspfad von schoolMIPS folgt, aber ein anderes Befehlssystem als Grundlage verwendet. Aufgrund der wachsenden Popularität von RISC-V und der Offenheit seines Befehlssystems (MIPS hatte zum Zeitpunkt des Schreibens des Kernels kein offenes Befehlssystem) wurde ein Satz von RISC-V-Anweisungen, nämlich RV32I, für die Entwicklung des zukünftigen Kernels ausgewählt. RV32I verfügt über einen kleinen Satz grundlegender Anweisungen (37 ohne spezielle Anweisungen) und kann bei Bedarf erweitert werden, indem beispielsweise ganzzahlige Multiplikations- und Divisionsanweisungen (RV32M) oder Unterstützung für verkürzte Anweisungen (RV32C) hinzugefügt werden. Außerdem wurde dieses Projekt als pädagogisch konzipiert, sodass beschlossen wurde, die Sichtbarkeit des Kernels zu maximieren, um seine Arbeit effektiv zu demonstrieren.

In Analogie zu schoolMIPS wurden folgende Kernelversionen implementiert:

- Einzelzyklusversion (00_simple_risc_v_cpu).

- Eine Single-Cycle-Version mit Unterstützung für lw / sw-Anweisungen (Wort laden / Wort speichern) (01_simple_risc_v_cpu_lwsw).

- Pipeline-Version (5-stufiges Förderband) (02_pipe_risc_v_cpu).

Derzeit wird die nächste Kernelversion (03_pipe_risc_v_cpu_fc) mit einem vollständigen Satz von RV32I-Befehlen beschrieben (ohne Berücksichtigung einiger spezieller Befehle).

Im Verlauf der Kernelbeschreibung wurden Möglichkeiten zur Verbesserung der Sichtbarkeit der Arbeit, des Debuggens und der Überprüfung erdacht. Derzeit sind folgende Methoden implementiert:

Hinzufügen eines Debug-Text-VGA-Moduls (für zwei Single-Cycle-Kernel-Zweige). Durch die Aufnahme dieses Moduls können Sie gleichzeitig den Wert von 32 Registern auf dem Monitorbildschirm verfolgen, was bei Verwendung der Informationsausgabe für Sieben-Segment-Indikatoren nicht möglich ist. In den folgenden Abbildungen berechnet der Kernel die Leonardo-Zahlen und zeigt Informationen zum entsprechenden Debugging-Modul an.

hex_display und DebugScreenCoreInformationsausgabe zu Sieben-Segment-Indikatoren:

Informationsausgabe auf dem VGA-Display:

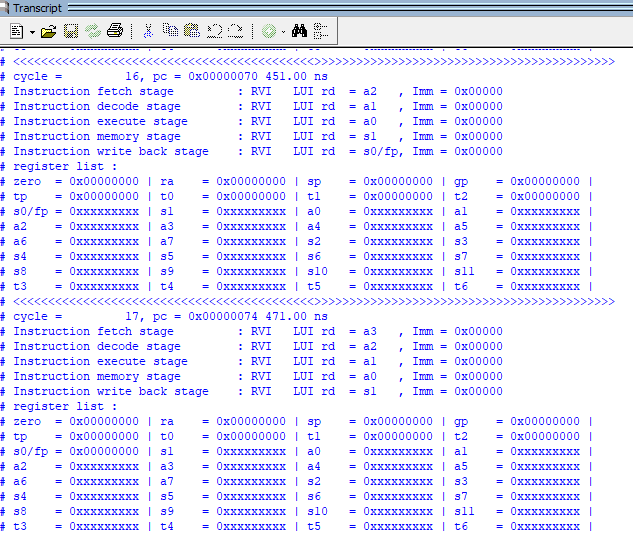

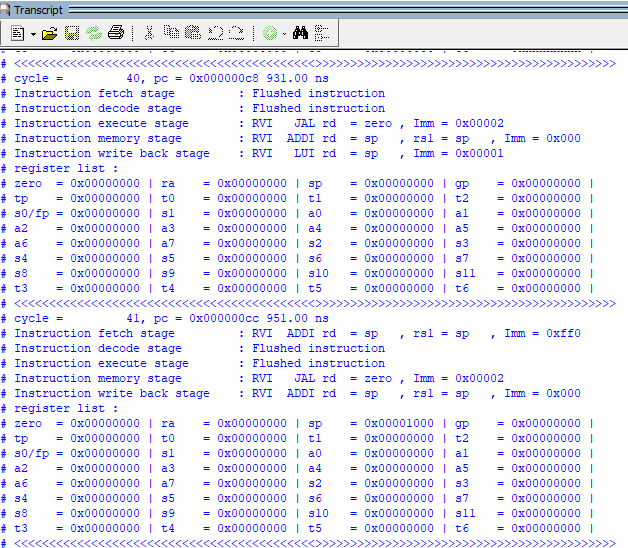

Hinzufügen von Nachrichten zum Simulator-Terminal zum Status der Registerdatei und Ausführen von Anweisungen. Diese Methode ermöglicht es Ihnen, den Betrieb des Kernels in den frühen Entwicklungsstadien besser zu analysieren, ist jedoch nicht immer praktisch.

TerminalInitialisierung der Registerdatei:

SP-Wert ändern:

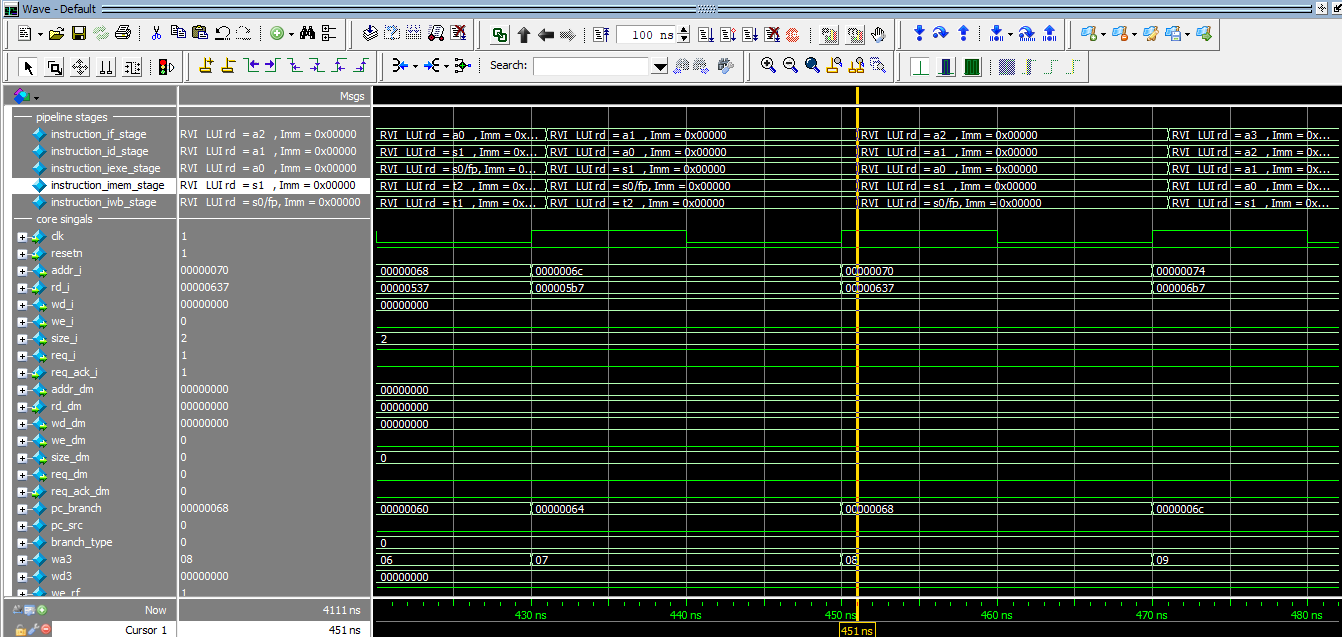

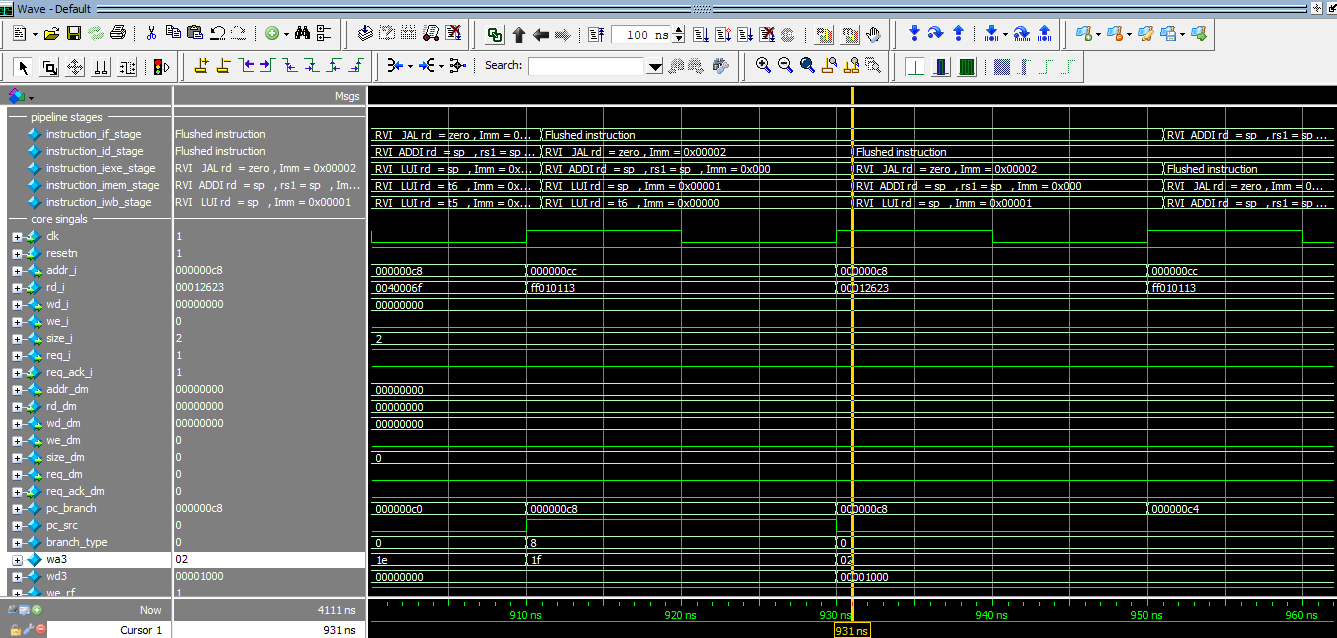

Hinzufügen von Zeichenfolgenvariablen zur Wellenform mit Anzeige ausführbarer Anweisungen. Mit diesen Zeichenfolgenvariablen kann der Entwickler die korrekte Einstellung der Steuersignale in allen Phasen der Pipeline verfolgen.

WellenformInitialisierung der Registerdatei:

SP-Wert ändern:

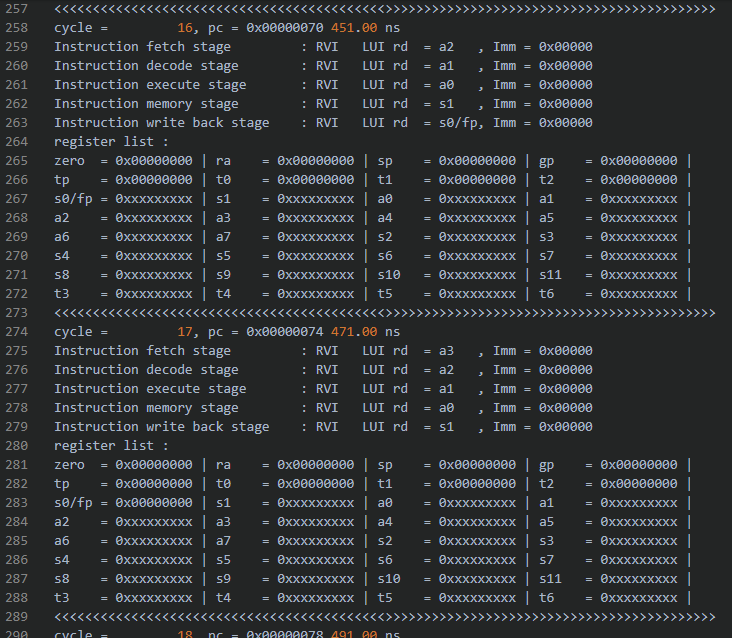

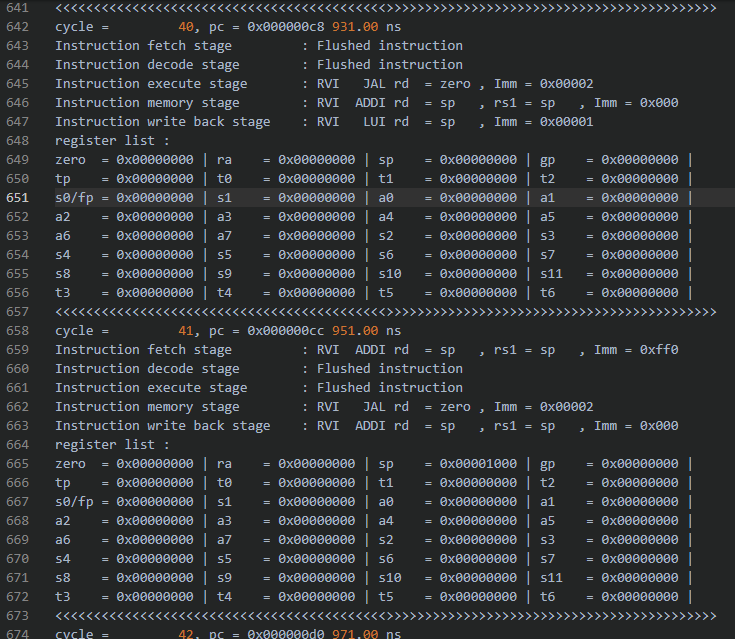

Hinzufügen der Möglichkeit, Debugging-Informationen über den Status des Kernels in eine Textdatei zu schreiben. Der Status der Registerdatei wird in tabellarischer Form dargestellt, und die Anweisungen, die derzeit vom Kernel ausgeführt werden, werden ebenfalls angezeigt. Es ist ein Analogon von 2 Punkten, erlaubt jedoch mehr Manipulationen mit den empfangenen Informationen;

TextdateiInitialisierung der Registerdatei:

SP-Wert ändern:

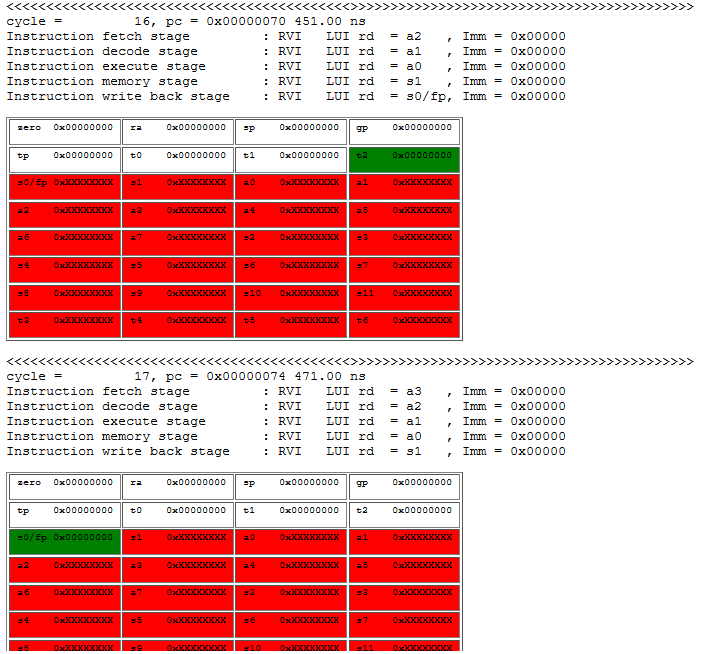

Hinzufügen der Möglichkeit, Debugging-Informationen über den Status des Kernels in eine HTML-Datei zu schreiben. Der Status der Registerdatei wird in tabellarischer Form mit Hinweisen zum Ändern der Werte der Zellen dargestellt, und die Anweisungen, die derzeit vom Kernel ausgeführt werden, werden angezeigt. Es ist ein Analogon zu den Absätzen 2 und 4, aber zusätzlich können Sie bequem eine Änderung der Daten anzeigen. Wie in den folgenden Bildern zu sehen ist, werden die Register rot hervorgehoben, wenn der Registerwert nicht definiert wurde (Register s0 / fp - t6). In Zyklus 17 ändert sich der Wert des Registers s0 / fp und die Zelle wird grün hervorgehoben.

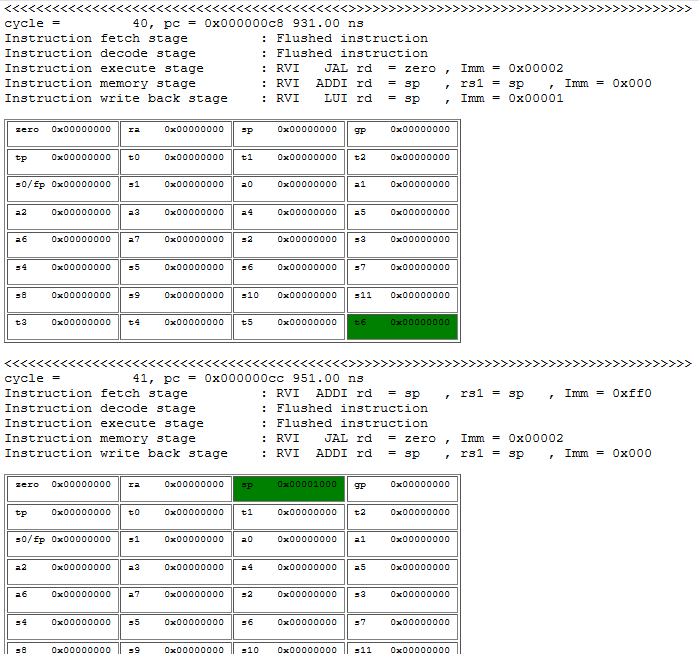

Im Zyklus 41 wird der Wert 0x00010000 in das sp-Register geladen.

HTML-DateiInitialisierung der Registerdatei:

SP-Wert ändern:

Vergleich der Kernelzweige:Derzeit unterstützte Kernel-Anweisungen für verschiedene Zweige:

Unterstützte Peripheriegeräte:

Unterstützte Sprachen zum Schreiben von Programmen:

Erforderliche FPGA-Ressourcen für den Kernel (nf_cpu):

EP4CE22F17C6 (de0_nano):

10M50DAF484C7G (de10_lite):

Projektentwicklung.

Was ist in Zukunft geplant:

- Fügen Sie alle RV32I-Anweisungen hinzu (in der Beschreibungsphase).

- Debugging implementieren;

- Fügen Sie einen DMA (DMA) -Controller hinzu.

- Unterstützung für andere Reifen hinzufügen AXI, Avalon, Wishbone;

- Cache (Cache) Speicher hinzufügen;

- Integration verschiedener Peripheriegeräte (SPI, TWI (I2C), Ethernet (10 Base-T));

- Interrupt-Controller hinzufügen;

- verschiedene Versionen auf andere Debug-Boards portieren;

- Fügen Sie weitere Methoden hinzu, um die Sichtbarkeit des Kernels zu erhöhen.

- Ausführen von RTOS, zum Beispiel Zephyr .

Empfehlungen und Vorschläge für die Entwicklung des Kernels werden ebenfalls akzeptiert.

Link zum Repository: nanoFOX .