Ich begrüße alle.

Ich folgte den Spuren der vorherigen Artikel über logische Analysatoren auf Habré und beschloss, meine "grundlegende" Arbeit zu beenden.

Ich werde ein wenig von weitem anfangen.

Alles begann in den frühen 10er Jahren, als ich in einem Amateurfunkforum zum ersten Mal von Saleae Logic (im Folgenden als Saleae bezeichnet, meine ich einen 8-Kanal-Analysator ohne Schieberegler) erfuhr.

Notiz genommen. Aber bereits mit 13 Jahren bei der Implementierung eines anderen Projekts stieß ich auf die Tatsache, dass ich wirklich einen Logikanalysator mit einem großen Puffer brauchte. Das damals verfügbare Oszilloskop und Hanteck la-5034 lösten das Problem nicht.

Das Hauptmerkmal von Saleae und seinen Klonen ist das Fehlen eines eingebauten Puffers - der gesamte Stream wird sofort auf den PC gejagt und dort gespeichert. Dann kann es analysiert, dekodiert und exportiert werden. Einerseits ist die Betrachtungstiefe praktisch unbegrenzt (Daten können stundenlang gespeichert werden), andererseits beträgt die maximale Abtastfrequenz 24 MHz. In den meisten Fällen ist jedoch aufgrund des programmatischen Charakters der Abtastung ausreichend, dass die Abtastungen einen merklichen "Jitter" aufweisen.

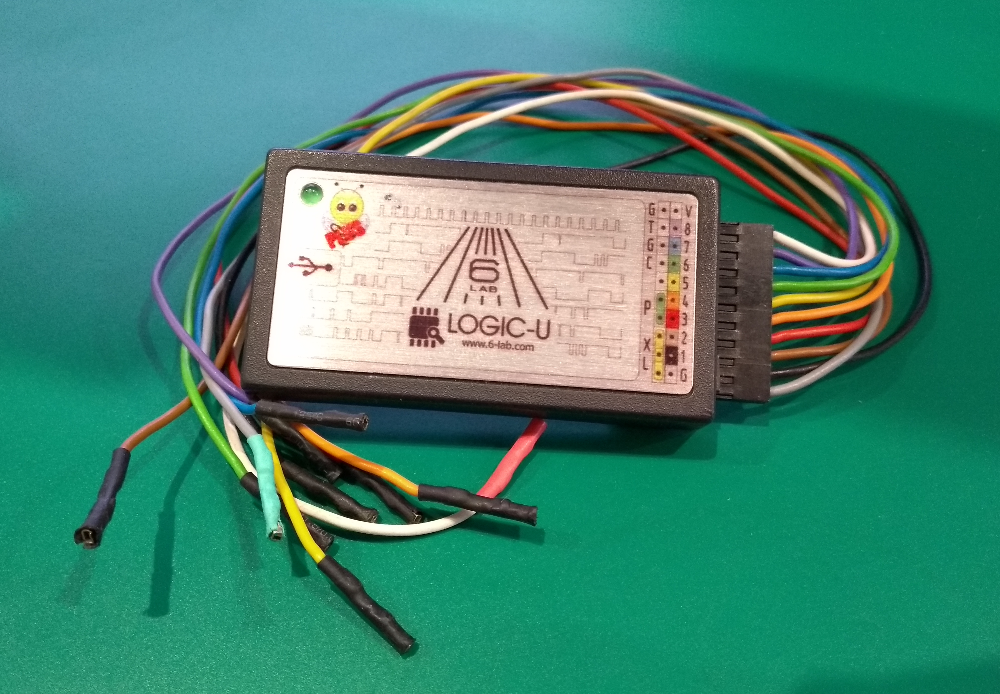

Infolgedessen schickten sie mir sehr schnell, in ungefähr einem Tag, von Kharkov aus dem 6-Labor (jetzt verstorben) über Klone ihren Saleae-Klon mit zwei bereits eingebauten Eepromen, um die Saleae- und Xbee-Typen zu wechseln (die Hardware dieser Geräte ist das gleiche, nur unterscheidet sich das Video: pid, die in eeprom blinken).

Dementsprechend können Sie Software beider Hersteller verwenden.

Zu diesem Zeitpunkt interessierte ich mich für so etwas wie 7Y7C68013A, na ja, oder kürzer als FX2 (obwohl es korrekter als FX2LP ist).

Dies ist ein 8051-kompatibler Mikrocontroller mit einem Hardware-USB2.0-Anschluss und ehrlichen 480 MBit / s.

Zu den Funktionen gehören: 16 KB RAM und die Möglichkeit, Firmware sowohl von einem angeschlossenen I2C-EEPROM als auch über USB herunterzuladen (dort ist kein Flash integriert).

Und dieser MK kann so tun, als wäre er ein beliebiges Gerät am USB-Bus (im Sinne einer Reaktion auf eine VID: PID).

Einige Details aus dem Datenblatt zum Ladevorgang

Betrachten Sie den Fall, wenn ein I2C-EEPROM an das MK angeschlossen ist.

In diesem Fall werden die ersten 8 Bytes daraus analysiert:

Wenn das erste Byte 0xC0 ist (wie in der Saleae-Klon-Firmware), konfiguriert der MK den USB-Port mit der in 1-4 Bytes angegebenen VID: PID und wartet, bis die Firmware über USB heruntergeladen wurde. Abhängig von der geflashten VID: PID MK kann ein anderes Gerät "sein", zumindest Saleae mindestens Xbee mindestens von jemandem. Sehr bequem. Sie können die EEPROMs in einem Stapel löten und mit einem Jumper auswählen.

Wenn das erste Byte jedoch 0xC2 ist, sollte die Firmware für MK ab 9 Byte im EEPROM gespeichert werden, das in den RAM geladen und ausgeführt wird.

Das Speicherformat ähnelt dem von Intel HEX:

Das heißt, die Firmware ist in Blöcke unterteilt, die einzeln in verschiedene Speicherbereiche geladen werden. Dementsprechend macht es keinen Sinn, leere Bereiche zu lagern.

Und jetzt nähern wir uns reibungslos der Hauptfigur unseres Artikels DreamSourseLab.

Ich werde die ganze Geschichte nicht nacherzählen (ich weiß es nicht wirklich und sehe keine tiefere Bedeutung). Dies sind drei Ingenieure, die durch Crowdfunding das Projekt des logischen Traumanalysators (fast) gesehen haben.

Was haben sie getan?

Sie fügten der FX2 eine billige Plisina hinzu - Spartan 6 (vielleicht Saleae ausspioniert).

Und dies sind 16 Kanäle gleichzeitig, dies sind eindeutige Abtastpunkte. Dies ist die Fähigkeit, einzelne Bits zu packen (zwei Leitungen können viermal häufiger abgetastet werden als acht, die Hauptsache ist, innerhalb der USB-Bandbreite zu bleiben). Dies ist eine Gelegenheit, mit einer hohen Frequenz (400 MHz / 4 Kanäle, 200 MHz / 8 Kanäle, 100 MHz / 16 Kanäle) im Puffer zu speichern und ihn dann langsam auf einen PC zu übertragen. Und wenn Sie Sigrok mit seiner leistungsstärksten Basis dekodierter Protokolle verarschen. Im Allgemeinen hat das Projekt ausgelöst - alle sind glücklich. Und unter Berücksichtigung der Tatsache, dass die Autoren den Stream-Modus gespeichert haben (ohne im internen Puffer zu speichern), haben wir einen logischen Traumanalysator erhalten (na ja, fast, weil ich sofort 32 Kanäle und FX3 wollte).

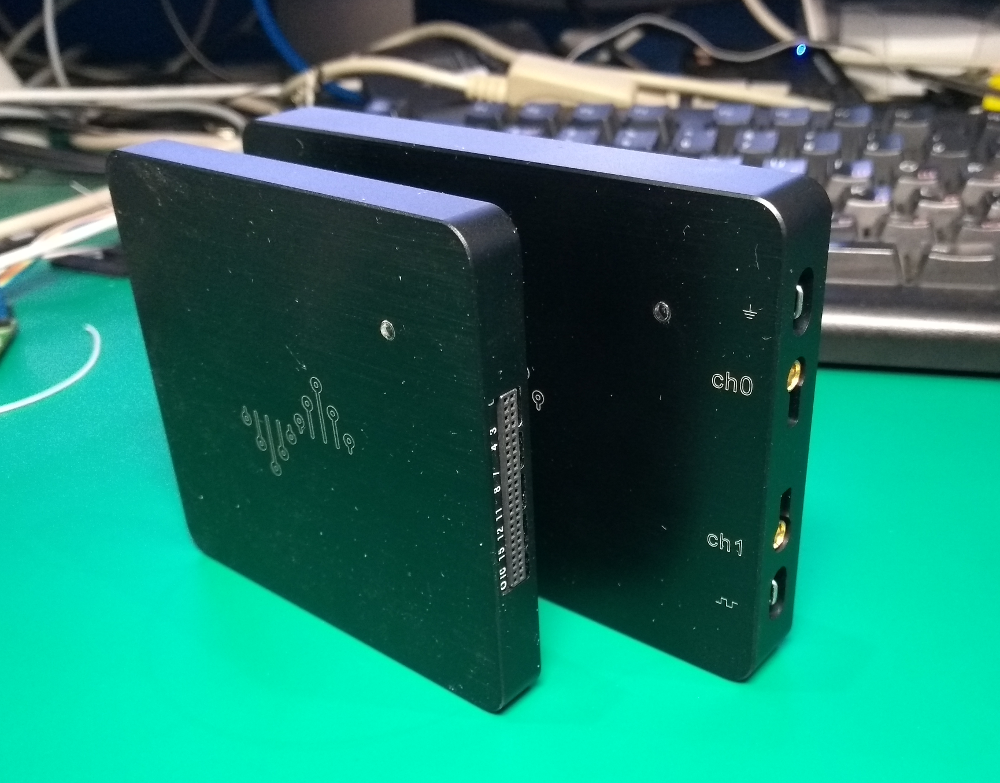

So erschien DSLogicPro. Strikte schwarze Aluminiumbox mit USB-C-Anschluss.

Und dann haben die Ingenieure das Geschäft getroffen. Und sie veröffentlichten Boxen mit den Namen DSLogicBase und DSLogicPlus (wie ich es verstehe, um die Welt durch chinesische Standorte zu erobern) sowie DSCope (wir hängen ein paar 8-Bit-ADCs auf und jetzt haben wir ein Zweikanal-Oszilloskop).

Um diesen Prozess unter strenger Kontrolle zu halten, haben wir das Board-Layout ein wenig geändert. Das heißt, DSLogicPlus und DSLogicPro sind elektrisch und funktional identisch, aber der SRAM hängt am Stecker an den anderen Pins (dies ist auf dem Bild der Spuren deutlich zu sehen). Ich vermute, dass an anderen Stellen Verbesserungen vorgenommen wurden.

Übrigens wurde eine sehr wertvolle Überarbeitung des Kabels zum Anschluss der untersuchten Signale vorgenommen. Wenn in Pro alle 16 Leitungen gleichzeitig mit einem breiten Anschluss verbunden sind, wurden in Plus alle Kabel in Gruppen von 4 Kanälen unterteilt, die separat angeschlossen werden können. Nun, die Kabel selbst sind kurz, koaxial und anstelle des Schneidens (wo das Koaxialkabel in ein separates Signal und gemeinsame Drähte unterteilt ist) befindet sich ein kleiner Schal mit einem Filter.

Und so bestellte ich im Frühjahr 17 DSLogicBase in China (leider wusste ich nicht alles, worüber ich damals schrieb). Sie schickten mir alles, aber ich freute mich auf den 64-Megasample-Puffer, drehte das Board auf und sah eine leere Stelle. Das schnelle Erhöhen des Butchu brachte 50% der Kosten zurück. Und dann begann er sich mit der Frage zu befassen, meine Basis in Plus zu verwandeln. Dies ist genau der Unterschied zwischen Base und Plus - das Vorhandensein eines separaten Puffers. Die Basis verwendet im FPGA integrierten Speicher.

Im Sommer 17, auf dem Weg zur Arbeit und zurück für eine halbe Stunde im MCC-Zug, studierte ich dieses Thema. Und ziemlich schnell wurde klar, dass die Unterschiede nur im versiegelten SRAM und einem Paar Bytes EEPROM-Firmware lagen.

Ein wenig darüber, was sich im Verzeichnis DSView / res befindet

Dort haben wir eine Reihe von Dateien mit den Erweiterungen bin und fw.

bin - das ist Firmware für Plisina. Sie werden zum Zeitpunkt des Programmstarts über fx2 geladen.

fw sind binäre Firmware-Dateien für FX2.

Wenn Sie alle fw-Dateien vergleichen, stellt sich heraus, dass sie sich alle nur im PID-Byte an der Adresse am Ende unterscheiden.

Das heißt, die Unterschiede zwischen allen Geräten sind genau dies und die Firmware des Steckers (der, wie gesagt, zum Zeitpunkt der Initialisierung geladen wird).

Ein Vergleich von fw mit dem, was im EEPROM geschrieben ist (natürlich habe ich den Speicherauszug sofort von meinem Analysegerät ausgegeben), ergab, dass die bereitgestellte Firmware hier ist.

Wenn Sie die Firmware vom EEPROM bereitstellen, stimmen sie (soweit ich mich erinnere) überein (für Softwareversion 0.96).

Wie bereits auf dem Hub geschrieben, müssen Sie nur den Speicher löten und 2 Bytes in der Firmware ändern (im Header und dann weiter in der Firmware).

In ähnlicher Weise wird DSCope fertiggestellt, wir verdoppeln den Speicher und ändern die PID im EEPROM.

Es gibt noch eine Nuance.

Mit der Veröffentlichung neuer Softwareversionen (0.96-0.99) wurden die unterstützten Hardwaremodelle hinzugefügt und die PID dieser Modelle geändert.

Also habe ich so ein Tablet bekommen:

Darüber hinaus wurde in der Firmware unter der Adresse 0x20 ein Hinweis für die Pro-Version 5, für Base und Plus 6 angezeigt. Höchstwahrscheinlich handelt es sich nur um die Version der Leiterplatte.

Übrigens gibt es noch einen anderen Weg, um zu verfeinern. Keine Neuprogrammierung des EEPROM erforderlich. Es reicht aus, SRAM zu löten und dann beim Kompilieren von libsigrok4DSL eine Korrektur an der Datei libsigrok4DSL / hardware / DSL / dsl.h vorzunehmen:

In der Struktur, die die statische Konstantenstruktur des Geräts beschreibt, unterstützt DSL_profile_DSLogic [],

Ändern Sie an der Stelle, an der DSLogic PLus und Base beschrieben werden, die PID-Felder, sodass das Programm den Eindruck hat, dass es über Base PID 20 und Plus PID 21 verfügt.

319 {0x2A0E, 0x0020, "DreamSourceLab", "DSLogic PLus", NULL, 320 "DSLogicPlus.fw", 321 "DSLogicPlus.bin", 322 "DSLogicPlus.bin", 323 {CAPS_MODE_LOGIC, 324 CAPS_FEATURE_VTH | CAPS_FEATURE_BUF, 325 (1 << DSL_STREAM20x16) | (1 << DSL_STREAM25x12) | (1 << DSL_STREAM50x6) | (1 << DSL_STREAM100x3) | 326 (1 << DSL_BUFFER100x16) | (1 << DSL_BUFFER200x8) | (1 << DSL_BUFFER400x4), 327 SR_MB(256), 328 0, 329 DSL_BUFFER100x16, 330 0, 331 0, 332 DSL_STREAM20x16, 333 SR_MHZ(1), 334 SR_Mn(1), 335 0, 336 0} 337 }, 338 339 {0x2A0E, 0x0021, "DreamSourceLab", "DSLogic Basic", NULL, 340 "DSLogicBasic.fw", 341 "DSLogicBasic.bin", 342 "DSLogicBasic.bin", 343 {CAPS_MODE_LOGIC, 344 CAPS_FEATURE_VTH, 345 (1 << DSL_STREAM20x16) | (1 << DSL_STREAM25x12) | (1 << DSL_STREAM50x6) | (1 << DSL_STREAM100x3) | 346 (1 << DSL_BUFFER100x16) | (1 << DSL_BUFFER200x8) | (1 << DSL_BUFFER400x4), 347 SR_KB(256), 348 0, 349 DSL_STREAM20x16, 350 0, 351 0, 352 DSL_STREAM20x16, 353 SR_MHZ(1), 354 SR_Mn(1), 355 0, 356 0} 357 },

Und Ihre Analyseversion mit dieser Version von DSView funktioniert so, als hätten Sie ein echtes Plus.

In der Zwischenzeit werde ich von einem Haufen Spartan6 + FX3 + DSView träumen.