Irgendwie kann ich meine Gedanken nicht kurz ausdrücken. Im vergangenen Herbst gab es den Wunsch, detaillierter über die von mir beherrschte PSoC-Architektur zu berichten, was zu einer Reihe von Artikeln darüber führte. Jetzt bin ich an der Vorbereitung der Hardware für unseren Redd-Remote-Debugging-Komplex beteiligt, der hier beschrieben

wurde , und ich möchte die gesammelten Erfahrungen in Textform wegwerfen. Ich bin mir noch nicht sicher, aber es scheint mir, dass es wieder nicht nur ein Artikel ist, sondern ein Zyklus. Erstens werde ich auf diese Weise die entwickelten Entwicklungsmethoden dokumentieren, die für jemanden nützlich sein können, sowohl bei der Arbeit mit dem Komplex als auch im Allgemeinen, und zweitens ist das Konzept noch neu und nicht ganz etabliert. Vielleicht erscheinen während der Diskussion von Artikeln einige Kommentare, aus denen man etwas ziehen kann, um es zu erweitern (oder sogar zu ändern). Deshalb fahren wir fort.

Lange Einführung

Ich mag es nicht wirklich zu theoretisieren und bevorzuge es, einige praktische Dinge auf einmal darzulegen. Aber am Anfang des ersten Artikels, ohne eine lange Einführung irgendwo. Darin begründe ich den aktuellen Entwicklungsansatz. Und alles dreht sich um eines: Arbeitsstunden sind eine sehr teure Ressource. Und die Angelegenheit betrifft nicht nur die für das Projekt vorgesehenen Bedingungen. Er ist körperlich teuer. Wenn es für die Entwicklung des Endprodukts ausgegeben wird, was können Sie nirgendwo ohne es tun? Aber wenn es für Hilfsarbeit ausgegeben wird, ist dies meiner Meinung nach schlecht. Ich erinnere mich, dass ich einen Streit mit einem Entwickler hatte, der sagte, dass er, nachdem er selbst Prototypen hergestellt hatte, Geld für seine einheimische Firma sparen würde. Ich machte das Argument, dass er ungefähr 3 Tage für die Herstellung aufwenden würde. Das sind 24 Mannstunden. Wir nehmen sein Gehalt für diese Stunden, addieren die Sozialsteuer, die "der Arbeitgeber zahlt", sowie die Miete des Büros für diese Stunden. Und wir sind überrascht zu sehen, dass Sie bei der Bestellung von Boards nebenbei niedrigere Kosten erzielen können. Aber das bin ich, ich übertreibe. Wenn Arbeitskosten vermieden werden können, sollten sie im Allgemeinen vermieden werden.

Was ist die Entwicklung der "Firmware" für den Redd-Komplex? Dies ist ein Hilfsjob. Das Hauptprojekt wird für immer glücklich leben, es sollte so effizient wie möglich durchgeführt werden, mit ausgezeichneter Optimierung usw. Es ist jedoch verschwenderisch, Zeit und Energie für Hilfsmittel aufzuwenden, die nach der Entwicklung in das Archiv gelangen. Mit Blick auf dieses Prinzip wurde die Entwicklung von Redd-Geräten durchgeführt. Wenn möglich, werden alle Funktionen als Standard implementiert. Die SPI-, I2C- und UART-Busse sind auf Standard-FTDI-Mikroschaltungen implementiert und werden über Standardtreiber ohne Schnickschnack programmiert. Die Verwaltung von Rollen erfolgt im Format eines virtuellen COM-Ports. Es kann modifiziert werden, aber zumindest wurde alles getan, damit ein solcher Wunsch nicht entsteht. Im Allgemeinen wird alles Standard, wenn möglich, auf standardmäßige Weise implementiert. Von Projekt zu Projekt müssen Entwickler lediglich schnell typischen Code für den PC schreiben, um auf diese Busse zugreifen zu können. Die Entwicklungstechnik in C ++ sollte für diejenigen offensichtlich sein, die Programme für Mikrocontroller entwickeln (wir werden in einem anderen Artikel auf einige technische Details eingehen).

Aber FPGA steht allein in der Anlage. Es wird dem System für Fälle hinzugefügt, in denen nicht standardmäßige Protokolle mit hohen Leistungsanforderungen implementiert werden müssen. Wenn diese benötigt werden, müssen Sie die "Firmware" dafür machen. Hier geht es um die FPGA-Programmierung, und ich möchte speziell darauf eingehen, nur alle zum gleichen Zweck - um die Entwicklungszeit von Hilfsmitteln zu verkürzen.

Um den Leser nicht zu verwirren, werde ich den Gedanken in einem Rahmen formulieren:

Es ist nicht erforderlich, in jedem Projekt eine Entwicklung für FPGAs durchzuführen. Wenn genügend Buscontroller direkt an den Zentralprozessor angeschlossen sind, um mit dem Zielgerät zu arbeiten, sollten Sie diese verwenden.

FPGA wurde dem Komplex für die Implementierung von nicht standardmäßigen Protokollen hinzugefügt.

Blockdiagramm des Komplexes

Schauen wir uns das Blockdiagramm des Komplexes an

Am Ende der Schaltung befindet sich ein „Taschenrechner“. Eigentlich ist dies ein Standard-PC mit Linux. Entwickler können reguläre Programme in C, C ++, Python usw. schreiben, die vom Computer ausgeführt werden. Im oberen rechten Teil befinden sich die Standardanschlüsse von Standardreifen. Auf der linken Seite befindet sich ein Schalter für Standardgeräte (SPI Flash, SD-Karte und mehrere Halbleiter-Halbleiterrelais, mit denen beispielsweise Tastendrücke simuliert werden können). Und im Zentrum steht genau der Teil, mit dem die Arbeit in dieser Artikelserie berücksichtigt werden soll. Sein Herzstück ist ein FPGA der FPGA-Klasse, von dem gerade Linien ausgehen (können als Differenzpaare oder normale ungepufferte Leitungen verwendet werden), GPIO-Leitungen mit konfigurierbarem Logikpegel sowie ein über einen ULPI-Chip implementierter USB 2.0-Bus.

Fortsetzung der Einführung zum FPGA-Programmieransatz

Bei der Entwicklung einer Hochleistungssteuerungslogik für FPGAs wird Seine Majestät normalerweise von einer Zustandsmaschine als erste Geige gespielt. Auf den Maschinen ist es möglich, eine schnelle, aber komplexe Logik zu implementieren. Andererseits wird ein Automat langsamer entwickelt als ein Programm für einen Prozessor, und seine Modifikation ist ein anderer Prozess. Es gibt Systeme, die die Entwicklung und Wartung von Maschinen vereinfachen. Eine davon wurde sogar von unserer Firma entwickelt, aber der Entwurfsprozess für jede Art von komplexer Logik ist nicht schnell. Wenn das entwickelte System das Endprodukt ist, ist es sinnvoll, eine gute Steuerungsmaschine vorzubereiten, zu entwerfen und Zeit für deren Implementierung aufzuwenden. Wie bereits erwähnt, ist die Entwicklung für Redd eine Nebenaufgabe. Es soll den Prozess erleichtern, nicht erschweren. Daher wurde beschlossen, dass die Entwicklung nicht automatisch erfolgt, sondern durch Prozessorsysteme.

Andererseits wurde bei der Entwicklung der Hardware die bislang modernste Option, FPGA mit dem ARM-Kern, abgelehnt. Erstens aus Preisgründen. Ein Cyclone V SoC-basiertes Prototyp-Board ist mäßig teuer, aber seltsamerweise ist ein separates FPGA viel teurer. Höchstwahrscheinlich wird der Preis für Prototyping-Boards gesenkt, um Entwickler zur Verwendung von FPGA-Daten zu verleiten, und die Boards werden einzeln verkauft. Die Serie muss einzelne Chips nehmen. Darüber hinaus gibt es aber auch eine "Sekunde". Zweitens, als ich mit Cyclone V SoC experimentierte, stellte sich heraus, dass dieses Prozessorsystem nicht so ist und produktiv ist, wenn es um den Einzelzugriff auf Ports geht. Batch - ja, da ist die Arbeit schnell. Und bei Einzelzugriffen mit einer Taktfrequenz des Prozessorkerns von 925 MHz können Sie mit einer Frequenz von einigen Megahertz auf die Ports zugreifen. Ich schlage allen vor, die Standardfunktion zum Eingeben von Daten in das FIFO des UART-Blocks aufzurufen, die den Warteschlangenüberlauf überprüft, sie jedoch aufruft, wenn die Warteschlange offensichtlich leer ist, dh nichts stört die Operationen. Meine Produktivität stieg von einer Million auf fünfhunderttausend Anrufe pro Sekunde (natürlich verlief die Arbeit mit dem Speicher mit normaler Geschwindigkeit, alle Caches wurden optimiert, selbst die Funktionsvariante, bei der FIFO nicht auf Überlauf überprüft wurde, funktionierte schneller, nur die diskutierte Funktion hat sich reichlich gemischt Schreiben und Lesen von Ports). Das ist FIFO! Tatsächlich wurde FIFO erfunden, um Daten dort abzulegen und zu vergessen! Schnell beenden! Und nicht mit Leistung, weniger als ein Mega-Betrieb pro Sekunde bei einer Prozessorfrequenz von 925 MHz ...

Latenz ist schuld. Zwischen dem Prozessorkern und dem Gerät befinden sich drei oder mehr Brücken. Darüber hinaus hängt die Geschwindigkeit des Zugriffs auf die Ports vom Kontext ab (mehrere Datensätze in einer Reihe werden schnell ausgeführt, aber der erste Lesevorgang stoppt den Prozess, bis die zwischengespeicherten Daten vollständig entladen sind. Zu viele Datensätze in einer Reihe werden ebenfalls langsamer, da die Schreibpuffer erschöpft sind). Schließlich ergab die Untersuchung der im Debugging-Puffer akkumulierten Traces, dass die

Cortex A- Architektur aufgrund des komplexen Cache-Systems denselben Teil für eine unterschiedliche Anzahl von Taktzyklen ausführen kann. Zusammenfassend wurde unter Berücksichtigung all dieser Faktoren (Preis, Leistungseinbußen bei der Arbeit mit dem Gerät, Instabilität der Zugriffsgeschwindigkeit auf das Gerät, allgemeine Abhängigkeit vom Kontext) beschlossen, einen solchen Chip nicht in den Komplex einzubauen.

Experimente mit dem PSoC von Cypress zeigten, dass der

Cortex M- Kern dort besser vorhersehbare und wiederholbare Ergebnisse liefert, die logische Kapazität und die maximale Betriebsfrequenz dieser Steuerungen jedoch nicht den technischen Spezifikationen entsprachen und daher auch verworfen wurden.

Es wurde beschlossen, ein kostengünstiges typisches Cyclone IV-FPGA zu installieren und die Verwendung eines synthetisierten NIOS II-Prozessorkerns zu empfehlen. Nun, und wenn nötig - um die Entwicklung mit anderen Methoden durchzuführen (automatische Maschinen, harte Logik usw.).

Ich werde diesen Absatz separat erwähnen (und sogar hervorheben), dass der Hauptprozessor des Komplexes x86 (x64) ist. Er ist der zentrale Prozessor des Systems. Darauf wird die Hauptlogik des Komplexes ausgeführt. Das Prozessorsystem, auf das weiter unten eingegangen wird, ist so ausgelegt, dass es einfach die Logik des Betriebs des Geräts liefert, das im FPGA "geflasht" ist. Darüber hinaus wird dieses Gerät nur verkauft, wenn die Entwickler nicht über genügend Vollzeitmodule verfügen, die direkt an den Zentralprozessor angeschlossen sind.

Der Prozess des Entwickelns und Debuggens von "Firmware"

Wenn auf dem Redd-Komplex Linux ausgeführt wird, bedeutet dies nicht, dass die Entwicklung in diesem Betriebssystem durchgeführt werden sollte. Redd ist ein Remote-Executor, und die Entwicklung sollte unabhängig vom Betriebssystem auf Ihrem Computer durchgeführt werden. Wer Linux hat, ist umso einfacher, aber wer ist an Windows gewöhnt (Früher mochte ich WIN 3.1 nicht sehr, aber ich musste arbeiten, aber irgendwann, als WIN95 OSR2, habe ich mich daran gewöhnt, und jetzt ist es nutzlos, damit umzugehen, es ist einfacher zu akzeptieren). können diese weiterhin die Entwicklung darin führen.

Da meine Freundschaft mit Linux nicht geklappt hat, werde ich keine schrittweisen Anweisungen zum Einrichten der Umgebung geben, sondern mich auf allgemeine Worte beschränken. Wer mit diesem Betriebssystem arbeitet, wird dafür ausreichen, und für den Rest ... Glauben Sie mir, es ist einfacher, Systemadministratoren zu kontaktieren. Am Ende habe ich genau das getan. Aber trotzdem.

Sie sollten Quartus Prime Programmer und Tools derselben Version wie Ihre Entwicklungsumgebung herunterladen und installieren. Wenn die Versionen nicht übereinstimmen, kann es zu Überraschungen kommen. Ich habe den ganzen Abend damit verbracht, diese Tatsache zu verstehen. Laden Sie daher einfach das Tool derselben Version wie die Entwicklungsumgebung herunter.

Geben Sie nach der Installation das Verzeichnis ein, in dem das Programm installiert wurde, das Unterverzeichnis bin. Im Allgemeinen sollte die wichtigste Datei jtagconfig sein. Wenn Sie es ohne Argumente ausführen (ich habe übrigens beharrlich die Eingabe von ./jtagconfig verlangt und nur so), wird eine Liste der im System verfügbaren Programmierer und der damit verbundenen FPGAs angezeigt. Es sollte einen USB-Blaster geben. Und das erste Problem, das das System aufwirft, sind nicht genügend Zugriffsrechte, um mit USB zu arbeiten. Wie man es löst, ohne auf sudo zurückzugreifen, wird hier beschrieben:

radiotech.kz/threads/nastrojka-altera-usb-blaster-v-ubuntu-16-04.1244Aber hier ist eine Liste der Geräte angezeigt. Jetzt solltest du schreiben:

./jtagconfig --enableremote <password>

Danach wird der Server gestartet, auf den von überall im Netzwerk zugegriffen werden kann.

Alles wäre in Ordnung, aber die System-Firewall lässt niemanden diesen Server sehen. Eine Überprüfung bei Google ergab, dass für jeden Linux-Typ (von dem es viele gibt) die Ports in der Firewall auf ihre eigene Weise geöffnet werden und so viele Zaubersprüche gesprochen werden müssen, dass ich lieber die Administratoren kontaktiere.

Wenn jtagd nicht in autorun registriert wurde, wird Ihnen beim Öffnen des Remotezugriffs mitgeteilt, dass es unmöglich ist, ein Kennwort festzulegen. Um dies zu verhindern, muss jtagd nicht über jtagconfig selbst, sondern davor gestartet werden.

Im Allgemeinen geht es beim Schamanismus um Schamanismus. Lassen Sie mich nur die These korrigieren:

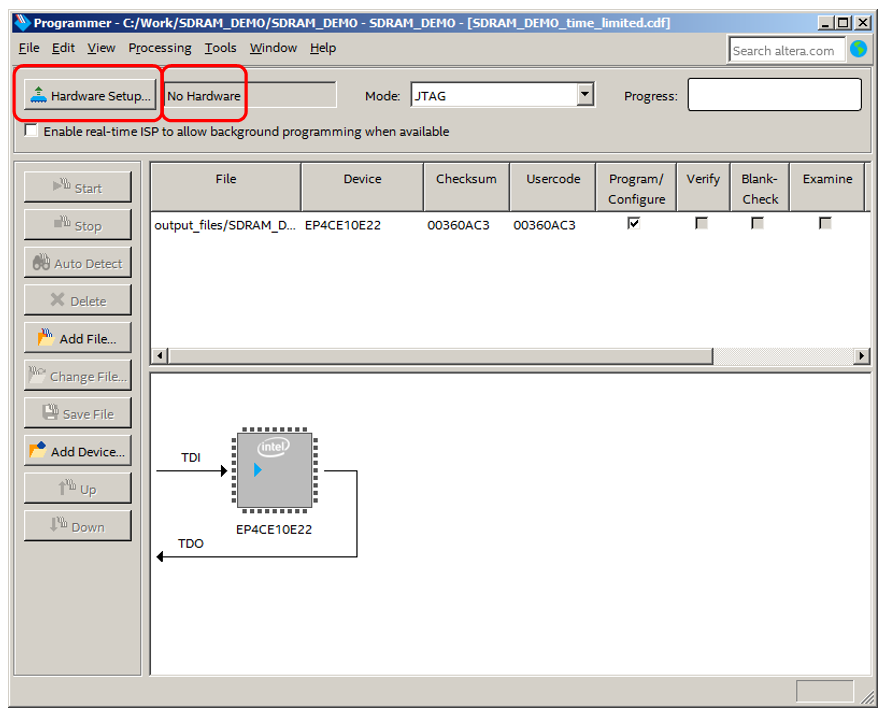

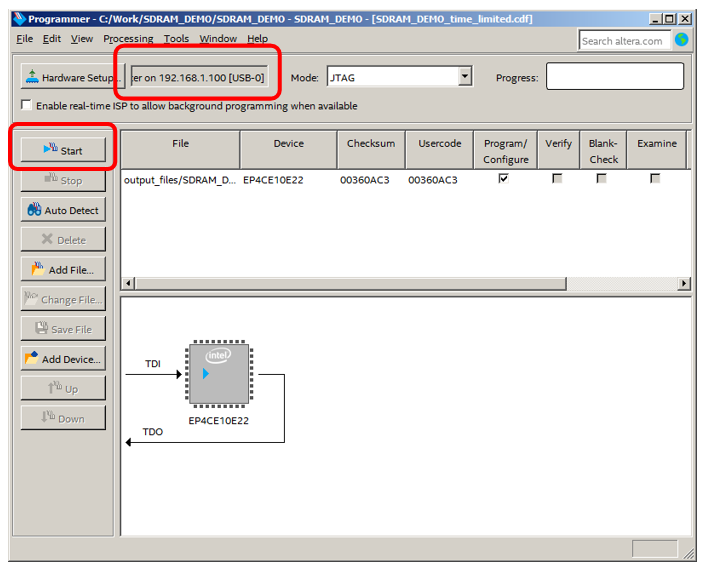

Es gibt natürlich einen ähnlichen Pfad, der über die GUI-Oberfläche verläuft, aber es ist logischer, alles im Stapel zu erledigen. Daher habe ich eine Batch-Version beschrieben. Wenn alle diese Arbeiten abgeschlossen sind (und die Systemadministratoren sie abgeschlossen haben), starten wir den Programmierer auf unserem Computer und sehen eine Meldung über den Mangel an Ausrüstung. Klicken Sie auf Hardware-Setup:

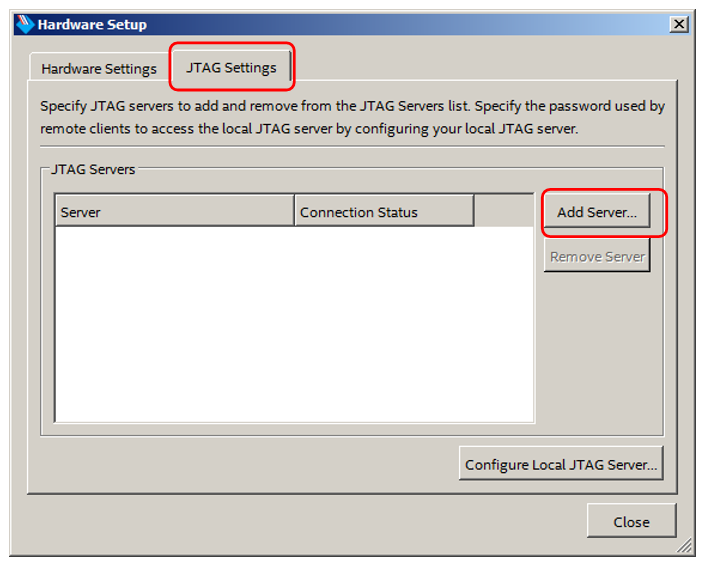

Gehen Sie zur Registerkarte JTAG-Einstellungen und klicken Sie auf Server hinzufügen:

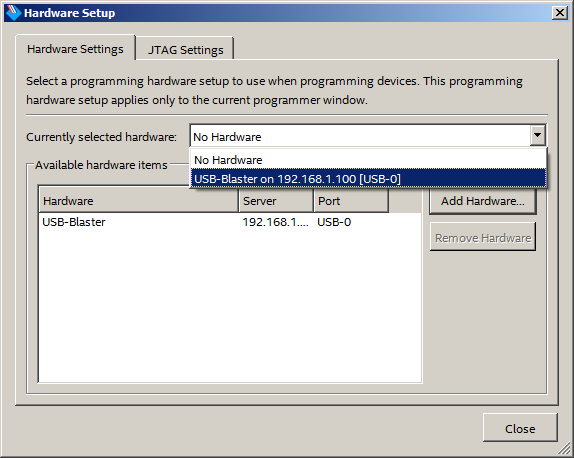

Wir geben die Netzwerkadresse von Redd (für mich 192.168.1.100) und das Passwort ein:

Wir stellen sicher, dass die Verbindung erfolgreich war.

Ich habe drei Maiferien verbracht, um dies zu erreichen, und dann haben die Administratoren alles entschieden.

Wechseln Sie zur Registerkarte Hardwareeinstellungen, öffnen Sie die Dropdown-Liste und wählen Sie dort den Remote-Programmierer aus:

Alles, jetzt kann es verwendet werden. Die Schaltfläche Start ist entsperrt.

Die erste "Firmware"

Na dann. Damit der Artikel einen echten praktischen Wert hat, analysieren wir die einfachste „Firmware“, die mit den oben genannten Methoden erstellt wurde. Das Einfachste, was ich wirklich für den Komplex implementieren konnte, ist ein Test des SDRAM-Chips. Hier an diesem Beispiel und üben.

Es gibt eine Reihe von Amateurkernen, die SDRAM unterstützen, aber alle schalten sich irgendwie schwierig ein. Und alle Tricks zu erklären, ist Arbeit. Wir werden versuchen, vorgefertigte Lösungen zu verwenden, die in das NIOS II-Computersystem eingefügt werden können, daher werden wir den Standard-SDRAM-Controller-Core verwenden. Der Kern selbst ist im Dokument

Embedded Peripherals IP User Guide beschrieben , und in der Beschreibung ist viel Platz für die Taktverschiebung des SDRAM relativ zum Kerntakt vorgesehen. Es werden komplexe theoretische Berechnungen und Formeln angegeben, aber was zu tun ist, wird nicht besonders berichtet. Was zu tun ist, finden Sie im Dokument

Verwenden des SDRAM auf dem DE0-Board von Altera mit Verilog Designs . Im Verlauf der Analyse werde ich das Wissen aus diesem Dokument anwenden.

Ich werde in der kostenlosen Version von Quartus Prime 17.0 entwickeln. Ich konzentriere mich darauf, da sie mir während der Montage mitteilen, dass in Zukunft der Kern des

SDRAM-Controllers aus der kostenlosen Version herausgeschmissen wird. Wenn dies in Ihrer Entwicklungsumgebung bereits geschehen ist, stört es niemanden, die kostenlose 17. Version herunterzuladen und auf einer virtuellen Maschine zu installieren. Die Hauptarbeit wird überall dort erledigt, wo Sie es gewohnt sind, und die Firmware für Redd mit SDRAM befindet sich in der 17. Version. Nun, wenn Sie die kostenlosen Optionen verwenden. Noch drohte niemand, es aus bezahlten herauszuwerfen. Aber ich war abgelenkt. Erstellen Sie ein neues Projekt:

Nennen wir es SDRAM_DEMO. Der Name sollte nicht vergessen werden: Ich werde eine superschnelle Entwicklung durchführen, daher sollte sich das Prozessorsystem selbst auf der obersten Ebene befinden, ohne Verilog-Schichten. Dazu muss der Name des Prozessorsystems mit dem Namen des Projekts übereinstimmen. Also erinnere dich daran.

Wenn wir in wenigen Schritten mit den Standardwerten übereinstimmen, entscheiden wir uns für einen Kristall. Wir wählen das im Komplex verwendete EP4CE10E22C7 aus.

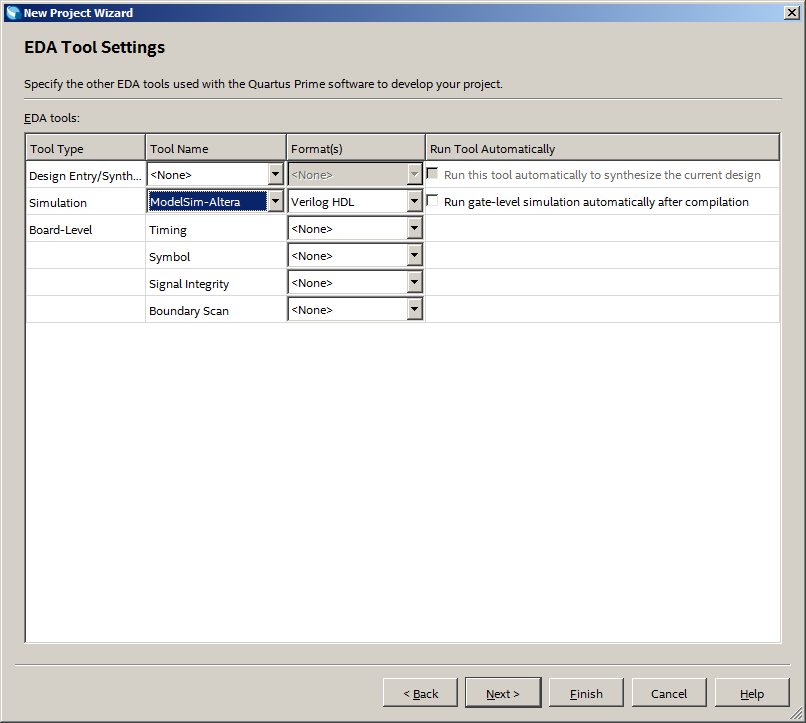

Im nächsten Schritt wähle ich aus Gewohnheit die Modellierung in ModelSim-Altera. Heute werden wir nichts modellieren, aber alles kann nützlich sein. Es ist besser, eine solche Gewohnheit zu entwickeln und ihr zu folgen:

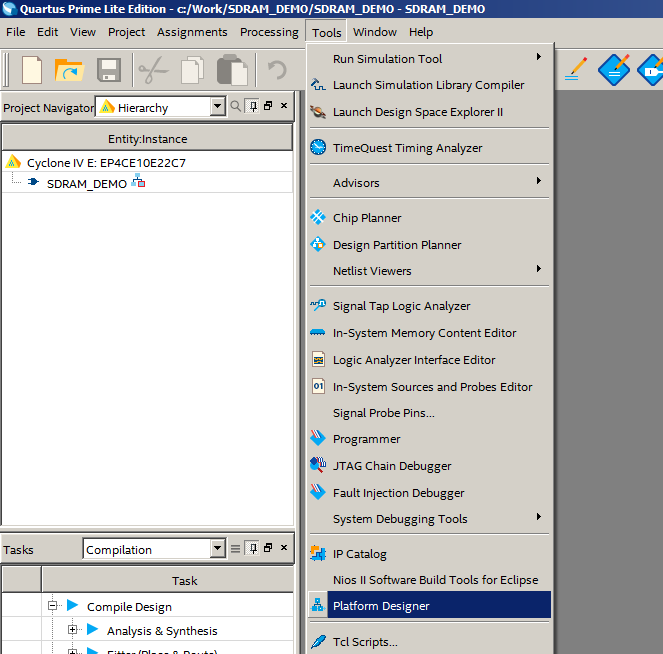

Das Projekt wird erstellt. Gehen Sie sofort zur Erstellung des Prozessorsystems (Tools-> Platform Designer):

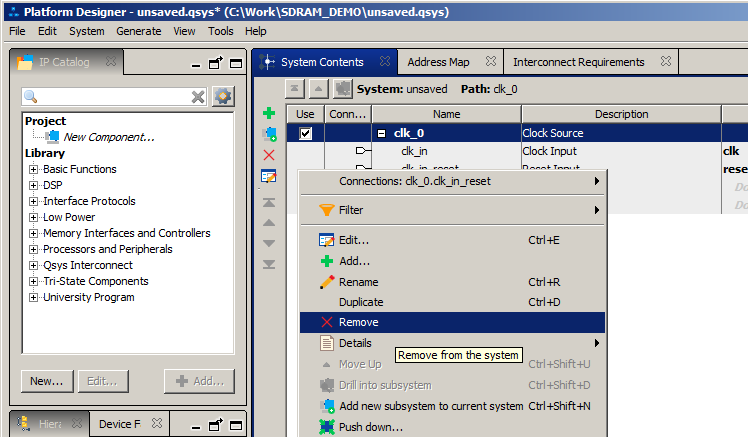

Wir haben ein System erstellt, das ein Uhr- und Rücksetzmodul enthält:

Wie bereits erwähnt, ist für den SDRAM-Kern eine spezielle Taktung erforderlich. Daher wird das Standardmodul rücksichtslos weggeworfen

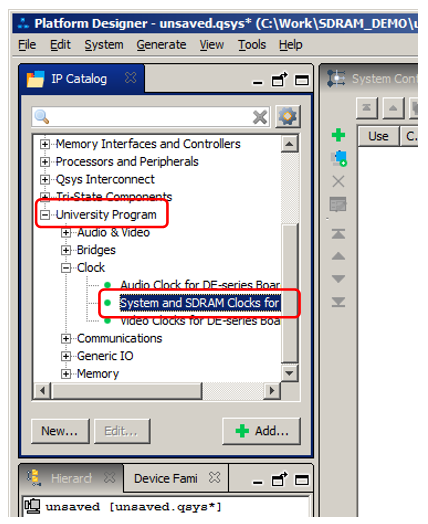

Fügen Sie stattdessen den Block Universitätsprogramm-> System und SDRAM-Uhr für Karten der DE-Serie hinzu:

Wählen Sie in den Eigenschaften DE0-Nano aus, da die Inspiration für die SDRAM-Schaltschaltung von diesem Steckbrett stammt:

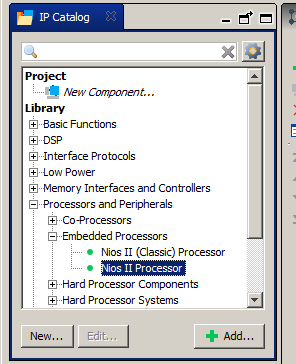

Wir fangen an, unser Prozessorsystem zu stopfen. Das erste, was hinzugefügt werden muss, ist natürlich der Prozessorkern selbst. Sei es Prozessor und Peripheriegeräte-> Embedded-Prozessoren-> NIOS II-Prozessor.

Für ihn füllen wir noch keine Eigenschaften aus. Klicken Sie einfach auf Fertig stellen, obwohl wir eine Reihe von Fehlermeldungen erstellt haben. Bisher gibt es keine Ausrüstung, die diese Fehler beseitigt.

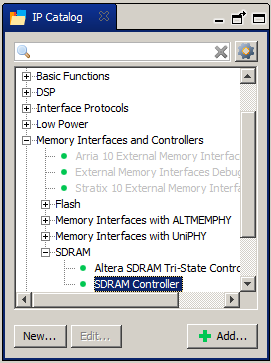

Fügen Sie nun das eigentliche SDRAM hinzu. Speicherschnittstellen und Controller-> SDRAM-> SDRAM-Controller.

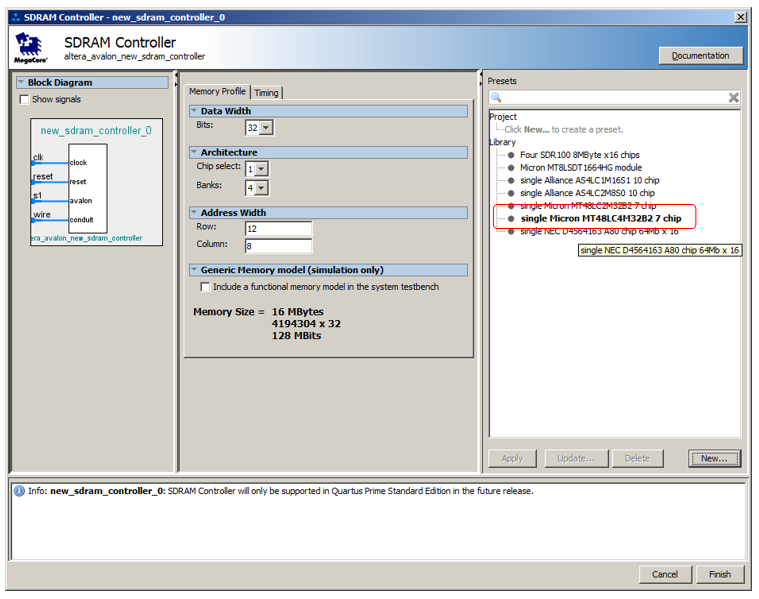

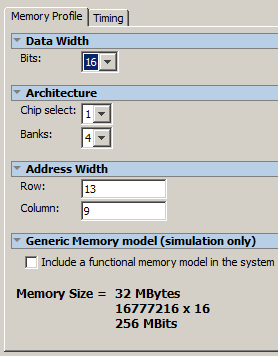

Hier müssen wir uns daran halten, die Eigenschaften auszufüllen. Wählen Sie aus der Liste die nächstgelegene Mikroschaltung aus, die in der Organisation ähnlich ist, und klicken Sie auf Apppy. Seine Eigenschaften fallen in die Felder Speicherprofil:

Jetzt ändern wir die Breite des Datenbusses auf 16, die Anzahl der Adressleitungen auf 13 und die Spalten auf 9.

Ich korrigiere die Zeiten noch nicht, vielleicht wird diese Empfehlung in Zukunft geändert.

Das Prozessorsystem impliziert ein Programm. Das Programm muss irgendwo gespeichert sein. Wir werden den SDRAM-Chip testen. Im Moment können wir ihr nicht vertrauen. Fügen Sie daher zum Speichern des Programms Speicher hinzu, der auf dem Block-RAM-FPGA basiert. Grundfunktionen-> On-Chip-Speicher-> On-Chip-Speicher (RAM oder ROM):

Volumen ... Nun, lassen Sie es 32 Kilobyte sein.

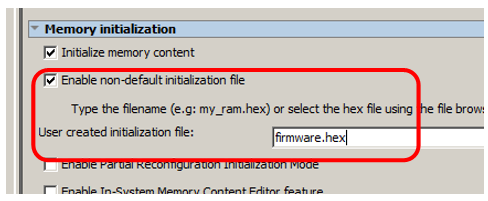

Dieser Speicher muss von irgendwoher geladen werden. Aktivieren Sie dazu das Kontrollkästchen Nicht standardmäßige Initialisierungsdatei aktivieren und geben Sie einen aussagekräftigen Dateinamen ein. Sagen wir firmware.hex:

Der Artikel ist bereits kompliziert, sodass wir ihn nicht überladen. Wir werden einfach das physikalische Ergebnis des Tests in Form von PASS / FAIL-Zeilen ausgeben (und wir werden das logische Ergebnis mit meinem bevorzugten JTAG-Debugging sehen). Fügen Sie dazu den GPIO-Port hinzu. Prozessoren und Peripheriegeräte-> Peripheriegeräte-> PIO (Parallel IO):

In den Eigenschaften, in denen wir 2 Bits setzen, möchte ich auch das Kontrollkästchen für die individuelle Steuerung von Bits aktivieren. Auch nur eine Gewohnheit.

Wir haben ein solches System mit einer Reihe von Fehlern:

Wir beginnen sie zu beseitigen. Zunächst werden wir die Uhr brechen und zurücksetzen. Bei der Clock- und Reset-Einheit müssen die Eingänge weggeworfen werden. Dazu gibt es Felder mit der Aufschrift "Zum Exportieren doppelklicken":

Wir klicken, geben aber mehr oder weniger kurze Namen.

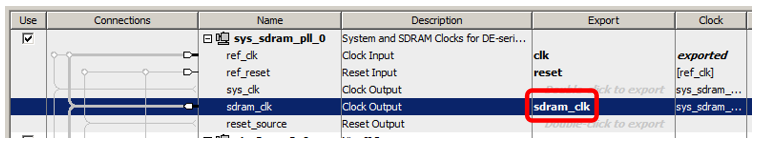

Sie müssen auch den SDRAM-Taktausgang wegwerfen:

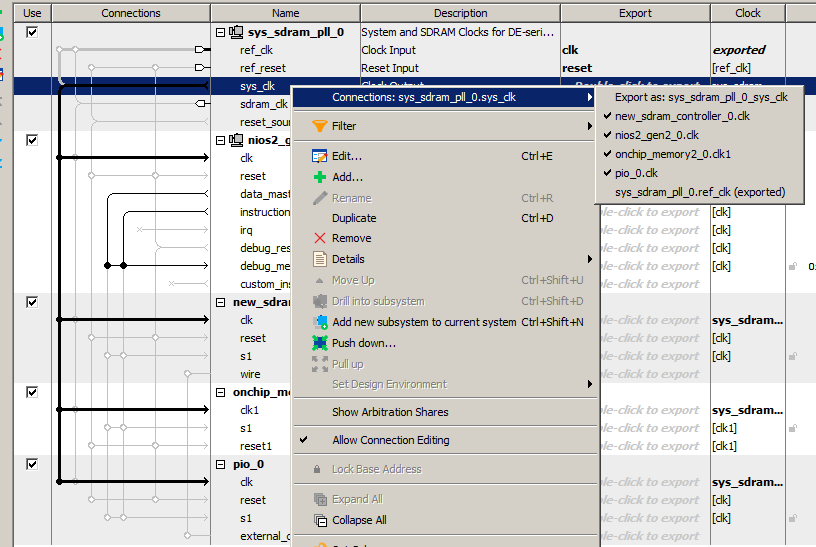

Jetzt teilen wir sys_clk auf alle Takteingänge und reset_source auf alle Rücksetzleitungen. Sie können die Punkte, die die entsprechenden Linien verbinden, vorsichtig mit der „Maus“ treffen oder zum entsprechenden Ausgang gehen, die rechte Maustaste drücken und dann zum Untermenü Verbindungen im Dropdown-Menü gehen und dort die Verbindungen auswählen.

Dann verbinden wir die Reifen miteinander. Wir verbinden Data Master mit allen Bussen aller Geräte und Inctruction Master mit fast allen. Es ist nicht erforderlich, es an den PIO_0-Bus anzuschließen. Von dort werden Anweisungen definitiv nicht gelesen.

Jetzt können Sie Adresskonflikte lösen. Wählen Sie dazu den Menüpunkt System-> Basisadressen zuweisen:

Und wenn wir Adressen haben, können wir auch Vektoren zuweisen. Gehen Sie dazu zu den Eigenschaften des Prozessorkerns (zeigen Sie darauf, drücken Sie die rechte Maustaste und wählen Sie den Menüpunkt Bearbeiten) und konfigurieren Sie dort die Vektoren im Onchip-Speicher. Wählen Sie einfach diesen Speichertyp in den Dropdown-Listen aus, die Nummern werden selbst ersetzt.

Keine Fehler mehr. Es bleiben jedoch zwei Warnungen. Ich habe vergessen, die SDRAM- und PIO-Zeilen zu exportieren.

Doppelklicken Sie, wie bereits beim Reset- und Clock-Block, auf die gewünschten Beine und geben Sie ihnen die kürzesten (aber verständlichen) Namen:

Alles, es gibt keine Fehler oder Warnungen mehr. Speichern Sie das System. Darüber hinaus muss der Name mit dem Namen des Projekts übereinstimmen, damit das Prozessorsystem zu einem Element der obersten Ebene des Projekts wird. Haben Sie nicht vergessen, wie wir es nannten?

Nun, wir drücken den wichtigsten Knopf - HDL generieren.

Alles, der Prozessorteil wird erstellt. Klicken Sie auf Fertig stellen. Wir werden daran erinnert, dass es schön wäre, dieses Prozessorsystem zum Projekt hinzuzufügen:

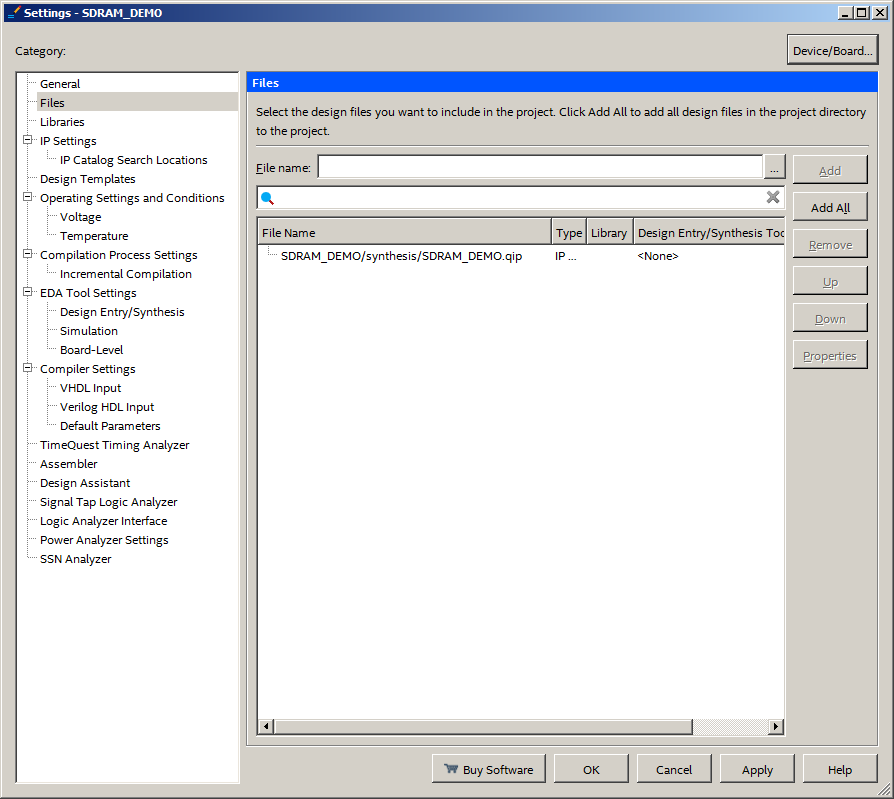

Hinzufügen:

Und dort erreichen wir mit der Schaltfläche Hinzufügen das folgende Bild:

SIP-Datei wurde noch nicht erstellt. Ja, und wir brauchen es im Rahmen dieses Artikels nicht.

Uhhhh Der erste Schritt wurde getan. Wir entwerfen das Projekt so, dass das System die Projekthierarchie und die verwendeten Beine herausfindet. Kompilierungsfehler sind nicht beängstigend. Nur in der kostenlosen Version der Umgebung wurden Kernel erstellt, die nur funktionieren, wenn der JTAG-Adapter verbunden ist. Aber im Redd-Komplex ist es immer verbunden, da es auf einer gemeinsamen Tafel geschieden ist, das heißt, wir haben nichts zu befürchten. Also ignorieren wir diese Fehler.

Nun zurück zur Beschreibung des SDRAM-Kernels. Es heißt, dass die CKE-Leitung nicht verwendet wird und immer mit dem Gerät verbunden ist. Tatsächlich sind FPGA-Strecken im Rahmen des Komplexes nicht nur teuer, sondern auch eine wertvolle Ressource. Und es wäre dumm, das Bein zu spreizen, das sich immer in der Einheit befindet (und auf dem DE0-NANO-Board ist es auch nicht geschieden). Es würde eine Verilog-Schicht geben, die entsprechende Kette könnte dort geschnitten werden, aber ich spare Zeit (nervöses Lachen, wenn man das Volumen des bereits erhaltenen Dokuments betrachtet, aber ohne Speichern wäre es noch mehr geworden). Daher gibt es keine Schicht. Wie man ist Gehen Sie zum Zuweisungseditor. Es ist drin, da es in Pin Planner nach den Beschreibungen keine ähnliche Funktionalität gibt.

Es gibt noch keine Leitung. Gut. Erstellen Sie eine neue

Wir wählen das folgende Symbol:

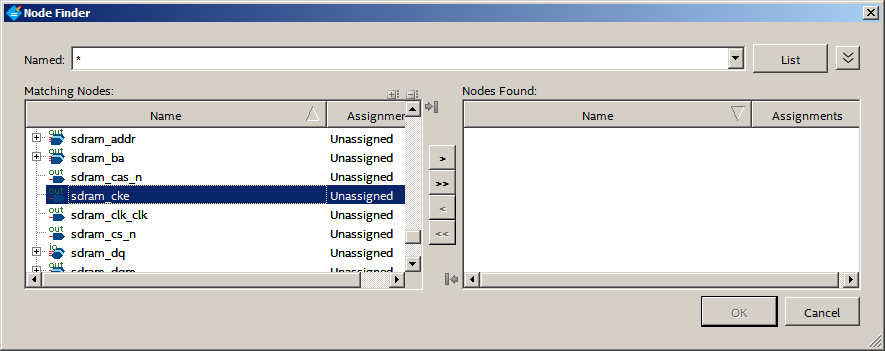

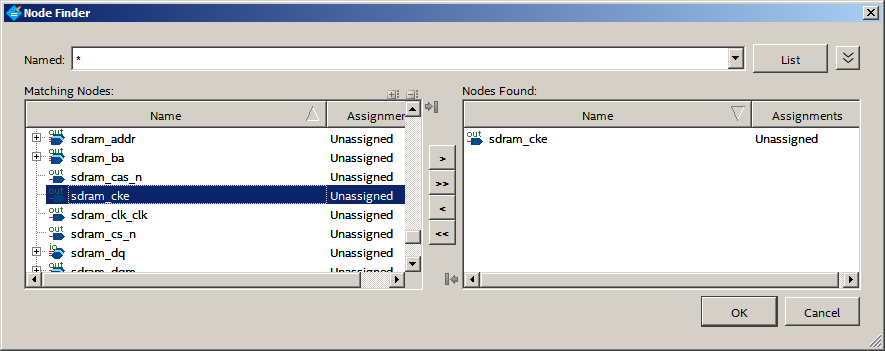

Klicken Sie in dem von uns festgelegten Suchsystem auf Liste und in den Suchergebnissen finden Sie unsere CKE:

Fügen Sie es der rechten Spalte hinzu und klicken Sie auf OK.

Wir bekommen folgende Liste:

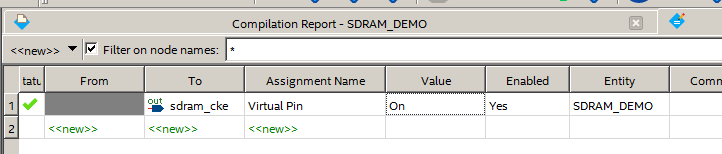

Klicken Sie im gelben Feld auf die Dropdown-Liste und suchen Sie den virtuellen Pin. Wir wählen. Die Gelbfärbung zog in eine andere Zelle:

Dort wählen wir Ein:

Alle Gelbfärbung ist weg. Und die Kette ist jetzt als virtuell markiert, was bedeutet, dass kein physisches Bein erforderlich ist. Daher können wir es nicht der physischen Schlussfolgerung des FPGA zuordnen. Schließen Sie den Zuweisungseditor und öffnen Sie den Pin-Planer. Sie können die Beine anhand der Abbildung zuweisen oder die Liste aus der * .qsf-Datei entnehmen, die Teil des Projekts ist, das ich dem Artikel anhängen werde.

Das war's, schließen Sie Pin Planner, wir führen die endgültige Zusammenstellung des Projekts durch. Die Hardware ist fertig, wir fahren mit der Entwicklung der Software für das resultierende Prozessorsystem fort. Aber der Artikel ist so groß geworden, dass wir ihn das

nächste Mal machen werden .