Sie haben diesen Traum: Sie befinden sich auf einer Prüfung oder sprechen vor einem bestimmten Publikum, und plötzlich stellen Sie fest, dass Sie sich überhaupt nicht vorbereitet haben und jetzt müssen Sie improvisieren. In dieser Situation, aber nicht in einem Traum, sondern im wirklichen Leben, stand ich vor den Maiferien in Moskau, wo ich aus Kalifornien flog, um ein dreitägiges Seminar für sorgfältig ausgewählte Schüler führender Moskauer Physikschulen durchzuführen. Unter der Schirmherrschaft von RUSNANO, im RUT-Gymnasium (MIIT) und in Anwesenheit von Lehrern von MIET, MIREA, MEPhI, MPEI und HSE MIEM.

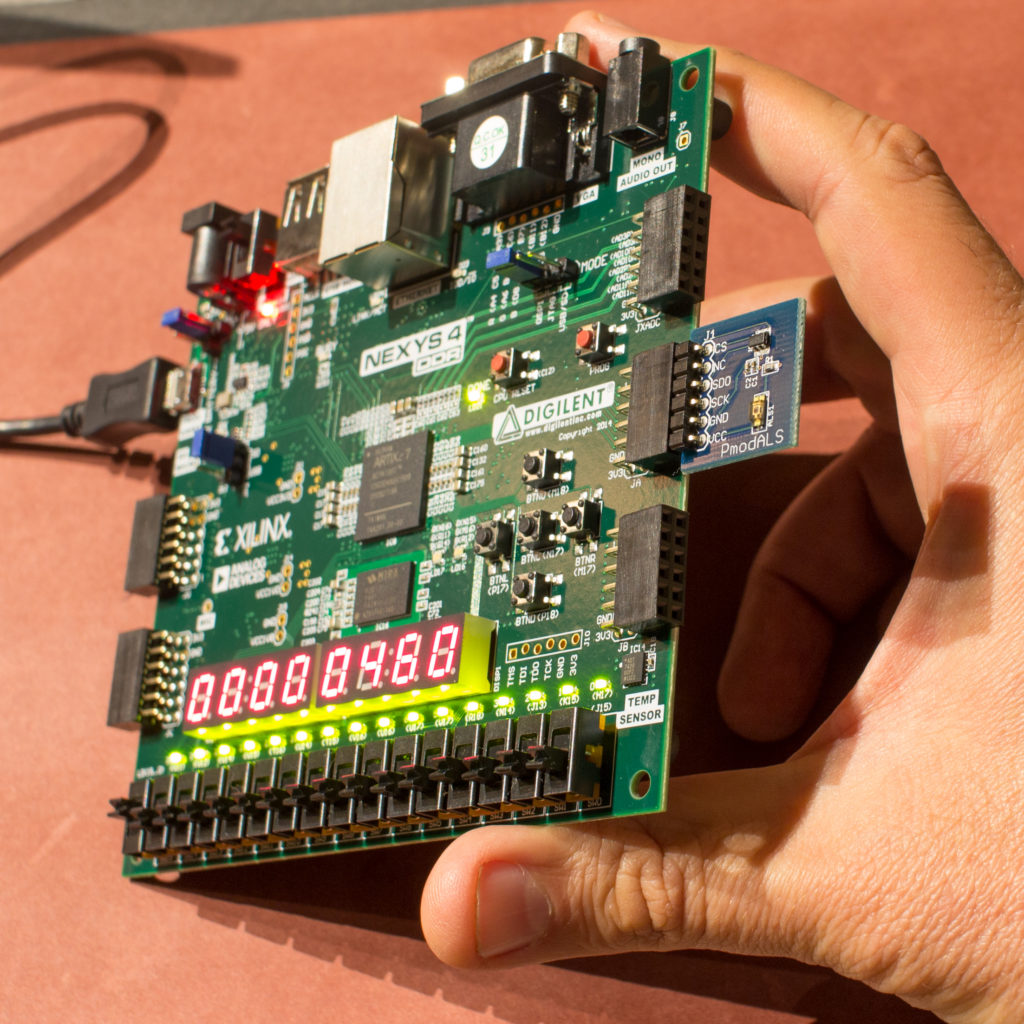

Meine Moskauer Kollegen hofften auf mich, und theoretisch hätte ich Schritt für Schritt Anweisungen und Beispiele für verschiedene Übungen auf einer Leiterplatte mit einer rekonfigurierbaren Logik-Mikroschaltung mitbringen sollen. Eigentlich hatte ich einige Beispiele für andere Boards, von denen ich nichts in der Unordnung von Flügen und anderen Ereignissen gebaut habe.

Deshalb nahm ich ein universelles Beispiel, das ich vor anderthalb Jahren in einem Alma-Ata-Astana-Flugzeug schrieb, warf alle Innereien aus dem Beispiel heraus und begann, es ohne harten Plan mit Schulkindern zu füllen. Und seltsamerweise - es hat funktioniert. Während des Füllvorgangs entstanden lehrreiche Momente der digitalen Schaltung und der Verilog-Hardwarebeschreibungssprache, die während der Planung nicht entstanden wären.

Am 4. Juni werden ich und meine Kollegen von Wave Computing ein ähnliches Seminar in Las Vegas durchführen, jedoch nur für Erwachsene. Vom 8. bis 19. Juli helfe ich MIET bei der Durchführung einer Sommerschule in Zelenograd. Pläne für diese Veranstaltungen (nicht endgültig, sondern zur Diskussion in einer Gruppe von Lehrern und Ingenieuren, einschließlich hier auf Habré) - am Ende des Beitrags.

Warum brauchen wir ein Seminar über FPGAs für Schulkinder? Integrierte Schaltungen mit programmierbarer Logik (FPGAs oder FPGAs - Field Programmable Gate Arrays) sind eine traditionelle Methode, um das Wissen in der Praxis zu konsolidieren, wenn das Design digitaler Schaltungen auf der Ebene der Registerübertragung unter Verwendung von Hardwarebeschreibungssprachen untersucht wird. Mit anderen Worten, die Schlüsseltechnologie für die Entwicklung von iPhones - Mikrochips in iPhones sind so konzipiert. Russlands Rückstand auf iPhones war auch auf die Tatsache zurückzuführen, dass FPGAs, Mikroarchitekturen und Hardwarebeschreibungssprachen Anfang der neunziger Jahre in Berkeley und MIT und in Russland aufgrund des Zusammenbruchs der UdSSR viel später eingeführt wurden.

Das letzte Rosnanov-Seminar verlief überraschend reibungslos, vor allem, weil die Studenten, die es besuchten, zuvor einen theoretischen Online-Kurs mit einer karriereorientierten Übersicht über moderne Methoden zur Gestaltung von Mikroschaltungen abgeschlossen hatten. Der Online-Kurs richtet sich an fortgeschrittene Schüler des Typs Olympiade und besteht aus drei Modulen:

„Vom Transistor zur Mikroschaltung“ ,

„Die logische Seite der digitalen Schaltung“ und

„Die physikalische Seite der digitalen Schaltung“ . In diesem Kurs lernen die Teilnehmer die sogenannte RTL2GDSII-Route kennen - eine Gruppe von Technologien, mit denen Ingenieure in Elektronikunternehmen Bulk-Chips (Application Specific Integrated Circuits, ASIC) entwerfen. FPGAs / FPGAs werden zum Prototypen von ASICs verwendet, einschließlich Unternehmen wie Intel, Apple und NVidia.

Seit die Studenten den Online-Kurs besucht haben, haben sie bereits gelernt, was D-Trigger, Zustandsmaschine, logische Synthese und Nachverfolgung sind. Sie sahen auch die Hardwarebeschreibungssprache im Online-Kurs. Jetzt musste dieses Wissen, das passiv in ihrer Erinnerung lag, nur wiederbelebt werden.

Jetzt werde ich immer für Seminare in den GUS-Ländern (zusätzlich zu den bereits geplanten Seminaren habe ich Vorschläge, dies in Minsk, Sotschi und Jakutsk durchzuführen) die Voraussetzung dafür schaffen, dass der Gastgeber Schulkinder oder Studenten über drei Module des Online-Kurses vorab aufnehmen kann Es bleiben nur motivierte Menschen übrig, die bereits alle mühsamen Aspekte durchlaufen haben, und reine Kreativität bleibt zur Verstärkung im letzten Moment, wie zum Beispiel der Fall eines Apfels, der Newtons Kopf traf. Darüber hinaus verknüpft der Online-Kurs all diese Aktivitäten mit Erwachsenenberufen. Die nächste Stufe zeichnet ein entferntes Ziel.

Insgesamt habe ich vor meinem Flug nach Moskau in meinem Haus in Sunnyvale, Kalifornien, ein universelles Beispiel vorgestellt.

Beispielcode :

Am ersten Tag des Workshops übten wir mit Mikroschaltungen mit einem geringen Integrationsgrad auf einem Steckbrett. Diese Technologie ist 50 Jahre alt, aber niemand hat im wirklichen Leben eine bessere Idee als in der Simulation, um beispielsweise zu zeigen, wie D-Trigger funktionieren. Obwohl es vielen modernen Technologielehrern an Schulen als veraltet und unnötig erscheint, geht jetzt im 6.111-Kurs des Massachusetts Institute of Technology im akademischen Jahr 2018/2019 das erste Labor für digitale Schaltkreise genau so mit Mikroschaltungen mit geringem Integrationsgrad vor - siehe

http: //web.mit.edu/6.111/volume2/www/f2018/index.html .

Darüber hinaus ist es am Beispiel der Verbindung von Mikroschaltungen mit einem geringen Grad an Integration mit Tasten zweckmäßig zu erklären, was es ist, warum es benötigt wird und wie Pull-up-Widerstände funktionieren. Und warum sie ein Potential von 0 geben, wenn die Taste nicht gedrückt wird, und wie hängt dies mit dem Spannungsteiler zusammen.

Selbst wenn am Beispiel eines Mikroschaltkreises mit geringem Integrationsgrad die LED durchbrennt, erhalten die Schüler Lebenserfahrung, dass es notwendig ist, dort einen Widerstand anzubringen. Wenn sie dies auf einem Computerbildschirm in einem Software-Simulator eines Steckbretts sehen, erhalten sie keine solche Lebenserfahrung, da Sie alles auf den Bildschirm zeichnen können und Schulkinder nicht sicher sind, ob Burnout wahr ist.

So ist die Funktion des D-Flip-Flops auf Mikroschaltungen mit geringem Integrationsgrad deutlich sichtbar:

Der zweite Tag begann mit einer historischen Skizze: Wie Mikrochips vor 50 Jahren entworfen wurden und wie sie sich seitdem zweimal verändert haben. Eine der Revolutionen überlagerte den Zusammenbruch der UdSSR, und dies ist der wichtigste technische Grund, warum Russland keine iPhones besitzt.

Um 8.45 Uhr wurde die Geschichte erzählt, wie der sowjetische Bojenspion, der die Bewegung amerikanischer Schiffe überwachte, in den Ozeanen gefangen wurde und wozu dies führte.

Am 13. März verdrängte die Geschichte, wie die Veröffentlichung eines Bloggers, John Cooley, die gesamte globale Industrie von VHDL zu Verilog.

Am 16.10 die Geschichte, wie Microsoft Windows als Plattform für die Arbeit von Chip-Designern an Linux verlor.

In diesem Teil - eine Demonstration, wie ein Programm zur Synthese von digitaler Logik und Firmware-Konfiguration im FPGA ausgeführt wird. Auf zwei Arten - durch Ausführen eines Skripts unter Linux und in einer integrierten grafischen Shell. Auch eine kurze Beschreibung des Inhalts der Demo. Nach diesem Galopp durch Europa setzen sich die Schüler an die grafische Hülle und machen einfache Übungen, beginnend mit den UND-ODER-NICHT-Logikelementen, deren Eingänge mit den Tasten verbunden sind, und den Ausgängen mit den LEDs. So etwas in der Art:

module top (input [2:0] key, output [7:0] led); wire a = ~ key [0]; // 0, , wire b = ~ key [1]; wire c = a & b; assign led [0] = ~ c; // , 0 endmodule

Dabei stellten sich sofort zwei interessante Fragen. Zuerst habe ich selbst vergessen, dass sowohl die Tasten als auch die LEDs auf dieser Platine invertiert sind. Das heißt, wenn die Taste gedrückt wird, dann 0 auf dem Draht und wenn nicht gedrückt, dann 1. Und wenn 0 der LED zugeführt wird, ist sie an und wenn 1 nicht an ist. Wenn Sie nichts über Inversion wissen, verhält sich das logische Element AND (led [0] = key [0] & key [1]) wie OR und OR - wie I. Gesetze von de Morgan in Aktion! ~ (a & b) == ~ a | ~ b sowie ~ (a | b) == ~ a & ~ b.

Aber selbst nachdem einige Schulkinder korrigiert hatten, funktionierte dieses Geschäft immer noch umgekehrt. Dann schaute ich in ihren Code und stellte fest, dass sie beim Umschreiben des Codes, den ich an die Tafel geschrieben hatte, dachten, dass „~“ (Tilde) „-“ (Minus) ist. Dies gab mir einen hervorragenden Grund, über den Unterschied zwischen

direktem und

zusätzlichem Code zu sprechen und auch darüber, warum für Einzelbitnummern (- 0) == 0 und (- 1) == 1, während (~ 0) == 1 und (~ 1) == 0. Um die Negation für Mehrbitzahlen in einem zusätzlichen Code zu berechnen, reicht es aus, sie bitweise zu invertieren und eins hinzuzufügen: - a == ((~ a) + 1).

Fortsetzung - Teile

2.3 ,

2.4 ,

2.5 .

Die gesamte Lektion fand unter Linux statt, genauer gesagt unter Lubuntu 18.04, auf dem Intel FPGA Quartus II installiert war. Lubuntu wurde mit SSDs geladen, auf denen auch Intel FPGA Quartus II Lite Edition 18.1 installiert war. Um von der SSD zu booten, müssen Sie sie nur an den USB 3.0-Anschluss anschließen, den Computer einschalten und F12 drücken. Rufen Sie dann das Menü auf und sagen Sie "Laden von USB".

Obwohl die Synthesesoftware für FPGA auch unter Windows verfügbar ist, ist Linux aus zwei Gründen gut:

1. Linux kann auf schwächeren Computern als Windows ausgeführt werden. Zum Beispiel habe ich einen Laptop mit 2 Gigabyte Speicher, also legt Intel FPGA / Altera Quartus II für Windows darauf fest und funktioniert gut unter Linux.

2. Alle erwachsenen Entwickler von Bulk-Chips bei Apple, NVidia und anderen elektronischen Unternehmen verwenden Linux, auf dem die Programme Synopsys Design Compiler, Synopsys IC Compiler, Synopsys VCS, Cadence IES usw. ausgeführt werden.

Warum ist es besser, alles auf bootfähigen SSDs zu tun und sie nicht auf Computern im Klassenzimmer zu platzieren? Da die Installation von Software von FPGA-Unternehmen ein ziemlich trostloser Prozess ist und Sie in der Umgebung von Altera Quartus oder Xilinx Vivado mit einem Tamburin arbeiten, Dateien in / etc ändern und alte 32-Bit-Bibliotheken für einige Komponenten installieren müssen, insbesondere für die kostenlose Version von Mentor ModelSim. Einige Bibliotheken müssen aus Quellcodes kompiliert werden. Es gibt

Skripte von Stanislav Zhelnio , die alles automatisch erledigen, aber selbst mit diesem Skript

dauert die Installation auf einem Computer einige Stunden.

Warum nicht alles in virtuellen Maschinen machen? Zum Beispiel mit VirtualBox? Wir haben dies an der Moskauer Staatsuniversität und an anderen Orten versucht, aber dort können Störungen durch USB-Ziehen auftreten. Eine bootfähige SSD mit Lubuntu scheint die beste Option zu sein.

Um das SSD-Set für den Workshop vorzubereiten, müssen Sie alles auf eine SSD legen und dann mit einem solchen Befehl klonen, mit dem Sie sofort von einer auf drei SSDs schreiben können:

time sudo dcfldd if=/dev/sdb bs=1M of=/dev/sdc of=/dev/sdd of=/dev/sde

Hier müssen Sie wissen, dass nicht alle SSD-Gehäuse Linux unterstützen, z. B. Kingwin Data Star verwöhnt Festplatten. Die richtigen Gehäuse sind Orico und Eluteng.

Außerdem empfehle ich nicht, SSDs durch einfache, herunterladbare USB-Sticks zu ersetzen. Obwohl es auch auf USB-Sticks funktioniert, sind einige Vorgänge unglaublich langsam und verursachen Unbehagen und Irritationen. Auf geladenen SSD-Laufwerken mit USB 3.0 fliegt jedoch alles schneller als Linux auf einer internen Festplatte.

Ich habe auch versucht, ein bootfähiges SSD-Laufwerk durch Drücken der Wahltaste beim Booten in den Apple Mac zu stecken, aber es hat nicht funktioniert. Weder über den USB 3.1-Anschluss noch über 3.0. Es scheint, dass der Mac beim Booten weder das Ext4-Dateisystem noch die Partitionstabelle verstehen möchte. Gibt es Mohn-Treiber und Linuxoide unter meinen Lesern? Es wäre interessant zu wissen, was zu tun ist (neben der Option, VirtualBox oder andere virtuelle Maschinen zu verwenden).

Interessanterweise verwendeten vor dem Seminar nur 2 Studenten aus der gesamten Gruppe Linux. Das ist sehr seltsam für mich, da ich anstelle des russischen Bildungsministeriums vor 10 Jahren alle russischen Schulen auf Linux übertragen würde, als Ubuntu benutzerfreundlich wurde. Zusätzlich zu Ubuntu könnte man eine spezielle russische Version von Linux für den Unterricht erstellen. Windows ist mit Viren verstopft. Sie müssen Lizenzgebühren dafür zahlen. Warum ist Windows besser als Linux, wenn Sie beispielsweise Python-Programmierschulkurse absolvieren? Oder reichen Google-Dokumente für Schüler nicht aus, aber Microsoft Word wird benötigt? Ich verstehe es einfach nicht.

Sogar die südkoreanische Regierung hat 2020 beschlossen, auf Linux umzusteigen .

Auf jeden Fall hatten Schulkinder bei meinem Seminar keine Probleme mit Linux, obwohl, wie gesagt, die meisten Schulkinder es zum ersten Mal verwendeten.

Zu Beginn des dritten Tages kam ich zu spät, weil ich eingeladen wurde, einen Vortrag vor der russischen Niederlassung von Samsung zu halten, und die Veranstaltung 3 Stunden dauerte (Sie können die Vorlesungsfolien herunterladen:

1 ,

2 ,

3 und

einen Artikel über einen Teil des Inhalts ), wonach ich hungrig wurde und nur während Das Essen von Buchweizen und Oliven in Mumu (was ich in Kalifornien sehr vermisse) stellte fest, dass mein Unterricht in der Turnhalle in 5 Minuten beginnen würde.

Dann rief ich Alexander Silantiev von MIET an und bat darum, den Unterricht ohne mich zu beginnen. Am Vortag begannen die Schüler mit einem Sieben-Segment-Indikator zu trainieren, der einen Buchstaben anzeigte. Wenn Sie nun die Ausgabe eines Buchstabens mit einem Schieberegister kreuzen, können Sie die Ausgabe auf einem dynamischen Mehrbit-Siebensegmentindikator implementieren. Gleichzeitig lernen die Schüler, wie man sequentielle Logik auf Veril codiert.

Der Plan war ein Erfolg - als ich das Klassenzimmer betrat, liefen einige Schulkinder bereits langsam Buchstaben auf einem dynamischen Indikator, und damit sie zu Wörtern verschmolzen, musste lediglich die Häufigkeit der Erzeugung des Aktivierungssignals (Aktivierungssignals) für das Schieberegister erhöht werden:

Dann gab ich Stanislav Zhelnio

Sparf von IVA Technologies das Wort und er skizzierte kurz, wie man von einfachen Logikblöcken zu einem winzigen, aber völlig realen Prozessor

übergeht (siehe

Beiträge von Stanislav auf Habr und

schoolMIPS auf GitHub ):

Fortsetzung des Vortrags von Stanislav ZhelnioDas Seminar fand am Gymnasium der Russischen Verkehrsuniversität (MIIT) statt. Während des Seminars und davor halfen Irina Grunicheva und Gleb Romanov (eNano); Alexey Pereverzev, Alexander Silantiev und Yevgeny Primakov von MIET, Alexander Romanov von HSE MIEM und seine Schüler, Alexei Kochnov von NIIIS, League of Robots (obraz.pro), Pavel Kirichenko (ICST, Intel, Autor von Büchern

bhv.ru/books/book). php? id = 201192 ), Yegor Kuzmin vom

Institut für Angewandte Mathematik der Russischen Akademie der Wissenschaften, Daria Krivoruchko, ein Schulmädchen von SUNTs, war bei LYuP, Timofey Cherkasov (Akademie für Digitale Technologien in St. Petersburg, School of Engineering Thinking LNMO), Alexander Bakerenkov und Julia Shaltaeva von der PreI-Universität MEPim Vorontsov von MPEI, Evgeny Pevtsov von MIREA, Vitaliy Kravchenko von Nautekh, Arkady Poe Yakov und Sergey Pevchenko von MEI.

Ruslan Tikhonov von Amperka brachte Komponenten für Übungen mit Mikroschaltungen mit geringem Integrationsgrad mit.

Der Herausgeber Dmitry Movchan von DMK Press präsentierte jedem Teilnehmer nützliche Bücher - ein umfangreiches Lehrbuch von David Harris und Sarah Harris, Digitale Schaltkreise und Computerarchitektur, und einfaches Lesen von A. Hideharu, Unterhaltsame Elektronik. Digitale Schaltungen. Manga

Maxim Maslov, der dem Moskauer Institut für Physik und Technologie angeschlossen ist, kam zu dem Seminar und spendete FPGA-Boards an Sommerschulen (in Russland gibt es wenig Wohltätigkeit für Bildung).

Was wird als nächstes passieren? Und dann wird es zwei Veranstaltungen geben, die das, was wir am RTH-Gymnasium gemacht haben, erweitern und vertiefen werden. Vom 8. bis 26. Juli findet die MIET-Sommerschule in Zelenograd statt. Hier ist ein Vorschlag für ihr Programm. Ihre ersten zwei Wochen bestehen aus fünf Teilen:

- Die Grundlagen digitaler Schaltungen auf Mikroschaltungen mit geringem Integrationsgrad.

- Einfache Übungen mit kombinatorischer und sequentieller Logik auf der FPGA-Karte.

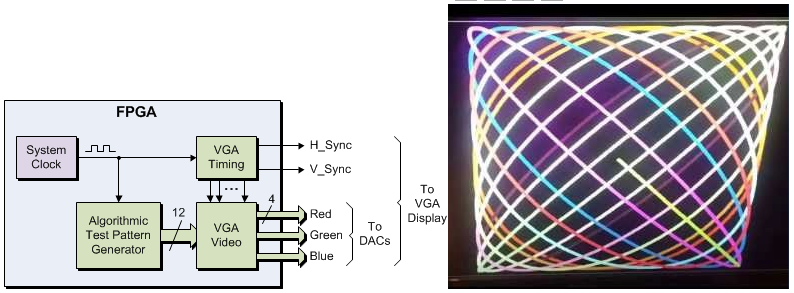

- Verwenden von FPGAs zur Steuerung der Grafikanzeige.

- Das Gerät und die Implementierung des einfachsten Mikroprozessors auf dem FPGA.

- Einzelne Projekte zur Erstellung von Spielen a la simplified Angry Birds, sowohl basierend auf einer Finite-State-Maschine, die ausschließlich in der FPGA-Hardware enthalten ist, als auch mit Programmsteuerung über den einfachsten im FPGA synthetisierten Prozessor.

Aber vor der Schule am 4. Juni wird es in Las Vegas ein Seminar geben, bei dem wir uns nicht mit dem Schulverarbeiter, sondern mit dem industriellen befassen werden.

Detaillierteres Programm in Zelenograd:

Woche 1. Grundlagen der digitalen Logik.

Tag 1. Kleine integrierte Schaltkreise, kombinatorische Logikübungen

Tag 2. Mikroschaltungen mit geringem Integrationsgrad, Übungen mit sequentieller Logik

Tag 3. FPGA, Übungen mit Tasten, Schaltern, LED, Sieben-Segment-Anzeige

Tag 4. FPGA, Ausgabe geometrischer Formen an VGA

Tag 5. FPGA, Zustandsmaschine für Angry Birds

Woche 2. Prozessor

Tag 1. Programmierung in Assemblersprache.

Tag 2. SchoolMIPS-Prozessor mit einem Zyklus.

Tag 3. Interaktion des Prozessors mit dem Abschluss geometrischer Formen auf VGA.

Tag 4. Vortrag über Unterbrechungen und Multitasking. Einzelprojekt - ein auf dem Prozessor programmiertes Videospiel mit Ausgabe an VGA.

Tag 5. Vortrag über das Förderband. Wettbewerb einzelner Projekte.

Woche 1. Tag 1. Kleine integrierte Schaltkreise.

1.1. Übungen mit kombinatorischer Logik.

1.1.1. XOR-Logikelement auf CD4070, ohne Tasten und Pull-up-Register - wiederholen Sie die Demonstration.

1.1.2. XOR-Logikelement, Schaltflächen und Pull-up-Register hinzufügen - Wiederholung der Demonstration.

1.1.3. Einzelaufgabe - per Datashit, um eine Demonstration eines der logischen Elemente AND / OR / NOT / XOR / NOR / NAND / XNOR mit zwei, drei, vier oder acht Eingaben zu erstellen:

1.1.3.1. CD4081, Quad 2-Eingang UND

1.1.3.2. CD4071, Quad 2-Input OR

1.1.3.3. CD4011, Quad 2-Input NAND

1.1.3.4. CD4001, Quad 2-Input NOR

1.1.3.5. CD4073, Triple 3-Input AND

1.1.3.6. CD4025, Triple 3-Input NOR

1.1.3.7. CD4082, Dual 4-Eingang UND

1.1.3.8. CD4072, Dual 4-Input OR

1.1.3.9. CD4012, Dual 4-Input NAND

1.1.3.10. CD4002, NOR mit 4 Eingängen

1.1.3.11. CD4068, 8 Eingänge UND NAND

1.1.3.12. CD4078, NOR mit 8 Eingängen

1.2. 7-Segment-Indikator mit gemeinsamer Kathode.

1.2.1. Auf einem Steckbrett mit Widerständen zusammenbauen, einzelne Segmente ausprobieren.

1.2.2. Kombination mit 7-Segment-Indikator-Treiber, CD4511, BCD zu 7-Segment-Latch-Decoder.

1.2.3. Option - Anzeige mit gemeinsamer Anode. Kombinieren Sie mit dem Wechselrichter CD4069, Wechselrichter.

1.2.4. Option - Fügen Sie dem CD4511-Eingang 4 Tasten mit Pull-up-Widerständen hinzu.

1.3. Kombinative Logikblöcke - eine individuelle Aufgabe am Ende des Tages oder in Form von Hausaufgaben:

1.3.1. CD4532, 8-Bit-Prioritätscodierer

1.3.2. CD4051, einzelner 8-Kanal-Analogschalter, wird als digitaler Decoder verwendet

1.3.3. CD4051, einzelner 8-Kanal-Analogschalter, wird als digitaler Multiplexer verwendet

1.3.4. CD4052, Dual 4-Channel Analog Switch, wird als digitaler Multiplexer verwendet

1.3.5. CD4053, dreifacher 2-Kanal-Analogschalter, wird als digitaler Multiplexer verwendet

1.3.6. CD4008, 4-Bit-Kombinationsaddierer

1.3.7. CD4063, 4-Bit-Digitalkomparator

1.3.8. CD4585, 4-Bit-Digitalkomparator

Am Ende des Tages zeigt jeder, wer was getan hat.

Woche 1. Tag 2. Übungen mit sequentieller Logik.

1.2.1. Bauen Sie einen Taktgenerator auf Basis eines 555-Chips zusammen. Probieren Sie verschiedene Kondensatoren und Widerstände aus.

1.2.2. D-Trigger auf Chip CD4013, Dual D-Flip-Flop mit Set-Reset.

1.2.3. Einzelprojekt:

1.2.3.1. Schieberegister basierend auf CD4015, statisches Dual-4-Bit-Schieberegister, Seriell-In, Parallel-Out.

1.2.3.2. Schieberegister basierend auf CD4035, 4-stufiges Schieberegister, parallel-in, parallel-out.

1.2.3.3. Schieberegister basierend auf CD4014, 8-stufiges Schieberegister, Parallel-In, Serial-Out.

1.2.3.4. Zähler mit LED-Ausgang CD4029, Binary Decimal Up Down Counter.

1.2.3.5. Zähler mit Ausgabe an eine 7-Segment-Anzeige über den Treiber.

1.2.3.6. Komplexer ist eine Kombination der Schieberegister CD4035 (Parallel-In, Serial-Out) mit dem seriellen Addierer CD4038. Es benötigt einen Wechselrichter CD4069. Zuvor werde ich den seriellen Addierer CD4032 ohne Wechselrichter demonstrieren.

1.2.3.7. Komplexer ist eine Kombination der Schieberegister CD4014 (Parallel-In, Serial-Out) mit dem seriellen Addierer CD4038. Es benötigt einen Wechselrichter CD4069.

Woche 1. Tag 3. FPGA, Übungen mit Tasten, Schaltern, LED, Sieben-Segment-Anzeige

1.3.1. Ein logisches Element in der kombinatorischen Logik wird über Tasten eingegeben und über LEDs ausgegeben.

1.3.2. Die Ausgabe eines Buchstabens auf einem Sieben-Segment-Indikator.

1.3.3. Der einfachste Multiplexer ist die Buchstabenausgabe in Abhängigkeit von der gedrückten Taste. Implementierung mit den Konstrukten "?", "If", "case".

1.3.4. Schieberegister.

1.3.5. Das Wort wird auf einem dynamischen 8-Bit-Sieben-Segment-Indikator unter Verwendung eines Schieberegisters angezeigt.

1.3.6. Einzelprojekt, vielleicht Hausaufgaben für das Wochenende:

1.3.6.1. Formen auf der LED-Matrix.

1.3.6.2. Schlange läuft auf einem Sieben-Segment-Indikator.

1.3.6.3. Schallfrequenzsignalerzeugung, Klangorgel.

1.3.6.4. Eingabe über eine 16-Tasten-Tastatur.

1.3.6.5. Codesperre - Erkennung einer Tastenfolge durch eine Zustandsmaschine.

1.3.6.6. Integration mit einem Entfernungsmesser-Sensor.

1.3.6.7. Integration mit Winkelgeber.

Tag 4. FPGA, Ausgabe geometrischer Formen an VGA

Tag 5. FPGA, Zustandsmaschine für Angry Birds

Woche 2. Prozessor

Tag 1. Programmierung in Assemblersprache.

Tag 2. SchoolMIPS-Prozessor mit einem Zyklus.

Tag 3. Interaktion des Prozessors mit dem Abschluss geometrischer Formen auf VGA.

Tag 4. Vortrag über Unterbrechungen und Multitasking. Einzelprojekt - ein auf dem Prozessor programmiertes Videospiel mit Ausgabe an VGA.

Tag 5. Vortrag über das Förderband. Wettbewerb einzelner Projekte.

Woche 3. Programmierbares Radio. Das Blockprogramm besteht aus drei Hauptteilen:

- Grundlagen der Elektrodynamik und Funkwellenausbreitung (theoretischer Teil);

- Funktionsprinzip des Transceiverpfades (Theorie und Praxis);

- Grundlagen der digitalen Signalverarbeitung - Filterung, Spektralanalyse (Theorie und Praxis).

Tag 1. Theoretische Grundlagen der Elektrodynamik und der Ausbreitung von Radiowellen. Das Strukturdiagramm des Übertragungsweges, die Funktionen der Komponenten. Signale (harmonisch, rechteckig). Signalpraxis mit NI Elvis.

Tag 2. Übertragung von Signalen auf eine hohe Frequenz. Mathematische Begründung für die Frequenzübertragung mit Matlab. Praktische Übung zur Frequenzübertragung mit NI Datex.

Tag 3. Verstärkung und Emission von Signalen. Üben Sie mit NI Datex. Demonstration der Richtwirkung der Antennen.

Tag 4. Signal filtern. Üben Sie mit NI Datex. Digitale Signalfilterung in Matlab

Tag 5. Übertragen von Signalen auf eine niedrige Frequenz. Üben Sie mit NI Datex. Das abgedeckte Material zusammenfassen, zusammenfassen.

Über den Rest der Schultage werden weitere Details in einem separaten Beitrag veröffentlicht, nachdem dies im Organisationskomitee der Sommerschule besprochen wurde. Wenn Sie als Schüler oder Ausbilder an der Sommerschule am MIET in Zelenograd teilnehmen möchten, haben die

Organisatoren gerade die Kontakte und die Registrierung veröffentlicht . Wenn Sie Student sind, ist es wichtig, dass Sie bis Juli alle drei Module des Rosnanov-Onlinekurses vollständig abgeschlossen haben (

„Vom Transistor zur Mikroschaltung“ ,

„Die logische Seite der digitalen Schaltung“ und

„Die physikalische Seite der digitalen Schaltung“ ). Die Übung wird schwierig sein und wir werden nicht aufhören können herauszufinden, in welchem Zyklus sich der Wert am Eingang oder Ausgang des D-Triggers befindet. Dies passt nicht sofort in Ihren Kopf, aber wenn Sie einen Online-Kurs belegen, wird es für Sie einfacher.

Einige Details

zum Seminar in Las Vegas am 4. Juni :

Es kommt nicht oft vor, dass ein Ingenieursseminar, das ursprünglich für Russland entwickelt und in Russland (einschließlich MIPT), der Ukraine und Kasachstan getestet wurde, dann in Las Vegas auf einer Konferenz zur Automatisierung des Elektronikdesigns beginnt. In Russland und der Ukraine wurde es als MIPSfpga-Workshop und auf der Design Automation-Konferenz als MIPS Open Developer Day bezeichnet. Besuchen Sie am 4. Juni das Embassy Suites by Hilton Convention Center in der 3600 Paradise Road in Las Vegas und nehmen Sie an einer Show teil, an der Studenten und Lehrer der Moskauer Staatlichen Universität, des Moskauer Instituts für Physik und Technologie, des Moskauer Instituts für Ingenieurphysik, des Zelenograd MIET, des ITMO in St. Petersburg, der Tomsk TSU, des KPI Kiew, Almaty teilnehmen AlmaU und teilweise Nazarbayev University in Astana.

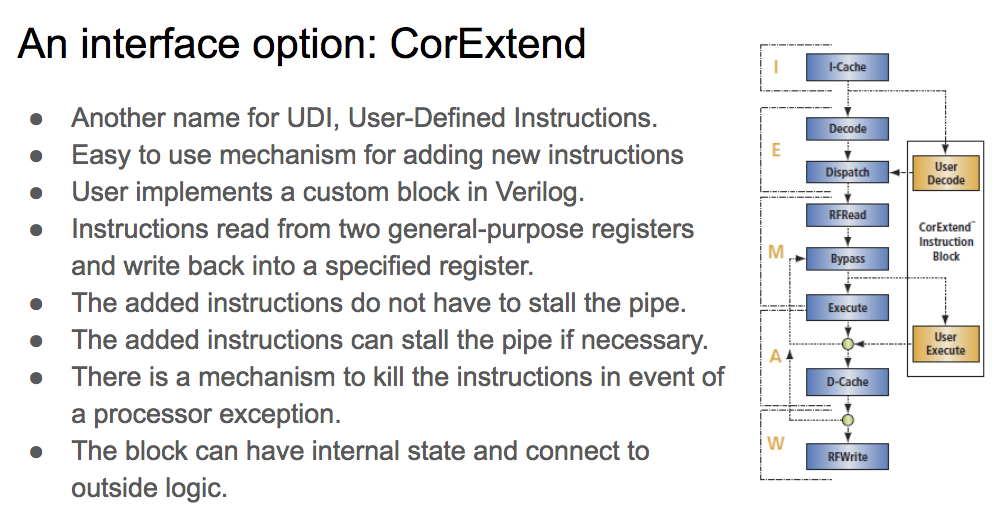

MIPSfpga ist ein Paket, das den Prozessorkern im Quellcode von Verilog enthält, den Sie ändern, neue Anweisungen hinzufügen, den Betrieb des Caches und der Pipeline beobachten, Multiprozessorsysteme erstellen, Software und Hardware gleichzeitig ändern usw. In der neuen Version des Seminars fügen Sie dem Prozessor einen Coprozessor hinzu, um Algorithmen für künstliche Intelligenz zu beschleunigen.

Darüber hinaus zeigen wir in der neuen Version des Seminars, wie der Kernel aus dem MIPS microAptiv UP-Paket konfiguriert und in die MIPSfpga-Bindung eingefügt wird. Wenn konfiguriert, können Sie exotische Prozessoroptionen erstellen, z. B. einen Prozessor mit 16 Sätzen von 32 Registern. Sie können diese Sätze beim Eingeben eines Interrupts automatisch wechseln und dadurch den Kontext schnell ändern, ohne den Kontext aus dem Speicher zu speichern / wiederherzustellen, was bei normalem RTOS etwa tausend Zyklen dauert.

MIPSfpga soll nicht vom absoluten Nullpunkt in ein Objekt injiziert werden. Für eine fruchtbare Verwendung ist es erforderlich, dass der Schüler die Grundlagen digitaler Schaltkreise bereits kennt, in C und Assembler programmieren kann und auch die Konzepte der Mikroarchitektur - Förderer, Pipelinekonflikte usw. - vorstellt. Dies wird an der SchuleMIPS studiert, die wir in Zelenograd verwenden.

Hier ist eine Folie über den Mechanismus zum Hinzufügen von Anweisungen zum MIPS microAptiv UP-Prozessor:

Bei einem Seminar in Las Vegas am 4. Juni und wahrscheinlich an einer Sommerschule für junge Elektronikingenieure, die vom 8. bis 26. Juli im MIET in Zelenograd stattfindet, wird mir meine Tochter Elizabeth Panchul helfen (wenn sie rechtzeitig ein Visum erhält). Da Elizabeth eine semi-russische-semi-russische / ukrainische ist, spricht sie nur Englisch. Daher können russische Lehrer (Studenten oder Doktoranden des Moskauer Instituts für Physik und Technologie, der Moskauer Staatsuniversität usw., die bereit sind, uns mit Elizabeth und dem MIET bei der Leitung der Schule zu helfen) den richtigen englischen Akzent von ihr und von ihnen lernen - die Grundlagen des Russischen. Zusätzlich zum Studium von Verilog, MIPS, Architektur, Mikroarchitektur und Organisieren von DMA im Speicher, wenn diese auf einem Grafikbildschirm angezeigt werden:

Wir erwarten Sie bei allen Seminaren sowie in Ausschüssen für die Erstellung ihrer Programme!