Mögliches Foto von 10 nm IceLake. Quelle

Mögliches Foto von 10 nm IceLake. QuelleAuf dem Prozessormarkt passieren seltsame Dinge. Der Weltmarktführer in der Person von Intel hat seit dem fünften Jahr Probleme, auf einen 10-nm-Herstellungsprozess umzusteigen. Zunächst kündigten sie den Übergang auf 10 nm im Jahr 2015 an, dann im Jahr 2016, 2017 ... In der Werft von 2019 und 10 nm von Intel in der Serie sind noch nicht da. Nun, nein, es gibt einige experimentelle / technische Proben, aber eine hohe Ausbeute ist ein Problem. Ein echter Übergang wird bereits

frühestens 2022 erwartet.

Tatsächlich war dies der Grund für den Mangel an Intel-Prozessoren auf dem Markt. Um dies zu überwinden, erweitert das Unternehmen die Produktion von modifizierten 14-nm-Prozessoren (derselbe See nur im Profil) und kehrt sogar auf 22 nm zurück. Es scheint, dass eine Regression offensichtlich ist. Derzeit berichten das koreanische Unternehmen Samsung, das taiwanesische Unternehmen TSMC und AMD, die sich der ZEN 2-Plattform angeschlossen haben, über die Einführung von bis zu 7 nm und stehen kurz vor der Umstellung auf 5 nm. Sie holten das „Mooresche Gesetz“ aus dem staubigen Schrank und erklärten es für lebendiger als alle Lebenden. Bald wird es 3 nm und 2 nm und sogar 1 nm geben (

sic! ) - pourquoi pas ?!

Was ist passiert? Wirklich

listige Asiaten schlagen die

verdammten Pendos in einer Schlüsselindustrie?

Kann ich Champagner öffnen?Haftungsausschluss: Ich habe

diesen Artikel zufällig gefunden und war äußerst erstaunt darüber, wie kompetent und detailliert er die Probleme der modernen Mikroelektronik aufdeckt, insbesondere den Tod von Moores Gesetz und Marketing. Es war einmal eine Zeit, in der ich selbst Artikel über die

Chipherstellung schrieb , und

in der Artikelserie „Inside Look“ habe ich sogar in sie hineingeschaut, das heißt, Das Thema ist für mich äußerst interessant. Natürlich möchte ich, dass

der Autor des Originalartikels ihn auf Habré veröffentlicht, aber im Zusammenhang mit der Beschäftigung hat er mir erlaubt, ihn hierher zu übertragen. Leider erlauben die Habr-Regeln kein direktes Kopieren und Einfügen, deshalb habe ich Links zu Quellen, Bildern und einem kleinen Gag hinzugefügt und versucht, den Text ein wenig zu begradigen. Ja, und ich kenne und respektiere Artikel (

1 und

2 ) zu diesem Thema aus der

Amartologie .

Lassen Sie uns das Problem gemeinsam lösen. Wir werden so viel wie möglich versuchen, uns mit Physik und Technologie zu befassen und nicht mit den Nuancen (deren Name Legion ist!). Die folgende Beschreibung ist vereinfacht und manchmal schematisch. Schreiben Sie Kommentare, wir werden versuchen, konstruktiv zu diskutieren.

Vorwort

"Nicht alles ist so einfach ...", pflegte die Tochter eines Offiziers zu sagen. Wenn Sie sich die Dichte der Transistoren ansehen, dann ist sie in der 14-nm-Technologie von Intel und der 7-nm-Technologie von TSMC fast gleich (

ooops !!! ). Und selbst der Rollback von Intel auf 22 nm hatte keinen großen Einfluss auf die Leistung. Was zur Hölle? Nach allen Regeln sollte der Übergang von der 14-nm- zur 7-nm-Technologie die Dichte der Transistoren um das Vierfache erhöhen. Und dies entspricht den Vorschriften von Gordon Moore, dessen

50. Jahrestag des Gesetzes kürzlich gefeiert wurde, und in der Nase der 55. Jahrestag!

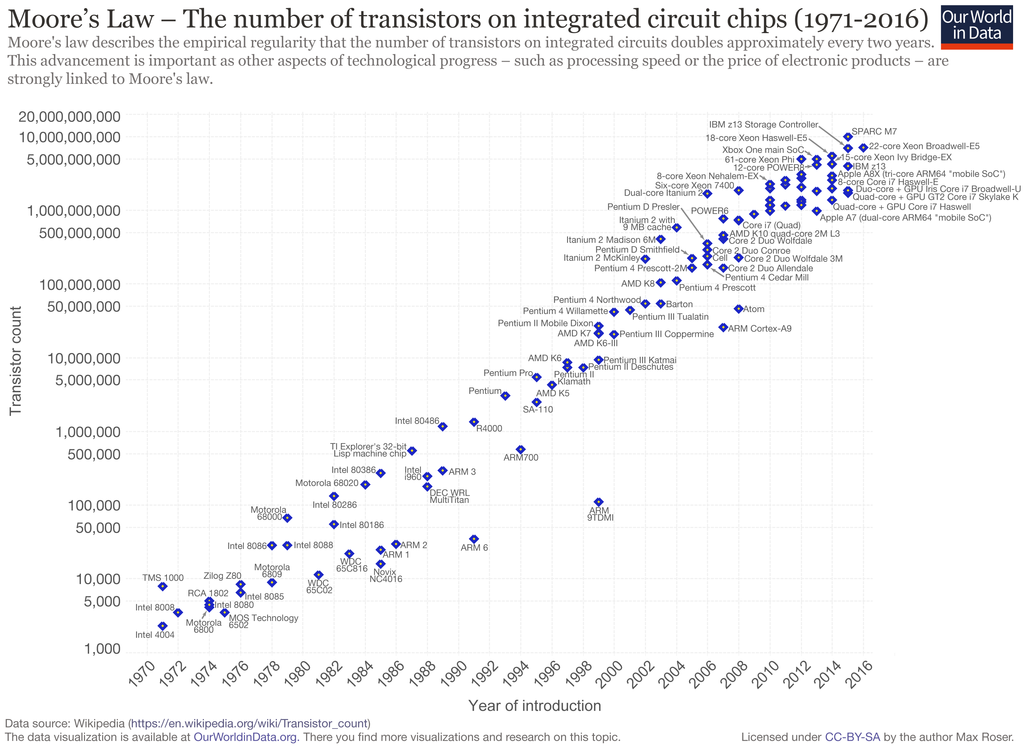

Moores Gesetz in Eisen gegossen. Wie Sie sehen können, „markieren“ wir seit ungefähr 5 Jahren vor Ort. Quelle

Moores Gesetz in Eisen gegossen. Wie Sie sehen können, „markieren“ wir seit ungefähr 5 Jahren vor Ort. QuelleGleichzeitig werden gemischte Aussagen gemacht. Einige argumentieren, dass das "Gesetz von Moore" relevanter ist als je zuvor, und die Mikroelektronik wird sich wie zuvor entwickeln. Brillante Wissenschaftler, Designer und Ingenieure werden alle Einschränkungen überwinden, sogar die Gesetze der Physik. Menschen brauchen neue Errungenschaften, und sie werden nicht lange brauchen.

Andere sagen, dass alle Jungs die physischen Grenzen erreicht haben, wir werden lecken, was ist, aber das ist normal. Dies wurde lange gewarnt. Der Leiter von NVIDIA

sagte während der CES 2019, dass Moores Gesetz tot ist und nun der Vektor (Huang sollte nicht im Vektor, sondern im Tensor sein) der Entwicklung geändert werden muss. Der Lithografiespezialist von AMD und GlobalFoundries

stimmt ihm zu.

Tatsächlich sind all diese technologischen Standards von Einheiten und zehn Nanometern seit langem von den physikalischen Dimensionen getrennt und zu mehr Elementen des Marketings geworden. Zumindest die letzten 15 Jahre: nach dem Übergang von 130 nm auf 90 nm. Es war dann, dass zum ersten Mal mit Einschränkungen nicht technologische, sondern grundlegende physikalische konfrontiert. Experten sprachen übrigens darüber, aber ihre leise Stimme wurde von den tapferen Sendungen von Vermarktern übertönt, die so taten, als sei nichts passiert, alles würde seinen eigenen Weg gehen, gemäß den Vorschriften von

Leni ... Dr. Moore.

Leider ist Moores Gesetz für Vermarkter und vielleicht zum Glück für uns kein Naturgesetz, sondern eine empirische Beobachtung, die 1965 von einem der Gründer von Intel, Gordon Moore, formuliert wurde. Nach seinen Beobachtungen kam im Abstand von einem Jahr eine neue Reihe von Mikroschaltungen heraus, während die Anzahl der Transistoren in ihnen um das Zweifache zunahm. 1975 wurde das Gesetz geändert, demnach sollte alle 24 Monate eine Verdoppelung erfolgen. Seitdem ist das Gesetz von Moore seit fast 40 Jahren zum Symbol und Banner für Hersteller digitaler Mikroelektronik erhoben worden, die manchmal verdreht sind (24 Monate wurden zu 36, jetzt stagnieren - siehe Bild oben).

Auf dem Weg entstanden verschiedene technologische Einschränkungen, die den Prozess verlangsamten (der gleiche Übergang durch die Beugungsgrenze). Oder Durchbrüche, die zu einem starken Anstieg der Miniaturisierung führten. Für einen externen Beobachter sah alles nach einem stabilen Wachstum aus, das dem Gesetz von Moore und nicht zuletzt den Bemühungen der Vermarkter entsprach.

Physik von "His Majesty Silicon"

Ich werde mit Silizium-Ode beginnen.

Silizium ist nur ein Geschenk des Himmels für Hersteller von Mikroelektronik. Nicht nur, dass Silizium buchstäblich unter den Füßen ein guter Halbleiter mit sehr geeigneten Parametern ist (in Bezug auf die Kombination von elektrischen, energetischen und physikalischen Eigenschaften). Reines Silizium ist fast ein Dielektrikum, die Leitfähigkeit wird vollständig durch die Konzentration der Verunreinigungen bestimmt. Es hat eine hohe Wärmeleitfähigkeit, ist technologisch fortschrittlich und beständig gegen aggressive Umgebungen.

Likbez für AnfängerSilizium ist bei gewöhnlichen Temperaturen ein Halbleiter mit einem kubischen Kristallgitter. 4 externe Elektronen von Siliziumatomen sind "sozialisiert", d.h. gehören zu allen Atomen des Kristallgitters. Sie sind nicht frei, aber nicht starr an ihr Atom gebunden. Dies ist ein Merkmal von Halbleitern. Für eine Weile drehen sich diese Elektronen um ihr Atom, werden dann auf das benachbarte übertragen und die benachbarten kommen an ihre Stelle. Externe (Valenz-) Elektronen wandern also zufällig von Atom zu Atom durch den Kristall (

Anmerkung: Nicht ganz so, die Elektronen selbst bewegen sich nicht, sie übertragen Energie nur durch Wechselwirkung miteinander ). Gelegentlich löst sich eine Art Elektron vollständig vom Atom und beginnt (quasi), sich frei zwischen den Kristallgittern zu bewegen. An seiner Stelle bleibt ein positives Siliziumion mit einer ungefüllten Elektronenlücke - ein „Loch“. Wenn die Elektronen das nächste Mal von einem Nachbarn weitergeleitet werden, ist die Lücke besetzt, aber sie erscheint beim Nachbarn, dann bei seinem Nachbarn usw. Das Loch beginnt sich auch zufällig durch den Kristall zu bewegen.

Wenn wir jetzt ein elektrisches Feld anlegen, fliegt ein freies Elektron von minus nach plus. Valenzelektronen sind ebenfalls der Wirkung des Feldes ausgesetzt und beginnen, freie Stellen schnell zur Plus-Seite zu füllen, und Loch-Stellen fließen zur Minus-Seite. Dieses Verhalten sieht so aus, als wäre ein Loch ein freier Ladungsträger, ein solches freies Elektron, nur mit einer positiven Ladung. Das Verhalten des Lochs wird durch dieselben Formeln wie das Elektron beschrieben, korrigiert um

eine größere „

effektive Masse “. Daher dämpfen sie oft nicht und betrachten Löcher der Einfachheit halber als gewöhnliche Elementarteilchen mit einer positiven Ladung.

Bei Raumtemperatur ist ein Elektron-Loch-Paar pro Billion Siliziumatome (Konzentration

10-12 ), aber reines Silizium bei Raumtemperatur ist ein Isolator (bedingt: Elektronen und Löcher vernichten sich zu schnell und haben keine Zeit, das Ende des Kristalls zu erreichen).

Wenn nun ein Atom mit 5 externen Elektronen, beispielsweise Phosphor, in das Siliziumgitter eingeführt wird, wird es in den 4-Elektronen-Austausch einbezogen und das fünfte Elektron wird frei. Aus freien Elektronen erhalten wir positive Phosphorionen und ein in Silizium eingebettetes „Elektronengas“. Die Leitfähigkeit von Silizium mit einer solchen Verunreinigung steigt linear an, Konzentrationen von einem Phosphoratom pro Million Siliziumatome (

ppm ) verändern die elektrischen Eigenschaften bereits dramatisch. Eine Beimischung von Phosphor wird als Donor bezeichnet, und der Halbleiter selbst wird als

Leitfähigkeit vom N-Typ bezeichnet . Zusätzlich zu Phosphor kann es Arsen oder Antimon sein.

Jetzt addieren wir zu reinen Siliziumatomen mit 3 externen Elektronen, zum Beispiel Bor. Es ist auch im 4-Elektronen-Austausch enthalten, kann aber nur 3 Elektronen ergeben. An benachbarten Siliziumatomen erscheint ein „Loch“ und macht sich auf den Weg durch den Kristall. Wir erhalten negative Borionen und ein positiv geladenes Lochgas. Eine solche Verunreinigung wird Akzeptor genannt, und der Halbleiter ist vom

P-Typ . Akzeptoren sind neben Bor Aluminium, Gallium und Indium.

Übrigens ist extrem reines Silizium (so dass es ein Isolator ist) unglaublich schwer zu bekommen. Das Vorhandensein von Bor macht Silizium

immer zu einem p-Halbleiter.

Ein Bonus für Silizium ist das Oxid - Siliziumdioxid SiO

2 . Es ist ein nahezu perfektes Dielektrikum mit hoher Festigkeit und Härte, das gegen alle Säuren außer Flusssäure (HF) beständig ist. Gleichzeitig löst Flusssäure das Silizium selbst nicht auf, Sie können keine Angst haben, überschüssiges Salz einzulegen. Selbst bei Raumtemperaturen (natürlich in Luft) bildet sich auf der Oberfläche von Silizium ein dünner Oxidfilm. Um dicke Oxidfilme zu erhalten, wird Silizium erhitzt oder eine Abscheidung bei niedriger Temperatur aus einem siliciumhaltigen Gas verwendet. Die Ausfällung wird verwendet, wenn bereits Schichten im Kristall abgeschieden sind und das Erhitzen zu einem "Verschmieren" der Topologie führt.

Langeweile eines Chemikers, einmal im Jahr des Periodensystems: Ein Schritt nach rechts - P, Phosphor, Oxid bildet Phosphorsäure, nach links - Al, Aluminium, Metall, Up - C, Kohlenstoff, Oxid - Gas, Down - Ge mit einer geringen Prävalenz in der Erdkruste (Kilo) kostet jetzt ~ 1k $).

Trotz ständiger Diskussion über das bevorstehende Ende der Silizium-Ära und den Übergang zu anderen Halbleitern beispielsweise Strukturen A

3 B

5 (Galliumaresenid, Galliumphosphid oder Galliumnitrid), Siliziumkarbid, Diamant,

Graphen und andere, da sie eine höhere effektive Elektronenmobilität aufweisen und Löcher, geringere Temperaturabhängigkeit, höhere Wärmeleitfähigkeit, Silizium herrscht in der Massenmikroelektronik.

Ja, für A

3 B

5 können Heteroübergänge erstellt werden . Dies ist der Fall, wenn sich die Bereiche innerhalb des Transistors nicht nur in der Art der Leitfähigkeit unterscheiden, sondern auch in der physikalischen Struktur, was zusätzliche Möglichkeiten bietet. Wenn andere Dinge gleich sind, können Galliumnitrid-Mikroschaltungen mit einer höheren Frequenz arbeiten, sind gegen hohe Temperaturen beständig und bieten eine bessere Wärmeableitung. Diese Materialien werden jedoch nur für diskrete Elemente und kleine Mikroschaltungen verwendet. Bei großen Mikroschaltungen sind die Preise aufgrund der Komplexität der Technologie um Größenordnungen höher als bei Silizium. Ja, und "andere gleich" wird nicht erhalten. Daher haben alternative Nicht-Silizium-Mikroschaltungen eine enge Spezialisierung.

MOSFETs

Betrachten Sie den Hauptbaustein digitaler Mikroschaltungen - einen planaren (flachen) Transistor mit einem induzierten Kanal. Er ist

MOS (Metalloxid-Halbleiter), er ist MIS (Metall-Dielektrikum-Halbleiter), er ist MOS (Metalloxid-Halbleiter), er ist

MOSFET .

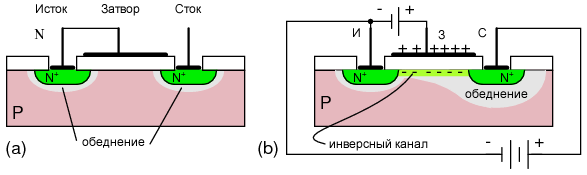

Schnittschema eines n-Kanal-Transistors

Schnittschema eines n-Kanal-TransistorsBeschreibung der ArbeitsprinzipienWir haben ein Siliziumsubstrat mit p-Leitfähigkeit. Es wurden 2 Schichten vom Typ n erzeugt - Source und Drain. Analoga von Emitter und Kollektor in

Bipolartransistoren . Zwischen ihnen ist eine Elektrode, die durch eine dielektrische Schicht (üblicherweise Siliziumoxid) von Silizium getrennt ist, ein Gate. Der Bereich unter dem Verschluss wird als Basis bezeichnet. Wenn wir eine Spannung zwischen Source und Drain anlegen, gibt es keinen Strom, da zwischen ihnen ein in Sperrrichtung vorgespannter

pn-Übergang besteht - der Transistor ist geschlossen. Schematisch ist dies ein Analogon einer Sperrdiode. Bei korrektem Anschluss ist dies ein Übergang zwischen der Basis und dem Abfluss.

Legen Sie nun eine positive Spannung an das Gate an. Ein elektrisches Feld geht durch das Oxid, dringt in Silizium ein, stößt Löcher (+) von der Oberflächenschicht des Lochs ab und zieht freie Elektronen (-) an. Letztere sind im p-Typ-Substrat vorhanden, obwohl nur wenige vorhanden sind. Bei einer bestimmten Spannung am Gate werden in der Oberflächenschicht der Elektronen mehr als Löcher. Inversion tritt auf und ein Kanal vom n-Typ erscheint unter der Oxidschicht. Es fließt ein Strom von Source zu Drain - der Transistor ist offen. Ein offener Transistor ist eine logische Einheit, ein geschlossener ist eine logische 0. Nun, oder umgekehrt, abhängig von der Implementierung.

Bei p-Kanal-Transistoren werden die n- und p-Bereiche vertauscht und der Transistor öffnet bei einer negativen Gate-Spannung.

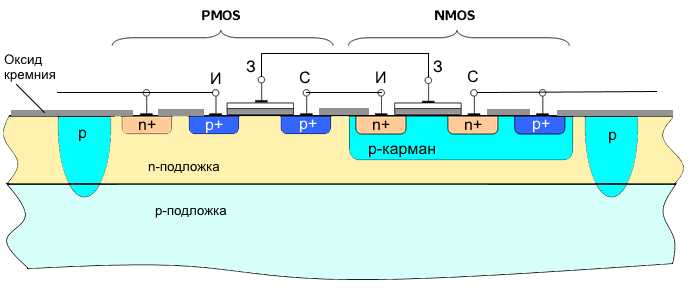

Die Vorteile von MOS-Transistoren sind die Kompaktheit. Es gibt aber auch einen schwerwiegenden Nachteil - einen hohen Stromverbrauch, da im offenen Zustand ein Durchgangsstrom durch den Transistor fließt. Daher dominieren seit den 1970er Jahren

CMOS-Transistoren (

komplementäre MOS ) in der digitalen Technologie. Dies sind in Reihe geschaltete p-Kanal- und n-Kanal-Transistoren mit kombinierten Gattern. Normalerweise in einer Zelle.

Wenn wir die Gates plus speisen - der n-Kanal-Transistor ist offen, ist der p-Kanal geschlossen. Es gibt keinen Durchgangsstrom minus am Ausgang. Wenn wir das Gate mit einem Minus versorgen - der n-Kanal-Transistor ist geschlossen, ist der p-Kanal offen. Es gibt wieder keinen Durchgangsstrom plus Ausgang. Das heißt, Das Element arbeitet auch als Wechselrichter.

Dies ist die energieeffizienteste Technologie. In einem statischen Zustand verbraucht das Element nichts (außer dem Streuleckstrom), nur der Schaltstrom wird verbraucht. Der Stromverbrauch ist fast direkt proportional zur Frequenz des Chips (Anzahl der Ladezyklen). Geringer Stromverbrauch und Kompaktheit bestimmten die Dominanz der CMOS-Technologie in der digitalen Elektronik.

Bipolartransistorschaltungen lieferten anfangs eine höhere Leistung, waren jedoch komplexer, nahmen mehr Platz ein und verbrauchten eine Größenordnung mehr Energie. Ich muss sagen, dass sich die Entscheidung für CMOS voll ausgezahlt hat. Es wäre fast unmöglich, solche Eigenschaften wie die heutigen Prozessoren auf andere Technologien zu übertragen. Und während Alternativen am Horizont nicht sichtbar sind.

Topologiefunktionen

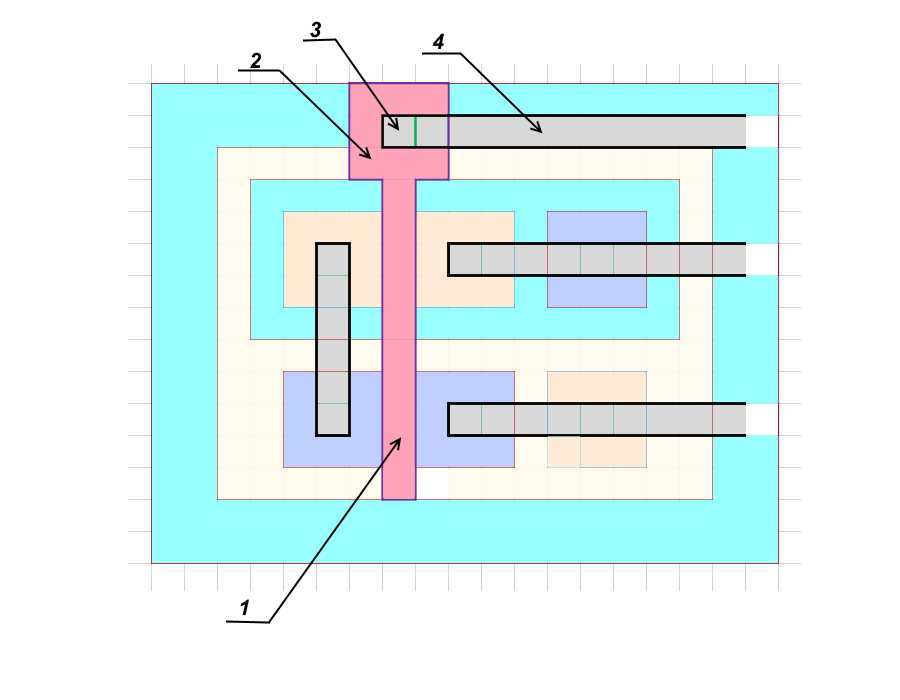

Die Chip-Topologie des Chips kann herkömmlicherweise als großes Blatt Papier in einer Zelle dargestellt werden, wobei die Grenzen der Bereiche entlang der Linien gezeichnet sind und die technologische Größe die Größe der Zelle ist. Tatsächlich können Sie für unkritische Elemente auch eine halbe Zelle einrücken (die Regel von zwei Lambdas), aber dies sind Nuancen.

Detailliertes TopologiedesignGehen wir mental auf das Ende der 1980er Jahre zurück, als die Technologien noch einfach und verständlich waren. Betrachten Sie ein reales Paar CMOS-Transistoren. Windows n + und p + sind hoch dotiert (1 Verunreinigungsatom pro mehrere hundert oder sogar zehn Siliziumatome), d.h. Der Gehalt an Verunreinigungen ist um Größenordnungen höher als nur n und p.

Angenommen, wir hätten TK erhalten, um die Topologie eines solchen Transistorpaares in eine isolierte Tasche zu zeichnen. Da es keine großen Ströme durch Transistoren gibt, berechnen wir basierend auf der kleinstmöglichen technologischen Größe, dem sogenannten technischen Abstand. Nennen Sie es d.

Profil

Profil Blick von oben

Blick von obenBeginnen wir mit dem Kontaktfenster für die Quelle des n-Kanal-Transistors

(1) . Wir machen es zum kleinstmöglichen

d * d .

Die Quelle

(2) hat dann die Größe

3d * 3d (Sie müssen mindestens von den Rändern des Fensters zurücktreten).

Die Basis

(3) besteht aus der Mindestbreite

d .

Weiterhin ist der Bestand

(4) mit seinem Kontaktfenster ebenfalls

3d * 3d .

Das letzte Element ist die hochlegierte Zone

(5) für den Kontakt mit der p-Basis sowie

3d * 3d . Es ist erforderlich, die Spannung von Quelle und Basis auszugleichen, damit das spontane Auftreten des Kanals nicht auftritt.

Zeichnen Sie die Ränder der p-Tasche selbst

(6) , ein weiteres

d aus den gezeichneten Fenstern. Die Größe des p-Fensters beträgt

5d * 13d .

Unten zeichnen wir einen p-Kanal-Transistor. Wir treffen diese Anordnung, um das gesamte Element auf eine quadratische Form zu bringen - es ist einfacher zusammenzubauen.

Wir ändern die Position von Source und Drain. Diese Anordnung minimiert die Länge der Kontaktmetallschienen. Beginnen wir mit dem Kontaktfenster für den Abfluss

(7) , die Größe ist minimal -

d * d .

Der Drain

(8) ist

3d * 3d , die Basis

(9) hat die Breite

d und stimmt mit der Basis des n-Kanal-Transistors überein. Die Quelle

(10) und die hochlegierte Kontaktfläche zur Basis

(11) sind ebenfalls

3d * 3d .

Die letzte Größe ist der minimale Einzug zum Teilungspfad

(12) , ein weiterer

d .

Insgesamt erhielt die Größe des Transistorpaares

11d * 15d . Die separate Spur ist in unserem Fall eine andere Region vom p-Typ, die mit einem n-Substrat einen in Sperrrichtung vorgespannten pn-Übergang bildet.

Es gibt eine weitere Möglichkeit zur Isolierung mit einem Dielektrikum - Siliziumdioxid SiO

2 oder Saphir Al

2 O

3 . Die letztere Option ist vorzuziehen, aber deutlich teurer. In diesem Fall können die Bereiche nahe dem Teilungspfad gebildet werden und der Leckstrom zwischen den Zellen ist Null. Typischerweise ist die Breite der Trennspur etwas größer als die Dicke der Epitaxieschicht (mehr dazu weiter unten) und ist gleich

2d .

–

13d*17d .

(1)

(1) ,

(2) (3) .

–

(4) . (

), , .

,

3 .

11d*15d , ,

33*45 . ,

1,5 .

16,5*22,5 . , , . , ( ). , . . .

, . .

( )? .

(

). , (

.: , () , , , , .

CorneliusAgrippa :

, , (, ). , ). (boule) 200 300 , (

aka wafers ) 0,5-0,7 . . 450 , . ( , ).

, — . : , (SiCl

4 ). . , . p- n-. n- p-. .

, , p-, . , , , .

.

, 700 .

, , . . , , . , . , .

. , , . , . , , . .

, . , , . . , . , , .

, , ,

.

tnenergy .

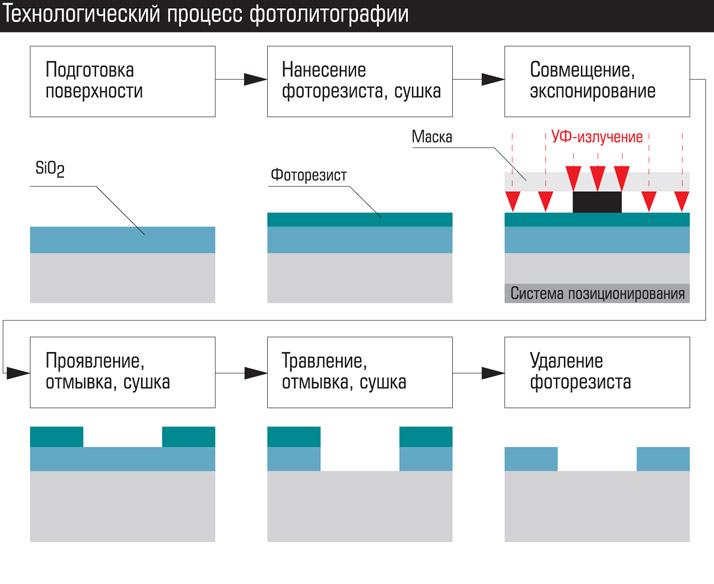

– . . ().

:

- .

- – . , .

- . – . , , p- . ( .: -) .

- . . , ( ) ( ). .

- – .

- . . , , ( shadowing effect).

- .

Am Ende der Operation erhalten wir eine Platte mit entfernten Oxidanteilen, die zur Diffusion, Ionenimplantation oder Metallabscheidung (

Hinweis: oder galvanische Abscheidung) geschickt werden kann. Nach dem Erzeugen der Schicht wird das Oxid normalerweise aus dem gesamten Bereich der Platte geätzt und ein neues abgeschieden.

Windows erstellen von breit bis schmal. In unserem Fall ist die Reihenfolge wie folgt: Trennbereiche, p-Taschen, p + Schichten, n + Schichten, Kontaktfenster mit Metallisierung, Aufbringen des Verschlusses, Kontaktbereiche des Verschlusses, die erste Schicht von Metallspuren mit Kontaktbereichen unter der zweiten Schicht, die zweite Schicht der Metallisierung usw. . In modernen Prozessoren beträgt die Metallisierung bis zu 10-15 Schichten.

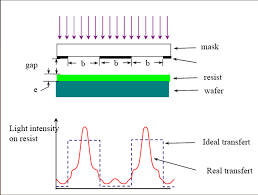

Die Kontaktphotolithographie wurde zu Beginn der Mikroelektronik eingesetzt. Jetzt ist die Hauptsache die Projektionsphotolithographie. Dies ist der Fall, wenn ein Linsen- und Spiegelsystem zwischen der Strahlungsquelle und der Fotomaske platziert wird, um einen sich verengenden Photonenstrahl zu erzeugen. In der folgenden Abbildung sind schematisch unterschiedliche Methoden der Fotolithografie dargestellt: Kontaktphotolithografie mit einer Lücke, Projektion durch Linsen, Projektionsspiegel.

Die Vorteile der Fotolithografie sind hohe Geschwindigkeit und niedrige Kosten. Der gesamte Plattenbereich mit all seinen Mikroschaltungen wird auf einmal freigelegt, und der Vorgang dauert mehrere Minuten. Oder ein Quadrat aus mehreren Mikroschaltungen, gefolgt von einer Plattenverschiebung.

Neben der Fotolithografie gibt es noch andere Arten - elektronische, Röntgen- und ionische. Am interessantesten ist die elektronische Lithographie (zum Beispiel das Mapper-Projekt, über das

BarsMonster geschrieben hat ).

Bei der elektronischen Lithographie erfolgt die Belichtung des Resists nicht durch Licht, sondern durch einen Elektronenstrahl. In seiner einfachsten Form ähnelt es der Bilderzeugung auf

CRT- Bildröhren. Von allen Arten der Lithographie liefert die elektronische Lithographie das klarste Bild und die höchste Auflösung. Der Nachteil ist die lange Belichtungszeit. In modernen Technologien hat der Elektronenstrahl eine Dicke von wenigen Nanometern und sogar Bruchteile von Nanometern, und der Plattendurchmesser beträgt 300 mm. Natürlich wird nicht ein Bündel verwendet, sondern Zehntausende, die von einem Computer gesteuert werden. Es ist jedoch ein sehr starker Gesamtelektronenfluss erforderlich. Zum Vergleich beträgt die Energie des UV-Strahlungsquanten mehrere

eV , die Elektronenenergie im Strahl mehrere tausend Elektronenvolt.

Außerdem sind die Elektronen elektrisch geladen und stoßen sich gegenseitig ab, was zu einer Strahldivergenz führt. Natürlich ist es möglich, die Geschwindigkeit von Elektronen zu erhöhen, aber dann durchdringen sie den Resist oder reflektieren mit hoher Geschwindigkeit in beliebige Richtungen, was Sekundärstrahlung (

Sekundärelektronen ) und dementsprechend Belichtung verursacht. All dies schränkt den Einsatz von Technologie ein.

Mit der elektronischen Lithographie werden Fotomasken erstellt. Die Belichtungszeit für eine Fotomaske beträgt mehrere Tage. Daher dominiert die Photolithographie bei der Herstellung von Mikroschaltungen.

Ein moderner Satz von Fotomasken für einen Prozessor kostet mehrere zehn Millionen Dollar. Angesichts der Tatsache, dass moderne Prozessoren Milliarden von Transistoren enthalten und sich Hunderte von Prozessoren auf der Platte befinden, ist dies nicht überraschend. Darüber hinaus sind die Fenster in der modernen Fotomaske nicht nur Löcher im Material, sondern häufig auch andere Materialien mit spezifischen optischen Eigenschaften. Ein realer Satz von Fotomasken besteht aus Dutzenden von Masken. Zu den neuesten Herstellungsprozessen mehr als 50 (

sic! ).

Mit ihnen können Sie jedoch Mikrochips wie heiße Kuchen stempeln. Während der Lebensdauer können Sie mit einer Reihe von Fotovorlagen Hunderttausende oder sogar Millionen von Mikrochips an der Ausgabe abrufen.

Was begrenzt also die Größe der Prozesstechnologie?

4 Gruppen von Faktoren können bedingt unterschieden werden:

- Hardware und Technologie. Verbunden mit der Hardware-Auflösung.

- Physik technologischer Prozesse. Es wird durch die physikalischen Einschränkungen eines bestimmten Prozesses bestimmt, die durch eine Änderung der Technologie oder der Materialien umgangen werden können.

- Körperlich. Dies sind Einschränkungen, die nicht umgangen werden können, deren Auswirkungen jedoch minimiert werden können.

- Extrem körperlich.

Hardware- und Technologieeinschränkungen

Diese Art der Einschränkung war in den frühen Stadien der Mikroelektronik entscheidend. Bezieht sich hauptsächlich auf die Herstellung von "Reinräumen", hoch entwickelten Geräten für technische Prozesse und Instrumenten (die für die Qualitätskontrolle von Produkten wichtig sind). Beispielsweise erfordert die Fotolithografie eine hochpräzise Optik, leistungsstarke Mikroskope, Mechanismen zum Kombinieren von Masken und Platten mit einer Genauigkeit von Bruchteilen von Nanometern, eine hochreine Atmosphäre oder ein Vakuum während der Belichtung usw. Es ist notwendig, den Parametern technologischer Prozesse - Temperatur, Dauer, Zusammensetzung der Atmosphäre, Strahlungsleistung, Oberflächenvorbereitung - sehr genau standzuhalten.

Jetzt ist die Genauigkeit der Ausrüstung kein begrenzender Faktor. Nicht weil es ein einfaches Problem ist. Es reicht aus, ein Diagramm einer modernen Projektions- oder Spiegelphotolithographie zu betrachten, um den Grad der Komplexität zu verstehen. Aber hier ist wirklich der Fall, wenn es keine Hindernisse für talentierte Designer und Ingenieure gibt.

Probleme mit der Technologie sind normalerweise in der ersten Serie relevant. Mit einer Änderung der technischen Prozessnorm ändern sich nicht nur die horizontalen, sondern auch die vertikalen Abmessungen, die Konzentration der Verunreinigungen und die Anteile der aktiven Zonen. Und jetzt ändert sich mit jedem neuen Schritt auch die Physik der Prozesse. Natürlich werden alle Parameter vorab berechnet und modelliert, aber die Realität nimmt immer Anpassungen vor. Daher wird für die erste Serie eine Ausbeute von 3% geeigneter Schaltungen (97% defekt) als Norm angesehen. Allmählich werden technologische Prozesse optimiert und der Prozentsatz der für die letzte Serie geeigneten Ausbeute beträgt über 90%.

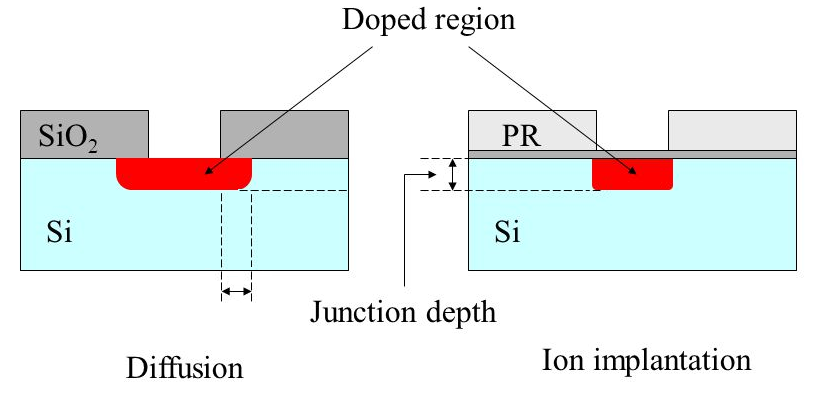

Physik technologischer Prozesse

Seit mehr als 30 Jahren, bis vor kurzem, waren es diese Faktoren, die einschränkend waren. Ich habe bereits einige dieser Einschränkungen aufgeführt - das Eindringen von Verunreinigungen unter das Oxid während der Diffusion, das Nagen des Oxids unter dem Fotolack während des Ätzens und die Erosion bereits abgeschiedener Schichten während thermischer Prozesse.

Lösungsverfahren werden ebenfalls teilweise beschrieben.

Die Diffusion wurde durch Ionenimplantation ersetzt. Außerdem wurde für die kleinsten Schichten das Verunreinigungsmaterial geändert - anstelle von Phosphor wird Arsen anstelle von Galliumbor verwendet. Ihre Atome sind größer und schwerer, daher lösen sie sich bei gleichen Temperaturen schlechter in Silizium auf (und vor allem ist es für sie schwieriger zu diffundieren!). Für die Ionenimplantation ist dies nicht wichtig, aber beim anschließenden Erhitzen erodieren solche Schichten viel schwächer.

Die Erzeugung von Oxid durch Erhitzen hat die katalytische Abscheidung bei niedriger Temperatur aus Gas ersetzt. Heizung wird verwendet, aber nur am Anfang, während der Kristall sauber ist. Bei einigen Operationen werden Siliziumnitrid (Si

3 N

4 ) oder aufeinanderfolgende Schichten aus Oxid und Nitrid anstelle von Oxid verwendet.

Das Ätzen mit flüssiger Säure wurde in Ionenätzen geändert. Säure wird nur verwendet, um Oxid aus dem gesamten Bereich zu entfernen.

Ein weiteres Problem war die Herstellung von Reinstoxid für ein Gate-Dielektrikum. Dieses Oxid bleibt als Arbeitselement auf dem Chip und stellt hohe Anforderungen an Reinheit und Gleichmäßigkeit. Die Oxiddicke beträgt stellenweise weniger als 10 Atomlagen. Ein kleiner Defekt führt zu einer Reifenpanne oder einem Ausfall. Dies führt zu einem elektrischen Verschluss des Verschlusses zur Basis und zum Ausfall des Elements. Für einige Zeit wurde ein Wechsel einer Schicht aus Oxid und Siliziumnitrid verwendet. In der 90-nm-Technologie wurde Hafniumoxid HfO

2 als Gate-Dielektrikum verwendet.

Übrigens waren es während der UdSSR genau die Probleme bei der Gewinnung von hochwertigem Oxid, die den Übergang zu CMOS verlangsamten. Daher die Suche nach alternativen Wegen und die allgemeine Verzögerung in der digitalen Mikroelektronik.

Der kritischste Vorgang ist die Fotolithografie. So sehr, dass bisher viele ein Gleichheitszeichen zwischen der Auflösung des gesamten technischen Prozesses und der Auflösung der Fotolithografie gesetzt haben. Das Hauptproblem der Fotolithografie seit den späten 1980er Jahren ist die Beugung von Licht. Genauer gesagt, ultraviolette Strahlung, obwohl das Prinzip dasselbe ist. Es wäre nicht übertrieben zu sagen, dass der Kampf um die Verkleinerung technologischer Prozesse 30 Jahre lang in erster Linie ein Kampf gegen die Beugung war.

Die Beugung des Lichts wurde bereits im 18. Jahrhundert von den Vätern der Begründer der Optik entdeckt:

Beim Eindringen in das Loch weichen die Lichtstrahlen und jede andere elektromagnetische Strahlung (EMP) vom geraden Weg ab, divergieren und dringen in den Schattenbereich ein. Das Phänomen wird bei Lochgrößen nahe der Wellenlänge beobachtet. Je kleiner das Loch im Vergleich zur Welle ist, desto stärker ist die Dispersion. Die Regel gilt bis zu viertel Wellenlängenlücken. Das Loch ist weniger als ein Viertel der Wellenlänge, der EMP-Strahl „sieht nicht“ und wird von der Oberfläche mit so kleinen Lücken wie von einem festen reflektiert.

Die Wellenlänge von Silizium-LEDs beträgt ca. 1 μm (nahes Infrarot), die Wellenlänge von sichtbarem Licht von 780 nm (rot) bis 380 nm (lila). Bei weniger als 380 nm beginnt die ultraviolette Strahlung (UV). Die heute in der Photolithographie verwendeten Emitter haben eine Wellenlänge von 248 nm und 193 nm, dies ist die Strahlung von Excimerlasern (zum Beispiel

auf XeF 2 ). Dementsprechend stiegen die Beugungsprobleme nach Überwindung des 3-Mikron-Technologie-Balkens auf ihre volle Höhe und wurden nach 800 nm dominant. Aufgrund der Beugung während der Belichtung tritt das UVI unter einer undurchsichtigen Maske in den Bereich ein und beleuchtet den Fotolack im Schatten. Als Ergebnis erhalten wir anstelle eines klaren Quadrats einen verschwommenen Pfannkuchen.

Zusätzlich zur Erosion von Fenstern gibt es den Effekt überlappender (Interferenz-) Seitenwellen für eng beabstandete Fenster. Flare-Peaks erscheinen weit unterhalb des reflektierenden Teils der Fotomaske.

Optik - herzlos du ...Mit welchen Methoden wird dieses Phänomen bekämpft?

Optik - herzlos du ...Mit welchen Methoden wird dieses Phänomen bekämpft?Der erste Schritt war die Verwendung der Projektionsphotolithographie. Bei starker Vereinfachung ist zwischen der Fotomaske und der Platte eine Linse installiert, die divergierende Strahlen sammelt und auf den Fotolack fokussiert.

Eine andere Methode bestand darin, die Wellenlänge der Belichtungsstrahlung zu verringern. Zu einer Zeit begannen sie mit Quecksilberbogenlampen mit einer Strahlungswellenlänge von 436 nm - das ist blaues Licht. Dann 405 nm (violett), 365 nm (nahe ultraviolett). Damit endete die Ära der Quecksilberlampen, der Einsatz von Excimerlasern begann. Zuerst 248 nm (mittleres Ultraviolett), dann 193 nm (tiefes Ultraviolett). Auf diesen Prozess und ins Stocken geraten.

Tatsache ist, dass sie die Transmissionsgrenzen der Quarzoptik erreicht haben. Kürzere Wellen absorbieren Quarz. Es war notwendig, entweder auf Spiegelsysteme umzusteigen oder Linsen aus anderen Materialien zu verwenden. Experimentelle Installationen bei 157 nm wurden basierend auf einer Calciumfluoridoptik durchgeführt. Sie gingen jedoch nie in die Serie. Da gab es Möglichkeiten zur Optimierung der 193 nm Lithographie.

Visuelle Infografiken auf Lasern.

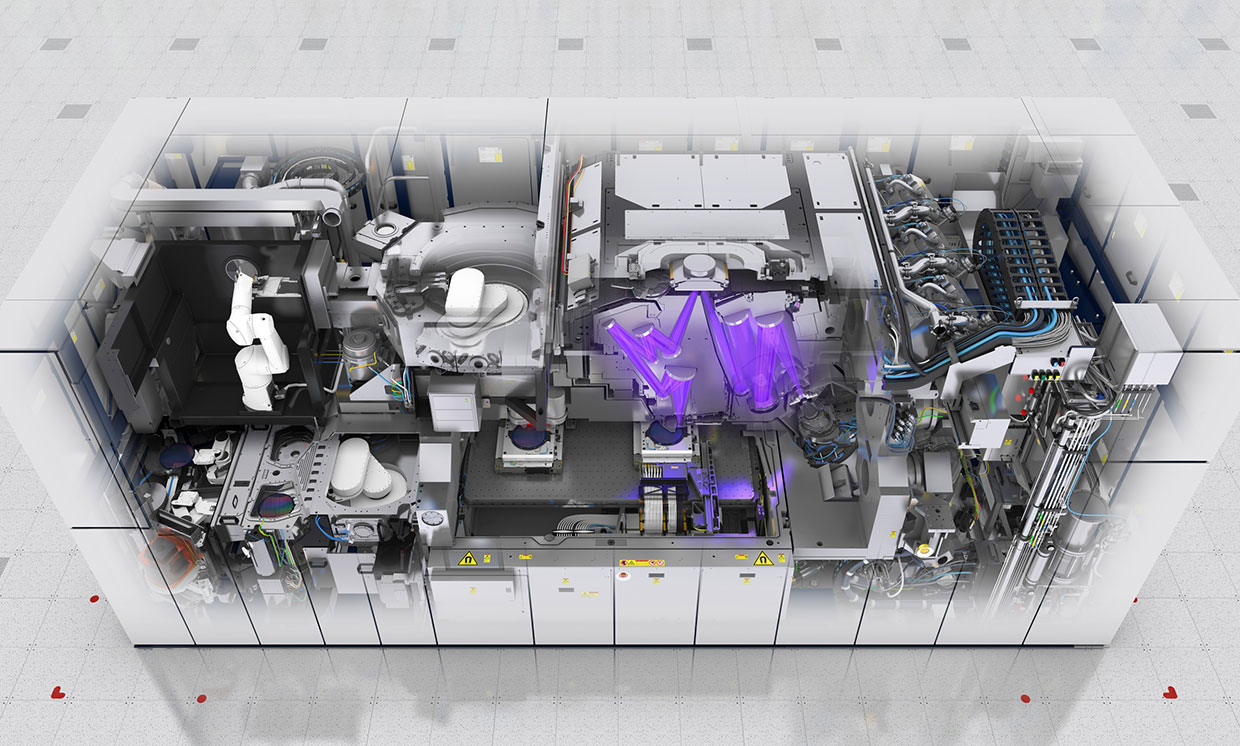

QuelleEUV-Lithographie

Mitte der neunziger Jahre entwickelten sie eine Standardphotolithographie auf extremem Ultraviolett (

EUV-Lithographie ) mit einer Wellenlänge von 13,5 nm. Diese Wellenlänge ermöglichte es, eine Auflösung in Einheiten von nm zu erhalten.

In den frühen 2000er Jahren erschienen die ersten experimentellen Proben.

Ende der 2000er Jahre sollte die Technologie in eine Reihe gehen. Und schließlich kam die Nachricht, dass Samsung und die taiwanesische TSMC 2019 auf EUV-Lithografie umsteigen werden. Weniger als 15 Jahre sind vergangen (

sic! ). Intel wurde zum Hauptgegner der EUV-Lithographie, obwohl es ursprünglich einer der Initiatoren war. Als sie erkannten, dass alles, was möglich war, aus dem UVI von 193 nm herausgedrückt wurde, kündigten sie den Übergang zu 126 nm an (ha ha!).

Was ist der Grund für diese Ablehnung?Tatsache ist, dass 13,5 nm bereits praktisch Röntgenstrahlung ist. Die Grenze zwischen UVI und Röntgenstrahlung wird üblicherweise als 10 nm angesehen, aber Ultraviolett unterscheidet sich nicht von weichem Röntgenstrahl im Verhalten von 13,5 nm. Daher ähnelt die EUV-Lithographie eher der Röntgenstrahlung. Linsen für eine solche Wellenlänge existieren in der Natur nicht, daher ist es notwendig, von heterogenen Metallschichten auf Spiegel umzuschalten.

Metallspiegel erzeugen nicht nur eine sehr dünne und komplexe Struktur, sondern absorbieren auch den größten Teil der Strahlung. Einheiten von Prozent der anfänglichen Strahlungsleistung erreichen den Fotolack. Wenn wir berücksichtigen, dass der Wirkungsgrad des Emitters selbst ebenfalls einige Prozent beträgt, sind zur Erzielung einer normalen Belichtungszeit eine hohe Leistung und ein hoher Energieverbrauch

erforderlich (

ooops! ).

Dies ist der ASML EUV-Scanner

Dies ist der ASML EUV-ScannerDie Strahlungsquelle ist Plasma. Eine sehr launische Substanz, aus der es schwierig ist, ohne Pulsationen einen gleichmäßigen Fluss zu erreichen. Sogar Luft absorbiert aktiv 13,5 nm, so dass die Belichtung nur im Vakuum erfolgen kann.

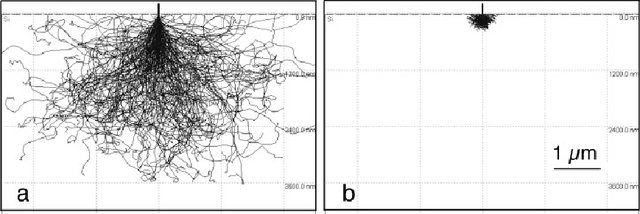

Das Problem bei der Auswahl des Fotolacks. Je kürzer die Wellenlänge ist, desto höher ist die Photonenenergie. Frühere Quellen gaben Energie in Einheiten von Elektronenvolt an, dies ist die übliche Energie chemischer Reaktionen. Die Photonenenergie für eine Welle von 13,5 nm beträgt 92 Elektronenvolt. Dies ist die Bindungsenergie tiefer Elektronen. Wenn ein solches Photon absorbiert wird, wird das Elektron sehr "heiß", beginnt zu rasen, strahlt überschüssige Energie ab und verursacht eine sekundäre Belichtung vom Fenster weg. Daher ist die Auswahl eines Fotolacks mit dem gewünschten Parametersatz ebenfalls eine schwierige Aufgabe.

Monte-Carlo-Simulationsergebnisse der Elektronenbewegung in Silizium mit Energien von 20 und 5 eV. Quelle

Monte-Carlo-Simulationsergebnisse der Elektronenbewegung in Silizium mit Energien von 20 und 5 eV. QuelleDiese Schwierigkeiten bestimmten die Gründe, warum sie den Übergang zu EUV auf den letzten verschoben haben.

Aktuelle Methoden zur Bekämpfung der Beugung

Daher wurde bis vor kurzem derselbe UVI mit einer Wellenlänge von 193 nm als Strahlungsquelle verwendet. Bis zur Technologie von 10 nm und 7 nm. Und jetzt erinnern wir uns, dass Strahlung den Spalt nicht durchdringen kann, wenn seine Breite weniger als ein Viertel der Wellenlänge beträgt. Für 193 nm sind es 48 nm. Die Frage stellt sich -

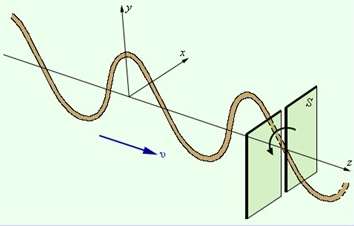

WIE ?!Dies ist das kleine Wunder, das die Ingenieure getan haben. Sie verwendeten die Strahlungspolarisationsmethode.

Wir nehmen einen rechteckigen schmalen Spalt (mit einer Breite von weniger als einem Viertel der Wellenlänge) und richten Licht darauf, das entlang der Achse polarisiert ist. Licht wird durch den Spalt hindurchtreten, selbst die Beugung in Querrichtung wird vernachlässigbar sein.

Und jetzt nehmen wir 2 senkrechte Schlitze: horizontal und vertikal. Zuerst bestrahlen wir einen Zweikomponenten-Fotolack mit polarisiertem Licht durch einen vertikalen Spalt und dann durch einen horizontalen. Es erscheint nur der zweimal bestrahlte Bereich. Genau wie alle genialen.

Richtig, Sie müssen zweimal mehr Fotovorlagen und zwei Belichtungsprozesse verwenden, um ein Fenster zu erstellen. Aber Sie können die gute alte Quarzoptik und bewährte Fotolacke jahrelang verwenden.

Das ist eine Wendung!Es gibt andere Möglichkeiten, die Beugung zu bekämpfen ...

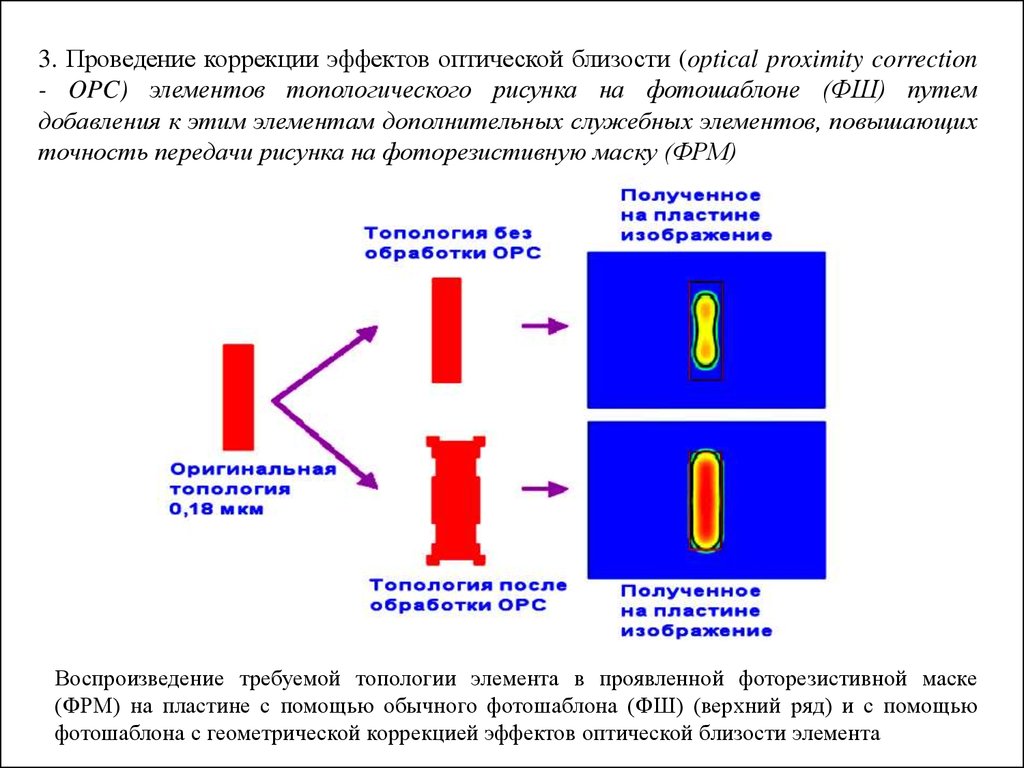

Optische Näherungskorrektur. Die Form der Fenster der Fotomaske ist nicht rechteckig, um Defekte während der Beugung auszugleichen.

Das optische Näherungskorrekturverfahren ist schematisch ...

Die Verwendung von Phasenverschiebungsmasken. An den Seiten des Hauptfensters der Fotomaske befindet sich ein Hilfsmittel, dessen Material die Phase der Welle verschiebt. Wenn Wellen angelegt werden (

Interferenz ), schneiden sie seitliche Verschiebungen teilweise voneinander ab.

Off-Axis-Beleuchtung.

Off-Axis-Beleuchtung. Der Strahl fällt nicht senkrecht zur Oberfläche der Platte, sondern aus zwei Quellen in einem leichten Winkel. Beim Aufbringen von Quellen werden seitliche Verschiebungen teilweise kompensiert.

Mehrfachbelichtung. Zum Beispiel müssen wir sechs nahe gelegene Fenster belichten. Zuerst fahren wir die Belichtung von 1, 3 und 5 Fenstern. Und dann 2, 4 und 6. Dies erhöht die Anzahl der Belichtungszyklen und Fotovorlagen um das Zweifache, aber immer noch besser als nichts. Angesichts der horizontalen und vertikalen Polarisation erhalten wir 4 Belichtungszyklen, um eine Schicht zu erzeugen.

Wenn wir uns also die moderne Fotomaske ansehen, sehen wir die Bereiche der Mikroschaltung nicht in expliziter Form. Es wird eine Reihe horizontaler und vertikaler Figuren geben, die, wenn sie überlagert werden, ein Bild ergeben. Eigentlich solide chinesische Schriftzeichen: Vielleicht haben die Chinesen deshalb die Produktion von Mikroelektronik besetzt ?!

Nach 45 nm wechselten sie zur Immersionsphotolithographie. Dies ist der Fall, wenn der Raum zwischen der extremen Linse und dem Fotolack mit Flüssigkeit gefüllt ist. Zuerst war es Wasser. Jetzt spezielle Flüssigkeiten mit einem hohen Brechungsindex (bis zu 1,8). Die Flüssigkeit reduziert die effektive Wellenlänge und neutralisiert die Lichtbrechung an der Grenzfläche des Mediums.

So erreichten sie die Auflösung von ~ 10 nm. Dies scheint jedoch die Grenze für die 193-nm-Lithographie zu sein.

Foto der ersten Metallisierungsschicht für die 24-nm-Technologie. Links erstellt durch 193 nm Lithographie, rechts experimentell 13,5 nm (EUV). Wie Sie sehen können, gibt es von den vorherigen klaren rechteckigen Formen nur Erinnerungen. Funktioniert immer noch.

Foto der ersten Metallisierungsschicht für die 24-nm-Technologie. Links erstellt durch 193 nm Lithographie, rechts experimentell 13,5 nm (EUV). Wie Sie sehen können, gibt es von den vorherigen klaren rechteckigen Formen nur Erinnerungen. Funktioniert immer noch.Über körperliche Einschränkungen, wie sie sich auswirken und wie sie die Produktion

im zweiten Teil in ein paar Tagen verändert haben - bleiben Sie dran!

Vergessen Sie nicht, den

Blog zu abonnieren: Es ist nicht schwer für Sie - ich freue mich!

Und ja, bitte schreiben Sie über die Mängel, die im PM-Text vermerkt sind.