Im

ersten Teil haben wir kurz die Siliziumphysik, die Mikroelektroniktechnologie und die technologischen Grenzen untersucht. Lassen Sie uns nun über physikalische Einschränkungen und physikalische Effekte sprechen, die sich auf die Größe der Elemente in einem Transistor auswirken. Es gibt viele von ihnen, also gehen wir die wichtigsten durch. Hier muss man in die Physik einsteigen, sonst nichts.

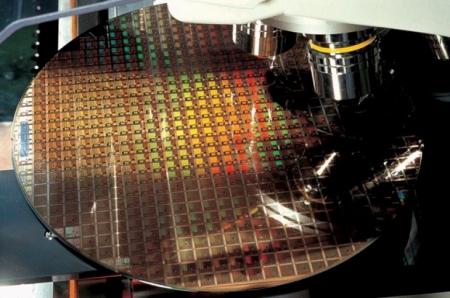

Haftungsausschluss: Es war einmal

, als ich Artikel über die

Herstellung von

Chips schrieb , und

in der Artikelserie „Inside Look“ habe ich sogar in sie hineingeschaut, d. H. Das Thema ist für mich äußerst interessant. Natürlich möchte ich, dass

der Autor des Originalartikels ihn auf Habré veröffentlicht, aber im Zusammenhang mit der Beschäftigung hat er mir erlaubt, ihn hierher zu übertragen. Leider erlauben die Habr-Regeln kein direktes Kopieren und Einfügen, deshalb habe ich Links zu Quellen, Bildern und einem kleinen Gag hinzugefügt und versucht, den Text ein wenig zu begradigen. Ja, und ich kenne und respektiere Artikel (

1 und

2 ) zu diesem Thema aus der

Amartologie .

Physikalische Effekte in der Mikroelektronik

Die Reihenfolge der Grundmengen für Silizium

Die Konzentration der Siliciumatome im Kristall beträgt 10

22 cm

-3Konzentration der intrinsischen Elektronen und Löcher bei Raumtemperatur - 10

10 cm

-3Konzentration von Verunreinigungsatomen aus leicht dotierten Bereichen - 10

16 -10

18 cm

-3Konzentration von Verunreinigungsatomen aus stark dotierten Regionen - 10

19 -10

20 cm

-3Die Konzentration an Verunreinigungsatomen in sehr stark dotierten Bereichen beträgt 10

21 cm

-3 . In diesem Fall spricht man bereits von einem

entarteten Halbleiter , da eine solche Konzentration (ein Verunreinigungsatom pro 10 oder weniger Siliziumatome) die Energiestruktur des Kristalls verändert.

Temperaturabhängigkeiten der Siliziumeigenschaften

Vom ersten Teil an erinnern wir uns, dass reines Silizium bei Raumtemperatur ein Dielektrikum ist. Ein Elektron-Loch-Paar entsteht nur in einem von einer Billion Fällen, aber dieser Anteil steigt mit zunehmender Temperatur exponentiell an. Es gibt so etwas - die Temperatur der Verdoppelung der Konzentration eigener Ladungsträger. Für Silizium sind es ungefähr 9 Grad.

Das heißt, Erhöhen Sie die Temperatur um 9 Grad, der Prozentsatz der zerfallenden Siliziumatome steigt um das Zweifache. 18 Grad - 4 mal; 27 Grad - 8 mal; 36 Grad - 16 mal; 45 - 32 mal; 90 - 1024 mal; 180 - 10

6 mal; 270 - 10

9 mal.

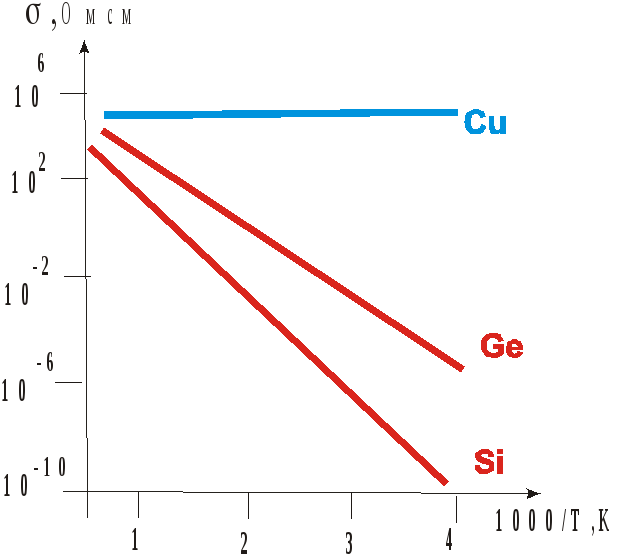

Vergleich der Wärmeleitfähigkeit von Kupfer, Silizium und Germanium. Quelle

Vergleich der Wärmeleitfähigkeit von Kupfer, Silizium und Germanium. QuelleWir erhalten, dass bei Erwärmung auf 200 Grad (~ 2,1 in der obigen Grafik) die intrinsische Konzentration von Elektron-Loch-Paaren 10

16 beträgt, was der Verunreinigungskonzentration von leicht dotierten Schichten entspricht. Bei 300 Grad (~ 1,75) bereits 10

19 ist dies die Konzentration stark dotierter Schichten (n + und p +). Bei dieser Temperatur verwandelt sich Silizium tatsächlich in einen Leiter und Transistoren verlieren die Steuerbarkeit.

Probleme werden viel früher beginnen. Die Temperatur im Chip ist ungleichmäßig. Es gibt lokale Heizzonen, normalerweise in der Mitte des Chips. Wenn die Temperatur in einem kleinen Bereich 200 Grad überschreitet, beginnt aufgrund einer Erhöhung der intrinsischen Leitfähigkeit von Silizium der Leckstrom zu steigen. Dies führt zu einer noch stärkeren Erwärmung, wodurch der Leckstrom weiter erhöht und der Bereich der Überhitzung erweitert wird. Der Prozess wird irreversibel und ... boomt. Und unwiderruflich. Daher ist bei allen großen Mikrokreisen ein automatischer Überhitzungsschutz eingestellt.

Deshalb ist es so wichtig, keine starke Erwärmung des Kristalls zuzulassen.

Zum Vergleich ist die Konzentration von intrinsischen Elektronen und Löchern in Galliumnitrid bei Raumtemperatur um mehrere Größenordnungen niedriger, und die Temperatur zur Verdoppelung der Anzahl von intrinsischen Ladungsträgern beträgt etwa 25 Grad. Die oben in Galliumnitrid beschriebenen Probleme beginnen bei etwa 600-700 Grad.

Tunnelstrom

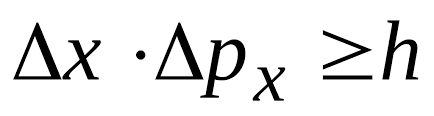

Dieses Phänomen ist gleichzeitig komplex und einfach. Die Wurzeln liegen in der Quantennatur des Elektrons. Ein Elektron lebt nach den Gesetzen der Quantenmechanik, die aus Sicht der klassischen Physik nicht immer verstanden werden. Nach diesen Gesetzen ist ein Elektron nicht nur ein Teilchen, sondern auch eine Welle, und sein Verhalten kann nur mit einer gewissen Wahrscheinlichkeit berechnet werden. Es gibt eine solche Heisenberg-Formel:

Es wird auch als

Heisenberg-Unsicherheitsrelation bezeichnet . Aus der Formel folgt, dass die räumlichen Parameter des Elektrons nicht mit einer Genauigkeit bestimmt werden können, die größer als ein bestimmter Wert (Plancksche Konstante) ist. In extremen Fällen der Gleichung wissen wir nichts über seine Geschwindigkeit und Bewegungsrichtung, wenn wir den genauen Ort des Elektrons kennen. Wenn Sie die Geschwindigkeit und Richtung genau kennen, ist nichts über seinen Aufenthaltsort bekannt. Es stellt sich heraus, dass das Elektron ein solches Teilchen ist, das im Raum mit Spitzen der Seinswahrscheinlichkeit verschwommen ist. Zu jedem Zeitpunkt kann sich ein Elektron ohne äußeren Einfluss überall im Universum befinden. Zwar ist die Wahrscheinlichkeit seines Auftretens sehr weit vom aktuellen Standort entfernt gering.

Stellen Sie sich nun die Struktur des Metall-Dielektrikum-Halbleiter-n-Typs (MIS) vor. In einem Metall ist die Konzentration an freien Elektronen ungefähr gleich der Konzentration an Atomen (10

22 / cm

3 ). Sie können nicht in ein Dielektrikum eindringen, da dies für Elektronen aus einem Metall ein Bereich verbotener Energien ist. Innerhalb des Dielektrikums beginnt eine Elektronenwelle mit Energie wie in einem Metall zu interferieren (sich selbst zu zerstören). Sie können sich jedoch in einem n-Halbleiter materialisieren, in dem für sie eine Zone zulässiger Energien vorhanden ist. Elektronen gelangen von einem Metall zu einem Halbleiter durch eine Oxidschicht ohne äußeren Einfluss, einfach aufgrund ihrer Wahrscheinlichkeit. Dies ist der

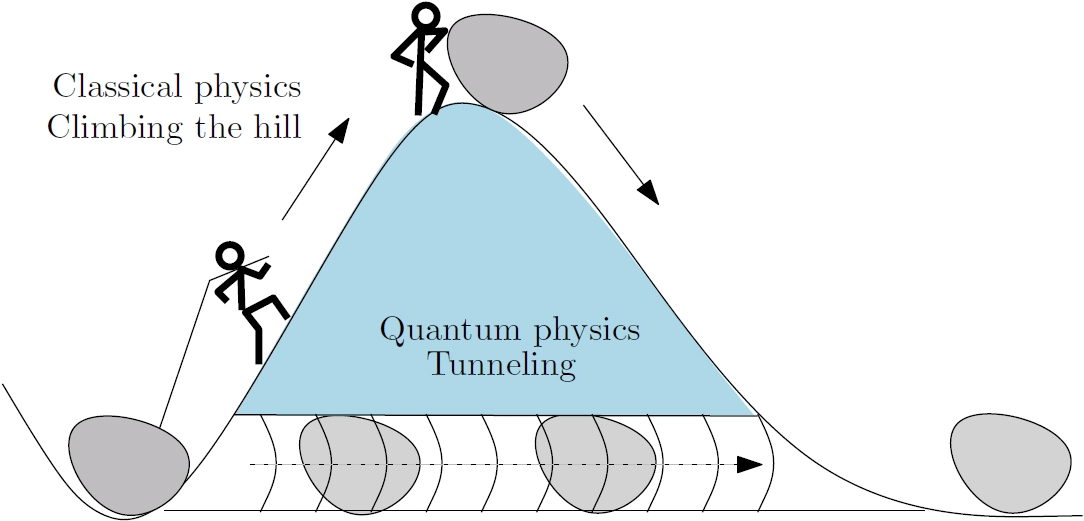

Tunnelstrom . Der Prozess selbst wird Tunneling oder Quantentunneln genannt (klingt cooler!).

Die zusätzliche Energie, die dem Elektron für das „klassische“ Eindringen in das Oxid hinzugefügt werden müsste, wird als Potentialbarriere bezeichnet. Schematisch nagt ein Elektron durch einen Tunnel durch eine Potentialbarriere.

Es gibt eine Strömung in die entgegengesetzte Richtung - von einem Halbleiter zu einem Metall. Da jedoch die Konzentration der freien Elektronen im Halbleiter um mehrere Größenordnungen niedriger ist, ist der Rückfluss proportional geringer.

Ein p-Halbleiter für Elektronen aus einem Metall ist auch ein Band verbotener Energien. Hier ist jedoch der umgekehrte Prozess möglich - das Tunneln von Valenzelektronen von einem Halbleiter zu einem Metall mit dem Auftreten von Löchern in Silizium. Es sieht so aus, als würden Löcher aus Metall tunneln. Die Intensität ist bei sonst gleichen Bedingungen etwa zehnmal geringer als beim Tunneln freier Elektronen.

Der Tunnelstrom für Entfernungen über 1 μm kann vernachlässigt werden. Zu geringe Wahrscheinlichkeit und Übergänge zu selten. Mit abnehmender Entfernung steigt die Wahrscheinlichkeit spontaner Übergänge stark an. Bei Abständen von Einheiten von nm wächst der Tunnelstrom zehnmal, wenn er sich 0,2 nm nähert.

Ein ähnlicher Mechanismus funktioniert für npn-Siliziumschichten. Für ein freies Elektron aus der n-Region ist die p-Region ein Band verbotener Energien, es treten keine Übergänge auf. Wenn jedoch die Breite der p-Basis zu eng eingestellt ist, beginnen die Elektronen direkt von der Quelle zur Senke zu tunneln. Dies begrenzt die theoretische maximale Basisbreite auf 8 nm. Bei kleineren Größen wird der Source-Drain-Transistor aufgrund des Tunnelstroms im Prinzip unkontrollierbar.

Bei pnp-Strukturen ist die Situation ähnlich, aber Löcher (Valenzelektronen) tunneln.

In entarteten Halbleitern (stark dotiert) im Band verbotener Energien gibt es Inseln erlaubter Energien. Für sie ist die Möglichkeit des Tunnelns durch diese Inseln möglich. Wie man einen Bach überwindet, indem man auf klebende Felsbrocken springt.

Raumladungsregion (SCR)

Der Raumladungsbereich (SCR), es ist auch der Verarmungsbereich, es ist auch der Raumladungsbereich - es ist eine elektrisch geladene Schicht, die sich an der Grenze von n- und p-Bereichen bildet.

Verbinde geistig 2 Siliziumstücke, eines vom n-Typ, das andere vom p-Typ. In der n-Schicht gibt es viele freie Elektronen, in der p-Schicht gibt es viele Löcher, sie bewegen sich zufällig. Ein Teil der freien Elektronen geht in die p-Schicht, ein Teil der Löcher in die n-Schicht. Infolgedessen verbleiben nicht kompensierte positive Ionen in der n-Schicht und negative Ionen werden in der p-Schicht nicht kompensiert. Entlang der Grenze der Regionen tritt ein lokales elektrisches Feld auf, das weitere Übergänge zu behindern beginnt. Die Feldstärke ist an der Grenze maximal und nimmt mit der Entfernung allmählich ab. Am Ende wird die Feldstärke so, dass die Übertragung von Löchern und Elektronen aufhört und ein Gleichgewichtszustand hergestellt wird. Für Silizium beträgt die Spannung eines solchen internen Feldes etwa 0,5 Volt. Hängt von der Verunreinigungskonzentration auf beiden Seiten ab. Die Abhängigkeit ist schwach, etwa 0,1 Volt, wenn sich die Konzentration um das 10-fache ändert.

Zusätzlich zum Auftreten eines elektrischen Feldes an der Grenze nimmt die Konzentration an freien Elektronen und Löchern ab. Direkt an der Grenze der Schichten auf Null. Daher der zweite Name - "erschöpfte Region". Die Breite dieses Bereichs hängt von der Spannung am Übergang und der Konzentration der Verunreinigungen ab. Die Abhängigkeit von der Konzentration von Verunreinigungen ist umgekehrt quadratisch, d.h. Mit einer Erhöhung der Konzentration um den Faktor 100 nimmt die Breite des SCR um den Faktor 10 ab (tatsächlich etwas geringer, da die Spannung an der Verbindungsstelle zunimmt).

Dies ist ein Zustand, in dem keine externe Spannung an die Struktur angelegt wird.

Wenn Sie eine externe Spannung anlegen, wird diese mit der internen vektorisiert.

Wir legen eine kleine Durchlassspannung an die Verbindungsstelle an, d.h. plus (+) zur p-Schicht, minus (-) zur n-Schicht. Das externe und das interne Feld sind in verschiedene Richtungen gerichtet und beginnen sich gegenseitig zu kompensieren. Übergangsspannung und SCR-Breite werden reduziert. Wenn die Spannung des externen Feldes höher als die interne wird, verschwindet der SCR und der pn-Übergang öffnet sich vollständig. Für Halbleiterdioden gibt es sogar einen solchen Parameter - Schwellenspannung. Dies ist die Durchlassspannung, bei der die Diode vollständig öffnet.

Legen Sie nun die Sperrspannung an: minus (-) an die p-Schicht, plus (+) an die n-Schicht. Die externen und internen Felder addieren sich, die Spannung an der Verbindungsstelle und die Breite des SCR nehmen zu.

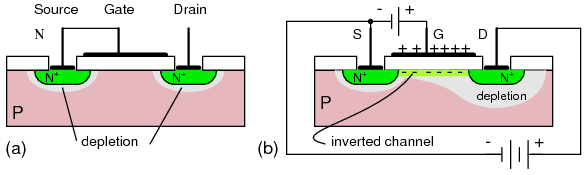

Wenn wir dieses Modell auf unseren Feldeffekttransistor übertragen, erhalten wir das folgende Bild:

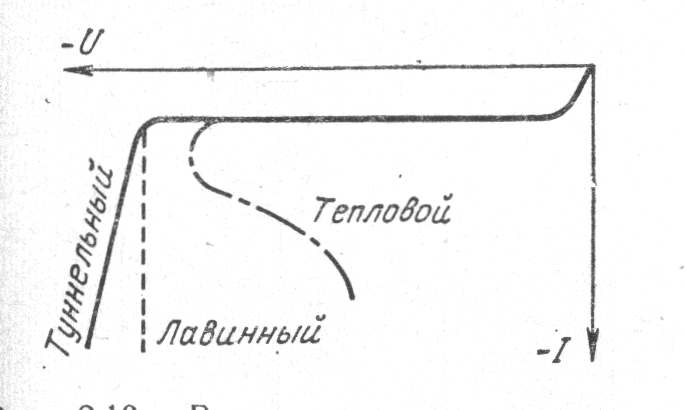

Hellrosa bezeichnet verarmte Bereiche (SCR). Wir erhalten, dass die reale Breite der

aktiven Basis , die durch die Gate-Spannung gesteuert wird, geringer ist als der Source-Drain-Abstand. Das heißt, die Größe der Basis abzüglich der Breite der SCR-Übergänge. In Abwesenheit einer Versorgungsspannung ist die Breite des SCR von Source und Drain gleich. Wenn Sie die Betriebsspannung anlegen, nimmt die Breite des SCR des Drains zu, da dieser unter Sperrvorspannung steht. Die aktive Basis verengt sich noch mehr:

Wenn die Basis zu kurz ist, werden der SCR von Drain und Source angeschlossen. Die Breite der aktiven Basis wird 0, ein Durchgangsstrom fließt vom Drain zur Source, der Transistor öffnet sich. Unabhängig von der Spannung am Verschluss. Der Transistor wird unkontrollierbar. Der Effekt wird als "Basispunktion" bezeichnet (

Hinweis: Wie F376 richtig bemerkt hat , handelt es sich höchstwahrscheinlich um "

Basispanne ").

Es gibt immer noch eine Zwischenoption, wenn der SCR nicht schließt, aber der Abstand von der Quelle zur Grenze des SCR des Abflusses weniger als 8 nm beträgt. Dann beginnen im SCR Elektronen von der Quelle zu tunneln. Sobald sie im SCR sind, werden sie durch ein elektrisches Feld in den Abfluss geworfen. Einfach ausgedrückt fließt ein anständiger Tunnelstrom von Source zu Drain.

Lawinenzusammenbruch

Wenn das elektrische Feld im SCR zu hoch wird, beschleunigt ein Elektron, das versehentlich hineinfliegt, so stark, dass es das Elektron aus einem neutralen Atom entfernt. 2 Elektronen erscheinen, sie beschleunigen wieder und entfernen die Elektronen von den folgenden usw. Der Prozess ähnelt einer Lawine, daher der Name. Im SCR erscheint ein leitender Kanal, durch den Strom fließt. Der Transistor öffnet spontan.

Eine ähnliche Situation kann im Gate-Dielektrikum auftreten. Wenn die Feldstärke über der Schwelle liegt, beschleunigt ein aus dem Metall herausfliegendes „schnelles“ Elektron und verursacht eine Lawine.

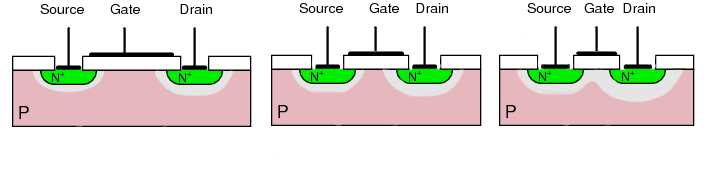

Ein klarer Vergleich verschiedener Arten von Pannen. Quelle

Ein klarer Vergleich verschiedener Arten von Pannen. QuelleUm einen solchen Lawinenzusammenbruch zu vermeiden, ist es notwendig, übermäßige Feldstärken über dem Durchschlagwert zu vermeiden. Feldstärke = Spannungen / Länge. Das heißt, Es ist notwendig, die Spannung zu reduzieren und die Breite des SCR (oder die Dicke des Dielektrikums) zu erhöhen.

Elektrische Widerstandsbereiche

Dies ist bereits eine klassische Elektrotechnik. Und der Drain, die Source, der Kanal und sogar die leitenden Metallschienen haben ihren eigenen elektrischen Widerstand. Der Widerstand ist höher, je größer die Länge des Diagramms und desto kleiner die Querschnittsfläche.

Angenommen, wir haben alle Elemente des Transistors proportional um das Zweifache reduziert. Durch Verringern der Länge wird der Widerstand des Abschnitts

um das Zweifache

verringert , und durch Verringern der Breite und Höhe

wird das Vierfache erhöht . Insgesamt ergibt dies eine zweifache

Erhöhung des Widerstands des Elements . Beim Durchgang des Stroms verursacht der Widerstand einen Spannungsabfall. Für Transistorspannungen im Bereich von 1 V und darunter ist sogar ein kleiner Spannungsabfall kritisch.

Für die Metallisierung wurde diese Frage einfach gelöst - die erste schmale Metallschicht verbindet nur die Elemente innerhalb der Zelle. Alles andere wird auf die oberen Metallisierungsstufen gebracht: Dort wird die Oxidschicht dicker und die Spuren breiter. Trotzdem kann die Größe von Kontaktfenstern und Metallisierungsspuren nicht unendlich reduziert werden.

Für Bereiche aus Silizium wurde eine Erhöhung des Widerstands durch eine Erhöhung der Konzentration von Verunreinigungen kompensiert. Zumindest bis vor kurzem, bis sich die Auswirkungen von Tunnelbau und Ausfall bemerkbar machten.

Ein anderer Weg war die Technologie von "gestrecktem Silizium" oder "gespanntem Silizium". Seine Essenz besteht darin, dass eine Germaniumschicht auf einem Siliziumsubstrat abgeschieden wird. Germanium ist ein Element der gleichen Gruppe wie Silizium, ähnlich in der Kristallstruktur. Germaniumatome sind jedoch größer, der Abstand zwischen ihnen im Kristallgitter ist größer. Dann wird über Germanium ein dünner epitaktischer Siliziumfilm gebildet. Silizium im Film beginnt, die Kristallstruktur von Germanium zu wiederholen. Der Schritt des Kristallgitters ist sowohl in Germanium als auch größer als in gewöhnlichem Silizium. Es stellt sich heraus, dass Silizium sozusagen in alle Richtungen gedehnt wird. Daher der Name. Dies erhöht die Beweglichkeit von Elektronen und Löchern.

Die kombinierte Wirkung physikalischer Effekte

Betrachten Sie nun die Auswirkungen dieser Effekte zusammen.

Die Hauptbedrohung bei der Miniaturisierung von Transistoren ist eine Punktionsbasis. Um es zu entfernen, müssen Sie die Breite des SCR reduzieren. Es kann reduziert werden, indem äußere Spannungen reduziert und die Konzentration von Verunreinigungen in der Basis erhöht werden.

Die Versorgungsspannung kann nirgends reduziert werden, sie liegt bereits im Bereich von 1V - etwa zwei Schwellenwerten. Wenn wir noch weniger tun, besteht die Gefahr, dass die Transistoren aufgrund des elektrischen Widerstands „verschwommen“ geöffnet werden.

Sie können die Konzentration von Verunreinigungen in der Datenbank erhöhen, aber dann erhalten wir:

- ein starker Anstieg des Tunnelleckstroms vom Drain zur Basis;

- erhöhtes Risiko eines Lawinenzusammenbruchs des Übergangs;

- Erhöhen der Spannungsschwelle zum Induzieren des Kanals mit der Gefahr eines Durchbruchs des Gate-Dielektrikums.

Aufgrund dieser Einschränkungen ist die

Konzentration an Verunreinigungen in der Base auf 10 18 -10 19 festgelegt .

All diese und unbenannte Faktoren beschränken die

minimale Basisbreite für Silizium-MOS-Transistoren im Bereich von 25 nm . Es ist weniger möglich, aber der Leckstrom wird unzureichend und die Ausfallwahrscheinlichkeit steigt exponentiell an.

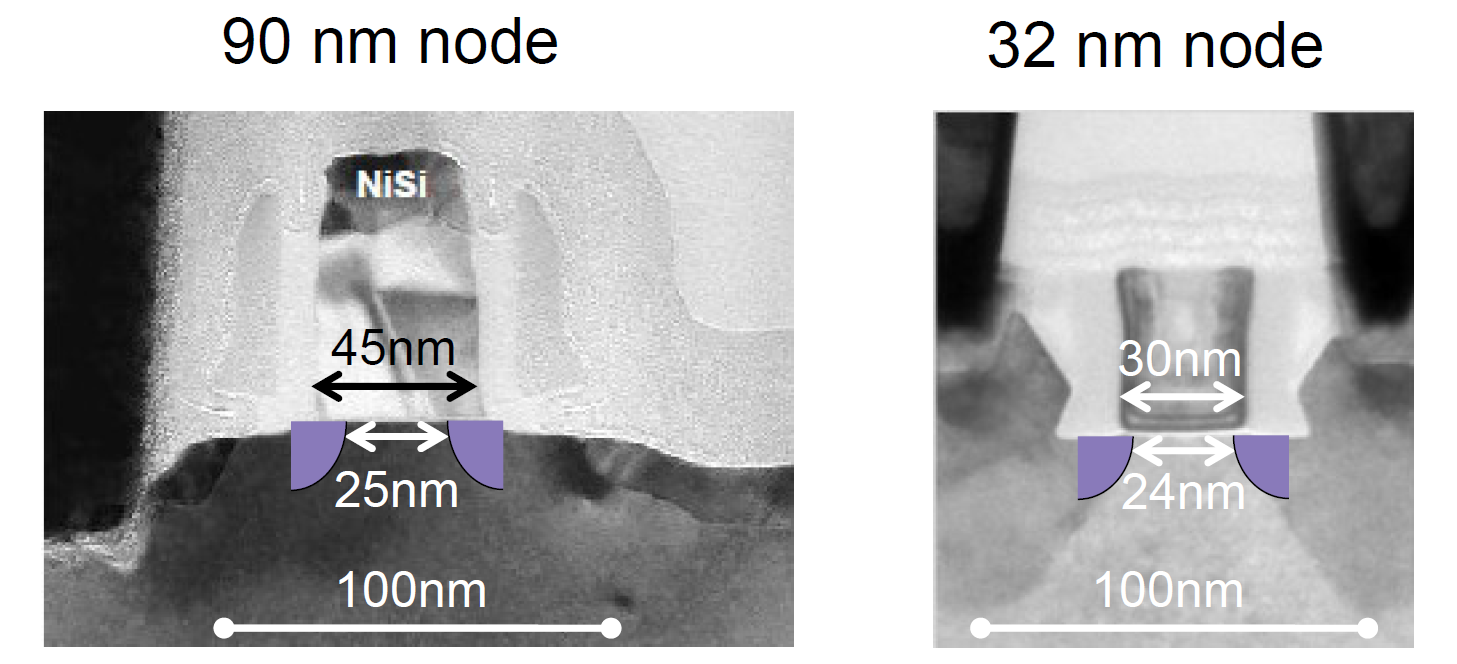

Mikroskopische Aufnahme von Transistoren mit 90-nm- und 32-nm-Prozesstechnologie. Zoom und Skalierung sind identisch. Quelle

Mikroskopische Aufnahme von Transistoren mit 90-nm- und 32-nm-Prozesstechnologie. Zoom und Skalierung sind identisch. QuelleWie wir sehen können, ist die Größe der Metallkontakte viel kleiner geworden, aber die Breite der Basis hat sich nicht geändert. Trotzdem 25 nm. Darüber hinaus ist es für Transistoren, die die Technologie von 14 nm, 10 nm und 7 nm verwenden, dasselbe (

ooops! ).

Dies wurde erstmals beim Übergang von 130 nm zur ersten 90-nm-Reihe festgestellt. Dann konnten sie zum ersten Mal die Breite der Basis nicht proportional zu allen anderen Größen reduzieren, sie blieb ungefähr 35 nm. Später wurde es noch auf 25 nm reduziert, aber seitdem unterliegt die Breite der Basis nicht mehr den Proportionen der Technologie. Und je kleiner die Transistoren wurden, desto mehr manifestierte sich dies.

Die Kriterien der technischen Prozesse mussten geändert werden. Was hast du getan Die meisten haben nichts getan. Sie erteilten weiterhin die Erlaubnis zur Fotolithografie als Norm des technologischen Prozesses. Oder die minimale Breite des Metallisierungspfads als Manifestation der einfachsten und intuitivsten Operation. Und dann gehen wir weiter zum Marketing ...

Die kreativsten Vermarkter kamen von Intel. Sie begannen, die technische Prozessrate aus der Größe der Elemente zu berechnen, beispielsweise basierend auf der Fläche der Sechs-Transistor-Zelle des statischen Speichers. In der Technologie mit einer Auflösung von 65 nm Lithographie betrug sie 0,77 & mgr; m

2 und bei einer Auflösung von 40 nm wurde sie 0,37 & mgr; m

2 . Wenn die Transistorgrößen wie zuvor proportional reduziert wurden, entspricht dies der Technologie von 45 nm. Wir gehen also davon aus, dass wir eine 45-nm-Technologie haben. Hierher kamen die Diskrepanzen zwischen der Intel-Technologie und anderen - 28 nm für alle, 32 nm für Intel; 20 nm für alle, 22 nm für Intel; 10 nm für alle, 14 nm für Intel.

Wie die nachfolgende Geschichte zeigte, war Intel ehrlicher als seine Konkurrenten.

Auswirkung von Leckströmen

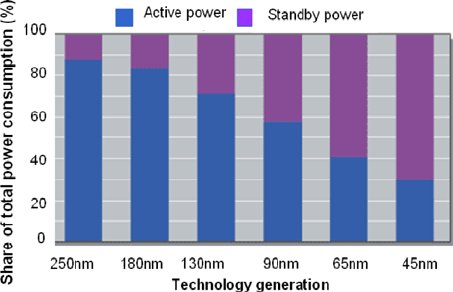

Es gibt einen wunderbaren Zeitplan aus einem Artikel bereits im Jahr 2010:

Quelle

QuelleDie Grafik zeigt den Prozentsatz des Arbeits- und Störenergieverbrauchs. Blau - Energiefreisetzung durch Aufladeströme (Betriebsstrom), lila - Ergebnis von Leckströmen (Streustrom). Dies berücksichtigt die Maßnahmen, die zur Reduzierung von Streuströmen ergriffen wurden.

Der Grund, warum das Wachstum der Prozessortaktraten gestoppt wurde, ist deutlich sichtbar. Die ersten Prozessoren mit 3 GHz (z. B.

Pentium 4 ) wurden Anfang der 2000er Jahre eingeführt. Also auf diesem Niveau und blieb. Normalerweise erklärt sich dies aus der Tatsache, dass die Anzahl der Kerne zugenommen hat, die Logik komplizierter geworden ist, das Pipelining vertieft wurde und die Anforderungen an Stabilität und allgemein an Glück bei Gigahertz gestiegen sind. Teilweise wahr.

Aber! - .

, . , 2 , 4 , 6-7 . , , -. . , .

.

180 130 . , , .

. - , , . , 45 .

, 2000- .

, — .High-k . , NiSi. - .

High-k. . , . , , . – – .

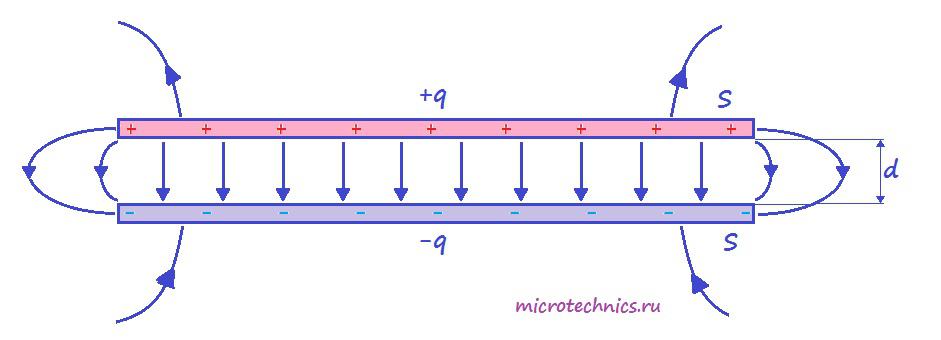

— . . , . . . :

S – ,

d – ,

ԑ – , 1, 1,

ԑ

0 – .

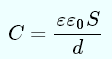

, . , . 1,2 (

sic! ). 6

(!!!) . . 5 , .. 1 , 10 (

!!! ) ( 10 0,2 ). .

– . — High-k . HfO

2 Ta

2 O

5 . 3.9, High-k 25-30. , , - .

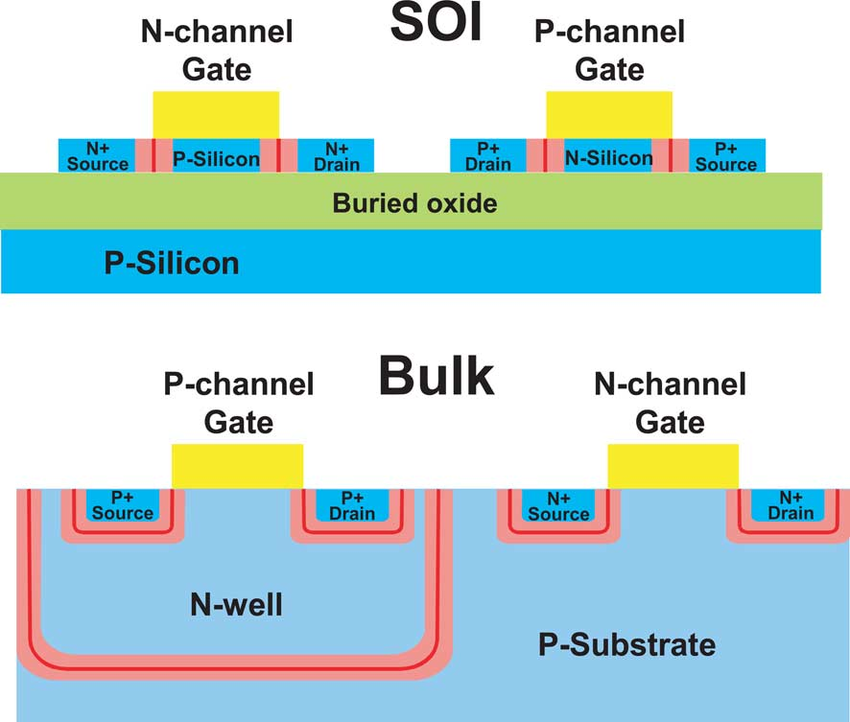

(SOI)

, , SOI, . : , (

UPD: , ,

SIMOX Smart Cut ).

SOI-

SOI-.

. . , - , . . . , .

Al

2 O

3 , . , . High-k 15 . .

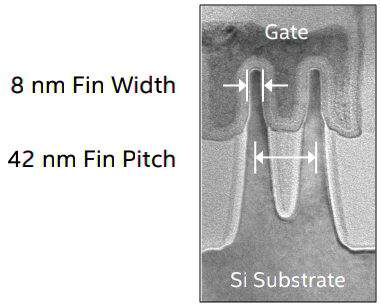

FinFET

Fin – , . 22 . , , .

UPD: FinFET

a5b , «».

, .

, .  — .

— . . , () , . , , , . , .

- () . , .

Quelle

Quelle

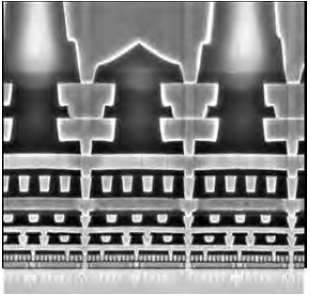

. 6 , 3 n-, 3 p- ( Fin ), (Gate), . , , ( 25 ), . . , 22 54 , 14 – 42 , 10 – 34 . .

3 , . Intel, Samsung TSMC. AMD – GlobalFoundries – . AMD TSMC Samsung.

, . , --. . , . . . , – , . , .

?! , . FinFET . High-k , , . . . Das heißt, .

Das heißt, . , 7 22 . FinFET 22 , 7 3 , . , , 10 7 1,8 . …

Was kommt als nächstes? . , Samsung GAAFET 5 .

CMOS, FinFET GAAFET .

CMOS, FinFET GAAFET . Das heißt, , . : ? — .

UPD: F376 , FinFet . Gate-All-Around FET , .

, . FinFET SOI. , , .

.

Die drei führenden Unternehmen stachen heraus - Intel, Samsung und TSMC. Intel produziert unter eigenen Marken, der Rest ist hauptsächlich auf Bestellung. Unter den Marken AMD, NVIDIA, Qualcomm, Apple und IBM verstecken Chips, die in den Werken von TSMC oder Samsung hergestellt werden. Einige alte Führer fielen ab oder stießen auf eine Barriere. Die Chinesen versuchen, in die große Liga einzusteigen, aber bisher nicht sehr erfolgreich: Ihnen fehlt ihre eigene technologische Basis, und die weltweit führenden Hersteller von Geräten halten die neuesten technologischen Linien für die Chinesen aufrecht.

Der Optimismus der Experten ist mit dem Übergang zu Massenstrukturen und dem Beginn des Einsatzes der EUV-Lithographie verbunden. Samsung und TSMC haben begonnen, es in begrenztem Umfang für die empfindlichsten Strukturen zu verwenden. Dies gibt ihnen die Möglichkeit, über das Erreichen von Standards von 7 nm und in Zukunft bis zu 5 nm zu berichten. Obwohl diese Zahlen, wie bereits beschrieben, tatsächlich wenig Wirkung haben. Derselbe Intel gab EUV im Allgemeinen auf. Anscheinend glauben sie nicht, dass dies die Leistung erheblich verbessern wird.

Auf der anderen Seite verstehen die Fachleute, dass die Moore-Ära vorbei ist und jeder neue Schritt im Produktivitätswachstum mehr Aufwand und Zeit erfordert. Das schnelle Wachstum der Mikroelektronik endet (

schluchzen! ). Wie ist das einmal in der Automobilindustrie und in der Luftfahrt passiert? Nach einem explosiven Wachstum folgt eine langsame Entwicklung.

Von den vielversprechenden Durchbruchspunkten kann man den Übergang zu einem anderen Material (nicht Silizium) und die Schaffung mehrschichtiger Mikroschaltungen herausgreifen (3D-Integration - Grüße an AMDs Ideen). Für die 3D-Integration müssen Sie die Wärmeerzeugung drastisch reduzieren oder die Wärmeableitung verbessern.

Das ist alles für Transistorgrößen. In einem anderen gibt es andere Reserven für Produktivitätswachstum. Zum Beispiel bei der Optimierung der Architektur. Sie können sogar einen Marketing-Schritt machen und sagen, dass ein neuer Prozessor mit verbesserter Architektur so funktioniert, als wäre er ein alter mit 0,5-nm-Technologie. Daher markieren wir es als 0,5 nm. Und stellt mit ihm fest, dass die Abmessungen der Transistoren gleich sind.

Es ist möglich, neue Zelltypen aus Kombinationen von Transistoren zu erstellen. Stellen Sie beispielsweise anstelle von 6 Transistorspeicherzellen 2 Transistorstrukturen mit komplexer Physik her, die sich gegenseitig beeinflussen. Volumenstrukturen bieten hier viele Möglichkeiten.

Physikalische Grenzen

Jemand könnte sagen, dass der Pessimismus des Autors nicht gerechtfertigt ist. Sie finden Wege, um die Einschränkungen zu umgehen. Vielleicht nicht so schnell wie vorher, aber trotzdem.

Tatsache ist, dass es immer noch physikalische Prozesse gibt, die nicht umgangen werden können. Die wichtigsten sind Materie, die aus Atomen besteht, und die Ladungsträger sind Elektronen. Einen Transistor zu erzeugen, der kleiner als ein Atom ist, funktioniert nicht. Es wird nicht funktionieren, auch nur weniger als 1000 Atome zu erzeugen. Weil es eine Elektronen- und Heisenbergsche Unsicherheitsrelation gibt. Ein Elektron ist ein sehr instabiles Teilchen, ein mehr oder weniger stabiles Verhalten ist nur für eine Anordnung von Tausenden und Millionen von Elektronen möglich. Mit einem Elektron kann man nur die Schrödinger-Katze zerstören.

Hinweis: Obwohl es Entwicklungen bei Einzelelektronentransistoren gibt (

1 ,

2 und

3 )

Selbst bei aktuellen Größen treten Kollisionen aufgrund des spontanen Betriebs von Transistoren auf. Wenn die Wahrscheinlichkeit einer Kollision 10 bis

9 (eins zu einer Milliarde) beträgt, ergibt sich bei der Anzahl der Elemente in Milliarden und Frequenzen in GHz durchschnittlich 1 Kollision pro Zyklus oder mehrere Milliarden Kollisionen pro Sekunde. Um diese zu erfassen, gibt es Systeme zur Überwachung der Integrität von Vorgängen, und ein verdächtiger Vorgang wird zur erneuten Ausführung gesendet.

Mit der Miniaturisierung nimmt die Anzahl der Kollisionen sehr stark zu. Infolgedessen kommen wir durch die Miniaturisierung zu einer Situation von Null oder sogar einem negativen Effekt. Das heißt, Transistoren, die weniger hergestellt wurden, passen mehr in den Kristall, aber aufgrund des Wachstums von Kollisionen und Wiederaufbereitungszyklen stieg die Gesamtproduktivität nicht an. Oder vielleicht sogar gefallen. Und diese Schwelle ist ziemlich am Horizont.

Ein paar Worte zur heimischen digitalen Mikroelektronik

Entgegen der landläufigen Meinung war die Verzögerung der UdSSR durch die Führer bis 1985 nicht so groß. Über 3-4 Jahre. Dies ist der

Fall, wenn wir die

führenden Unternehmen in Zelenograd übernehmen (Anmerkung:

BarsMonster schrieb damals über Micron). Nach Moores Gesetz beeinträchtigte sogar eine Verzögerung von 3-4 Jahren die Leistung erheblich. Es gab Probleme beim Erhalten von hochwertigem Oxid mit der Klarheit von pn-Übergängen. Wenn wir eine konservative Politik in Bezug auf die Verpackung von Chips in dem Fall hinzufügen (lange Kontaktlinien haben die Produktivität der Geräte nicht erhöht) sowie die sowjetischen Standards für die Herstellung von Platten und Gehäusen mit einem Bündel Eisen (diejenigen, die sowjetische Tonbandgeräte zerlegen, werden es verstehen), bekommen wir einen Witz über den sowjetischen Chip mit Gusseisen Griffe zum Tragen.

Es gibt viele Gründe für den Rückstand. Später Startanuli, begrenzte Ressourcen, Sprühressourcen. Als sich die Amerikaner auf CMOS konzentrierten, experimentierten unsere weiter mit verschiedenen Technologien. Sie arbeiteten ziemlich aktiv mit Siliziumalternativen, hauptsächlich mit A

3 B

5 -Materialien. Nun, die allgemeine Entspannung der späten sowjetischen Forschungsinstitute.

Nach 1985 begannen die Amerikaner abrupt und wir hatten Probleme. Dann in den 1990er Jahren, als das Leben in der Branche durch Trägheit warm war. Infolgedessen betraten sie das 21. Jahrhundert mit 800-nm-Technologie, als die Führer bereits 130 nm gestürmt hatten. Das zweite Leben der Branche wurde durch Massenchipisierung von Karten und Regierungsaufträgen gegeben. Die Hauptproduktion von Stahl: Chips für SIM-Karten, Bankkarten, Zahlungskarten, Transport- und Rabattkarten und andere Konsumgüter. Große Gigahertz und kleine Nanometer werden dort nicht benötigt.

Hinweis: Während es in Moskau Zeitkarten gibt (gekauft, gebraucht, weggeworfen, mit einer Fabrik beladen), fördern sie im selben China aktiv ressourcenschonende Technologien, insbesondere die wiederverwendbare Verwendung des "Tokens" in der U-Bahn (auch für eine kurze Fahrt). .

Video über die U-Bahn von Shenzhen

Trotzdem wird versucht, in die „große Liga“ der Mikroelektronik einzusteigen. Die Entwicklung erfolgt in vier Hauptrichtungen.

- "Souveräne" technische Prozesse. Ein Versuch, einen vollständigen Produktionszyklus für Haushaltsgeräte und unsere eigenen technologischen Prozesse zu schaffen. Wir folgen dem gleichen Weg, den Führungskräfte vor 20 Jahren eingeschlagen haben, berücksichtigen jedoch den gefundenen Rechen und die Lösungen. Von den letzteren waren in offenen Quellen 250 nm in der Reihe und 150 nm im Implementierungsprozess. Dies beinhaltet auch den Versuch, eigene EUV-Lithografieanlagen bei 13,5 nm zu erstellen und somit sofort zu beenden, wenn nicht in den großen Ligen, dann in deren Nähe.

- Kauf von technologischen Linien von führenden Herstellern. Das Problem dabei ist, dass die modernsten Installationen auch in den besten Jahren nicht an uns verkauft wurden. Normalerweise verkaufen sie veraltete Linien, die eingestellt wurden. Nun, im Zusammenhang mit den Sanktionen, umso mehr. Hier können wir uns an das Epos erinnern, als Angstrom 2007 die Ausrüstung des AMD-Werks in Dresden im Rahmen des 180-nm-Herstellungsprozesses kaufte. Oder der Kauf einer 90-nm-Linie von Micron von der französischen STMicroelectronics, gefolgt von einem Upgrade auf 65 nm. Während dies der dünnste Herstellungsprozess in Russland ist, gelang es ihnen, vor den Sanktionen zu schnappen. Es stimmt, es gibt jetzt eine Problemumgehung - die Beschaffung über China.

- Auftragsproduktion in Fabriken in China oder Taiwan. Gleichzeitig sind Architektur und Topologie bei uns voll entwickelt,

jetzt stellen wir sogar unsere eigenen Fotomasken her . Die Chinesen können die technologischen Prozesse nur in ihren Fabriken reproduzieren. Wir erhalten fortschrittlichere produktive Prozessoren und entwickeln Kompetenz in der Entwicklung modernster Prozessorsysteme. Hier ist nicht eine Gruppe von Kulibin-Wissenschaftlern beteiligt, sondern große Designteams. Nur der letzte Abschnitt, die Produktion, wird aus dem gesamten Zyklus gestrichen.

Hinweis: Baikal wird im TSMC-Werk nur nach den Standards von 28 nm hergestellt. Ein Artikel über den Ausgang des Baikalsees und seine Analyse.

- Die Entwicklung alternativer Technologien. Dies ist die Entwicklung vielversprechender Technologien, die sich in Zukunft möglicherweise verbreiten werden. Dies schließt Arbeiten an A 3 B 5 -Verbindungen und -Heterostrukturen ein, hauptsächlich Galliumarsenid und -nitrid. Sowie Versuche, die Elektronenstrahl- und Röntgenlithographie für die Massenproduktion zu optimieren, wodurch im Allgemeinen die Einschränkungen der Lithographie beseitigt werden.

Hinweis: Wir haben vom verstorbenen Alferov eine starke Schule für Heterostrukturen geerbt, aber trotz staatlicher Unterstützung hat OptoGaN diese nicht gestreckt , da der Markt und die Marktbedingungen versagen.

Im Allgemeinen ist die Situation für die russische Mikroelektronik nicht brillant. Es besteht jedoch die Hoffnung, dass die Führer aufgrund körperlicher Einschränkungen unweigerlich langsamer werden, und hier schleichen wir uns langsam hinterher.

Der letzte Akkord über Erinnerung und Zeitfenster im dritten Teil in ein paar Tagen - bleiben Sie dran!

Vergessen Sie nicht, den

Blog zu abonnieren: Es ist nicht schwer für Sie - ich freue mich!

Und ja, bitte schreiben Sie über die Mängel, die im PM-Text vermerkt sind.