Heutzutage gibt es mehr als einen Speichertyp, von denen jeder für eine bestimmte Aufgabe verwendet wird. Sie kommen mit ihren Aufgaben recht gut zurecht, aber es gibt eine Reihe von Mängeln, die es nicht ermöglichen, eine dieser Speicheroptionen als universell zu bezeichnen. Wenn wir hier das Problem des kolossalen Datenwachstums auf der ganzen Welt und den Durst der Menschheit nach Energieeinsparung hinzufügen, dann ist es notwendig, etwas völlig Neues zu schaffen. Heute werden wir uns mit einer Studie treffen, in der Wissenschaftler einen neuen Speichertyp eingeführt haben, der die Vorteile von Flash- und DRAM-Speicher kombiniert. Welche „Extras“ hat diese Innovation, welche Technologien wurden verwendet, um sie zu erstellen, und welche Aussichten bestehen? Dies erfahren wir aus dem Bericht der Forschungsgruppe. Lass uns gehen.

Studienbasis

Es gibt viele Arten von Speicher, und alle wurden für eine bestimmte Aufgabe erstellt: SRAM (statischer Direktzugriffsspeicher) für den Cache, DRAM (dynamischer Direktzugriffsspeicher) für den aktiven Speicher, Flash-Speicher für die Datenspeicherung usw. Wie erwartet weist jedoch jeder der oben genannten Speichertypen seine eigenen persönlichen Mängel auf.

Zum Beispiel ein Flash-Speicher, bei dem es sich um eine Sammlung von MOS-Transistoren (Metalloxidhalbleiter) mit einem Floating Gate (FG) zum Speichern von Ladung handelt. Die Daten werden in einer solchen Ausführungsform als die Ladungsmenge dargestellt, die in der FG gehalten wird, die durch Oxidschichten isoliert ist.

Nach Ansicht von Wissenschaftlern besteht der Nachteil darin, dass zum Aufzeichnen und Löschen eine ausreichend hohe Spannung zur Steuerung durch einen Steuerverschluss (CG) erforderlich ist, üblicherweise etwa ± 20 V

2 . Dieser Prozess ist langsam und der durch einen Stromstoß verursachte Ausfallmechanismus führt zu einer Verkürzung der Lebensdauer des Geräts.

Trotz dieses Minus gibt es ein ziemlich beeindruckendes Plus - Daten werden durch Überprüfen der Kanalleitfähigkeit gelesen, was sehr wenig Spannung erfordert. Aus diesem Grund bleiben die Daten intakt, was als zerstörungsfreies Lesen bezeichnet wird.

DRAM wiederum ist viel schneller als Flash-Speicher, weshalb es sozusagen für aktive Computerprozesse verwendet wird. Der Nachteil des DRAM besteht darin, dass beim Lesen Daten aus den Zellen verloren gehen. Außerdem treten Ladungslecks von Kondensatoren auf, die zum Speichern von Daten verwendet werden.

SRAM ist auch ein ziemlich schneller Speichertyp und Daten gehen nicht so verloren wie im DRAM. In der Regel werden jedoch 6 Transistoren pro Zelle verwendet, dh Sie benötigen viel Fläche auf dem Chip.

Nachdem die Wissenschaftler die oben beschriebenen Mängel der klassischen Gedächtnistypen vorgestellt haben, betonen sie, wie wichtig es ist, eine alternative oder hybride Option zu finden, die frei von solchen Problemen ist und gleichzeitig alle Vorteile ihrer Vorgänger kombiniert.

In dieser Arbeit stellen die Forscher ihre Vision eines neuen Speichertyps vor - eines neuen ladungsbasierten, nichtflüchtigen Niederspannungs-Halbleiterspeichers in kompakter Form, der bei Raumtemperatur arbeitet. Die Forscher nannten ihre Nachkommen ein „universelles Gedächtnis“ (einfach, aber geschmackvoll).

Das Gerät ist ein Speicher mit einem Floating Gate, der auf der Basis von InAs / AlSb / GaSb-Heterostrukturen erstellt wurde, wobei InAs sowohl als Floating Gate als auch als Kanal ohne Übergänge verwendet wird.

Wissenschaftler haben Simulationen und tatsächliche Testergebnisse für einen Einzelzellenprototyp bereitgestellt.

Forschungsergebnisse

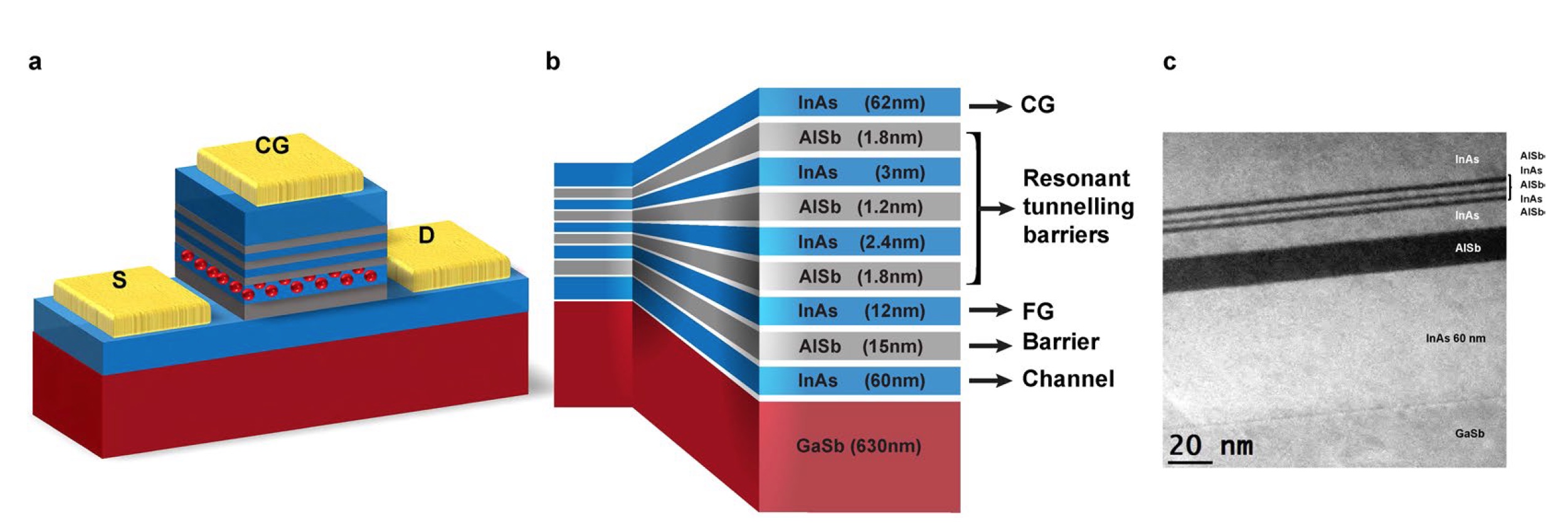

Bild Nr. 1

Bild Nr. 1Das obige Bild zeigt eine schematische Ansicht einer Vorrichtung und ein Bild eines PREM (Transmissionselektronenmikroskop).

Wie im Fall eines Flash-Speichers wird in diesem Gerät die Ladung in FG gespeichert, gleichzeitig gibt es jedoch keine Oxidbarrieren. Stattdessen wurde eine Verschiebung des Leitungsbandes in der sogenannten 6,1-Å-Halbleiterfamilie verwendet. Das heißt, die der Speicherzelle zugrunde liegende Vorrichtung ähnelt eher einem Transistor mit hoher Elektronenmobilität (HEMT) als einem MOS-Transistor. InAs bildet einen Kanal, der keine Übergänge enthält. N-Dotierung wurde jedoch verwendet, um unbeabsichtigte Hintergrunddotierungen zu kompensieren und Ga-Leerstellen im zugrunde liegenden GaSb zu halten. Beide Aufgaben bilden natürlich Schichten vom p-Typ.

Der pn-Übergang * ist die Kontaktfläche zweier Halbleiter mit unterschiedlichen Leitfähigkeitstypen - p (Loch) und n (elektronisch).

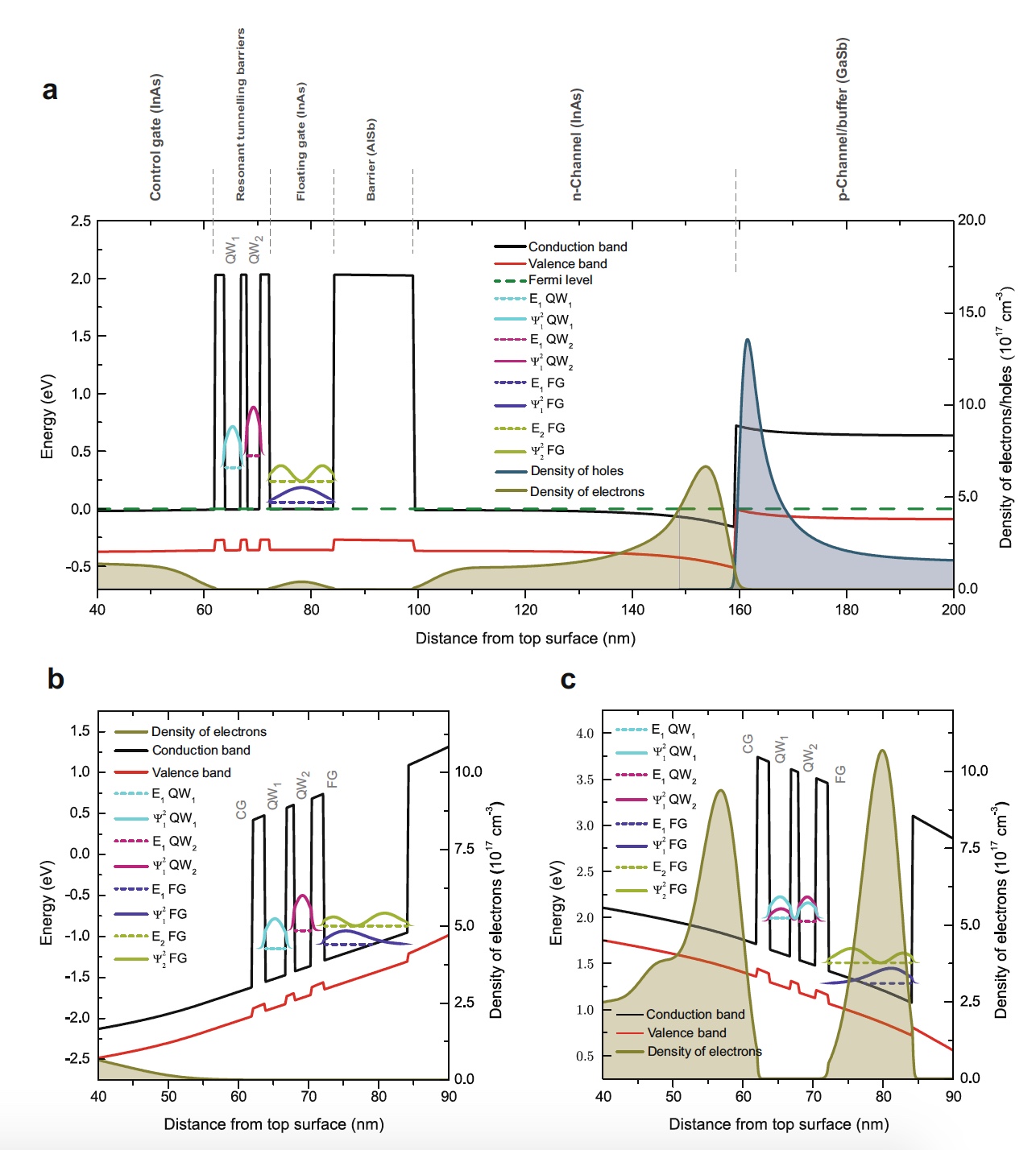

Bild Nr. 2

Bild Nr. 2Grafik

2a zeigt die simulierte Ausrichtung von Energiebändern sowie die Dichte von Elektronen und Löchern in den Schichten ohne Vorspannung. Die theoretischen Daten zeigen zusammen mit der Simulation, dass das InAs-Leitungsband an der InAs- und GaSb-Grenzfläche unterhalb des GaSb-Valenzbandes liegt. Dies führt zur Übertragung von Elektronen von der GaSb-Schicht auf die InAs-Schicht, wonach Löcher in GaSb verbleiben.

Das Loch * ist eine ungefüllte Valenzbindung, die sich als positive Ladung manifestiert, die der Ladung eines Elektrons entspricht.

Die akkumulierten Elektronen / Löcher sind an der Grenzfläche zwischen InAs und GaSb sichtbar, aber die Elektronen im InAs-Kanal sind nicht mit der InAs / GaSb-Grenzfläche verbunden, und ihre Dichte wird während des gesamten InAs beobachtet. Die Leitfähigkeit des gesamten Kanals wird von Elektronen in InAs dominiert, die eine höhere Mobilität und Dichte aufweisen als Löcher in GaSb.

Das interne FG der InAs-Schicht ist durch eine AlSb-Barriere (15 nm) vom InAs-Kanal isoliert. Gleichzeitig wirken doppelte

* InAs-

Quantentöpfe und drei AlSb-Barrieren als resonante Tunnelbarriere zwischen FG- und CG-InAs mit n-Dotierung.

Quantentopf * - begrenzt die Bewegung von Partikeln in der zweidimensionalen Dimension (anstelle der dreidimensionalen), wodurch sie sich nur in einer flachen Schicht bewegen können.

Daher werden in der untersuchten Vorrichtung die im FG der InAs-Schicht gespeicherten Elektronen durch eine anomal große Lücke im Leitungsband mit AlSb isoliert. Dies bedeutet, dass Sie ein Ladungsbegrenzungssystem erhalten können, das eine Lagerzeit bei Raumtemperatur von 1014 Jahren hat.

Der wichtigste Aspekt des Betriebs der untersuchten Vorrichtung ist die Tatsache, dass zwei Quantentöpfe (QW1 und QW2) in der Dreifachresonanztunnelbarriere unterschiedliche Dicken aufweisen, d. H. Es finden begrenzte Zustände mit unterschiedlichen Energien statt (

2a ). Da QW2 dünner als QW1 ist, hat das einzige verfügbare Energieniveau für Elektronen in QW2 eine höhere Energie als das Äquivalent in QW1. Zusätzlich hat der Zustand in QW1 eine signifikant höhere Energie als der Zustand in der benachbarten CG-Region. Dies verhindert ein direktes Elektronentunneln zwischen CG und FG, und die Elektronentransferbarriere von CG zu FG (oder umgekehrt) wird durch eine Verschiebung des InAs / AlSb-Leitungsbandes um 2,1 eV bestimmt, d. H. Die Ladung fließt nicht zu / von FG.

Der Grundzustand und der primäre angeregte Zustand im Floating Gate (FG) befinden sich weit unterhalb der Energiezustände in beiden QWs. Wenn daher keine Spannung angelegt wird, sind die Elektronen innerhalb des FG verriegelt, d.h. Die dreifach resonante Tunnelbarriere wird für Elektronen von / nach FG unüberwindbar. Somit wird eine Nichtflüchtigkeit erreicht.

Wenn eine unbedeutende Spannung an das Steuergatter (CG) angelegt wird, ist es möglich, die Kopplung der Energiezustände innerhalb der resonanten Tunnelbarriere einzustellen, wodurch die Elektronen frei von (

2b ) oder (

2c ) dem schwebenden Gate passieren können.

Während der Experimente wurden alle Lese-, Schreib- und Löschvorgänge in mehreren Zellen (Verschlussgröße 10 × 10 & mgr; m) in einer vor Elektrostatik bei Raumtemperatur geschützten dunklen Box durchgeführt. Alle Operationen, einschließlich Aufzeichnen und Löschen, wurden mit einem Versatz von ≤ 2,6 V durchgeführt, was ungefähr eine Größenordnung niedriger ist als für den vollständigen Betrieb mit einer Flash-Speicherzelle erforderlich, betonen die Forscher. Das Löschen wurde durchgeführt, indem das Steuergatter (V

E CG-S ) um +2,5 oder +2,6 V zwischen dem CG und der Quelle verschoben wurde, was zum Zustand "0" führte.

2b zeigt eine simulierte Ausrichtung von Energiebändern, die mit einer Löschspannung von +2,6 V erhalten wurden. Unter solchen Umständen ist das berechnete Elektronenenergieniveau in QW1 niedriger als das Niveau in QW2, während beide unter dem ersten angeregten Zustand liegen und nahe am Energieniveau liegen Grundzustand in FG. Das Ergebnis ist eine Löschung, d. H. Ein Elektronenfluss von FG nach CG, gefolgt von einer Verarmung von FG. Das gleiche Prinzip gilt für die Schreiboperation: V

W CG-S = -V

E CG-S , um die Ladung in FG zu erhöhen (Zustand "1").

Graph

2c ist eine simulierte Energiezone, wenn der Steuergatterversatz zum Schreiben von Daten verwendet wird: V

W CG-S = –2,6 V. In diesem Fall stimmen die Energieniveaus in QW1 und QW2 praktisch überein, was zu einer starken Kopplung dieser Zustände, resonantem Tunneln und Fluss führt Elektronen von CG nach FG.

Aufgrund der kapazitiven Kopplung hängt die Kanalleitfähigkeit von der im FG gespeicherten Ladungsmenge ab. Daher werden Daten durch Messen des Gate-Source-Stroms bei einer festen Gate-Source-Spannung gelesen.

Ladungserhöhung in FG, d.h. Zustand "1" reduziert die Ladung im Kanal, was zu einer Abnahme seiner Leitfähigkeit führt. Im Fall des Zustands "0" erfolgt der umgekehrte Vorgang. Daten können ohne Vorspannung auf CG gelesen werden, aber für die individuelle Auswahl von Geräten in einem Array von Zellen ist Spannung erforderlich. Zusätzlich sollte die Spannung ein elektrisches Feld durch die resonante Tunnelbarriere erzeugen, das es ermöglicht, die Ladung von / zu FG zu übertragen. Um diese Aufgaben zu erfüllen, sind nur ~ 2,5 V erforderlich.

Universelle Speicherfunktionen

Während praktischer Tests wurde das Lesen mit einem Nullpunktversatz von CG und V

SD = 1,0 V durchgeführt. Laut Wissenschaftlern war es jedoch möglich, für ein erfolgreiches Lesen weniger Spannung anzulegen.

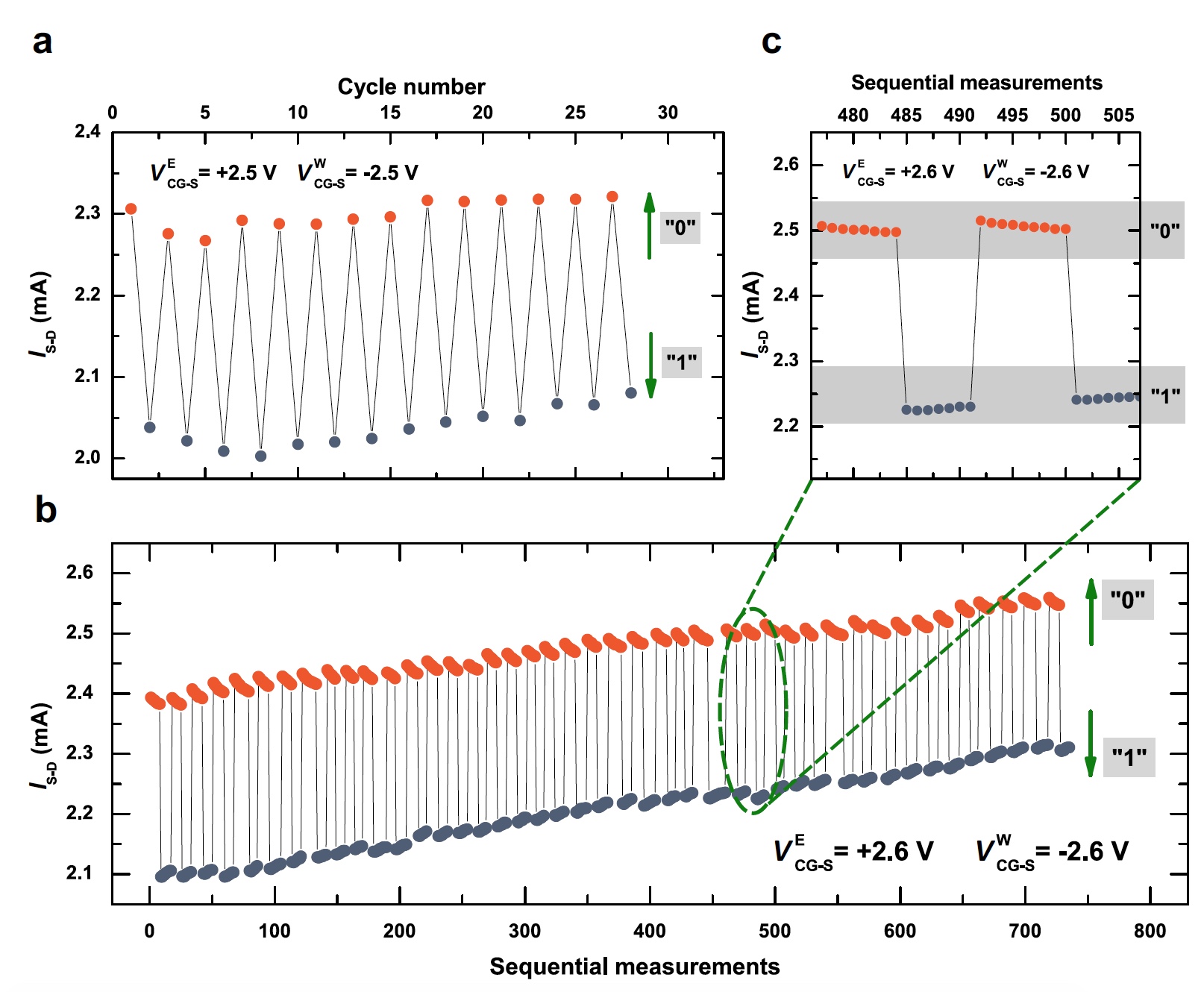

Bild Nr. 3

Bild Nr. 3Fig.

3a zeigt den Lösch-Lese-Schreib-Lese-Prozess. Das Hauptmerkmal der Sequenz ist die Leseoperation nach jedem Lösch- oder Schreibschritt.

Fig.

3b zeigt eine kompliziertere Sequenz, in der nach jeder Lösch- und Schreiboperation nicht eine Leseoperation, sondern mehrere vorhanden sind. Auf diese Weise zeigen die Forscher, dass die Leseoperation zerstörungsfrei ist.

Zwischen dem Zustand "0" und "1" gibt es einen deutlichen Unterschied in allen Sequenzen. Auf

3b gibt es jedoch Anzeichen einer symmetrischen Aufwärtsverschiebung in I

SD, wenn die Anzahl der Operationen zunimmt. Der Grund für dieses Verhalten ist zwar unklar, aber Wissenschaftler beabsichtigen, diesen Aspekt in weiteren Arbeiten zu untersuchen. Bei

3a wird dies jedoch nicht beobachtet, da die Spannung zum Löschen / Schreiben etwas niedriger ist.

Nach mehreren hundert Schreib- und Löschvorgängen sowie vielen Lesevorgängen während mehrerer praktischer Tests fanden die Wissenschaftler keine Anzeichen einer Beschädigung des Geräts.

Ein wichtiges Merkmal aller Speichertypen, die auf Ladungsspeicherung basieren, ist die Schaltenergie, die durch die Ladeenergie des Kondensators bestimmt wird.

Die Ähnlichkeit der Grundprinzipien der Flash-Speichertechnologie und des untersuchten universellen Speichers legt einen Vergleich dieser beiden Speichertypen nahe. Wenn wir davon ausgehen, dass die beiden Geräte dieser beiden Typen dieselbe Kapazität bei gleicher Verschlussgröße haben, ist die Schaltenergie des Universalspeichers 64-mal geringer als die des Flash-Speichers. Diese erstaunlichen Zahlen zeigen auch die Überlegenheit des universellen Speichers gegenüber dem DRAM.

Nach theoretischen Schätzungen liegt die CG-FG-Kapazität für eine Vorrichtung mit einer Größe von 10 × 10 & mgr; m in der Größenordnung von

10–12 F, und die Schaltenergie beträgt ungefähr 2 × 10

–12 J. Durch Verringern der physikalischen Größe der Vorrichtung wird die Schaltenergie für eine Vorrichtung der Größe 20 stark auf

10–17 J verringert nm, und dies ist 100-mal weniger als für DRAM und 1000-mal weniger als für Flash-Speicher. Und dies ist nach den kühnen Aussagen der Forscher ein sehr einzigartiges Merkmal.

Bild

3c zeigt einige Schreiblöschvorgänge aus

3b , bei denen die Unterschiede zwischen dem Zustand "0" und "1" sichtbar sind: Aufeinanderfolgende Lesemessungen nach dem Löschen ergeben eine geringfügig niedrigere I

SD für den Zustand "0". Die umgekehrte Situation wird bei sequentiellen Lesemessungen nach der Aufzeichnung beobachtet, oder vielmehr ist I

SD etwas größer.

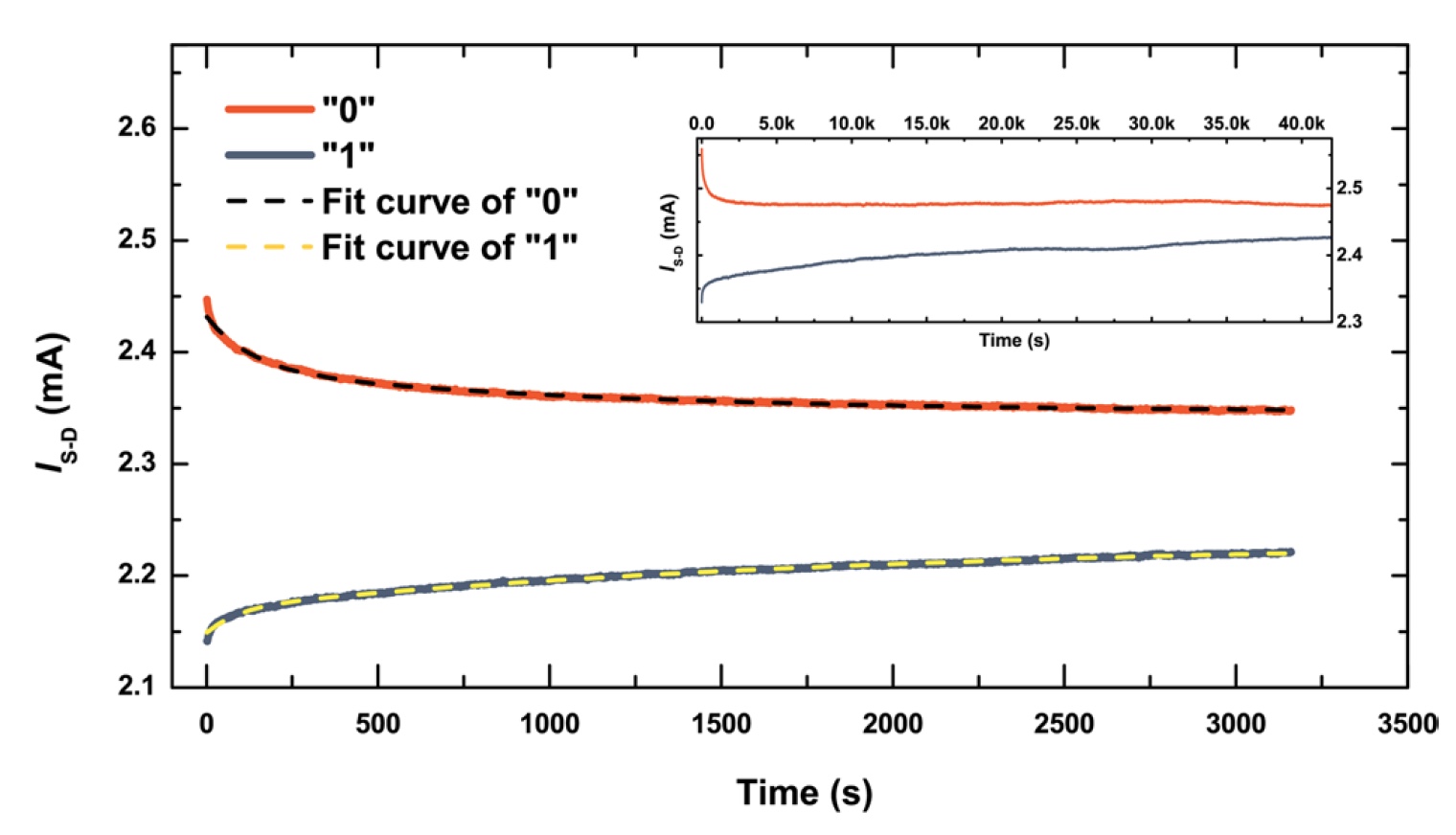

Wissenschaftler führen diesen Effekt auf die Variabilität (Volatilität) der Daten zurück. Um dies zu untersuchen, führten die Wissenschaftler für jeden Gedächtniszustand über einen langen Zeitraum eine Folge von Leseoperationen durch (Bild Nr. 4).

Bild Nr. 4

Bild Nr. 4Beide Zustände "0" und "1" zeigten einen anfänglichen schnellen Abfall, der mit dem übereinstimmt, was für

3s gesehen wird . Danach treten jedoch viel langsamere Änderungen auf, so dass während der gesamten Beobachtungszeit die entsprechenden Zustände „0“ und „1“ klar unterscheidbar sind.

Ein weiteres Experiment wurde ebenfalls durchgeführt (Einfügung in Bild Nr. 4), das die begrenzende Sättigung der exponentiellen Dämpfung und die zeitlich unterscheidbaren Zustände "0" und "1" zeigt.

Das Vorhandensein einer doppelten exponentiellen Dämpfung bedeutet, dass mehrere Mechanismen gleichzeitig der Verschlechterung von Zuständen zugrunde liegen. Unter den möglichen Optionen unterscheiden Wissenschaftler das Tunneln durch fehlerhafte Zustände in AlSb-Barrieren, die thermische Anregung von Elektronen durch die enge InAs-Bandlücke und die Rekombination mit thermisch erzeugten Löchern.

Die Auswertung der Kapazität der Vorrichtung und der angelegten Spannung zum Aufzeichnen / Löschen zeigt an, dass während des Schreib- und Löschvorgangs ungefähr 107 Elektronen vom / zum Floating Gate übertragen werden. Dies ist ziemlich viel, aber es wird praktisch kein negativer Einfluss beobachtet.

Für eine detailliertere Kenntnis der Nuancen der Studie empfehle ich Ihnen, den

Bericht der Forschungsgruppe zu lesen .

Nachwort

Den Wissenschaftlern gelang es nicht nur, einen neuen Speichertyp zu entwickeln, sondern auch erfolgreiche erste praktische Tests eines nichtflüchtigen, ladungsbasierten Geräts mit kompakter Größe bei Raumtemperatur durchzuführen. Den Wissenschaftlern gelang es auch, Nichtflüchtigkeit und Niederspannungsumschaltung durch die quantenmechanischen Eigenschaften einer asymmetrischen Dreifachresonanztunnelbarriere zu kombinieren. Forscher sagen, dass ihr Gerät skaliert werden kann, ohne seine Würde zu verlieren.

Die Zeiten ändern sich, ebenso die Technologien. Flash-Speicher, SRAM und DRAM haben unter Speichergeräten seit langem eine beherrschende Stellung inne. Dies könnte sich jedoch ändern, wenn die Entwicklung des universellen Speichers mit dem gleichen Erfolg wie in dieser Studie fortgesetzt wird. Diese Technologie wird den Stromverbrauch der damit ausgestatteten Geräte erheblich reduzieren, ihre Lebensdauer verlängern und die Produktivität steigern.

Weitere von den Autoren geplante Studien werden zeigen, wie revolutionär das Gedächtnis ist, das von Wissenschaftlern stolz als universell bezeichnet wird.

Vielen Dank für Ihre Aufmerksamkeit, bleiben Sie neugierig und haben Sie eine gute Arbeitswoche, Jungs!

Vielen Dank für Ihren Aufenthalt bei uns. Gefällt dir unser Artikel? Möchten Sie weitere interessante Materialien sehen? Unterstützen Sie uns, indem Sie eine Bestellung

aufgeben oder Ihren Freunden empfehlen, einen

Rabatt von 30% für Habr-Benutzer auf ein einzigartiges Analogon von Einstiegsservern, das wir für Sie erfunden haben: Die ganze Wahrheit über VPS (KVM) E5-2650 v4 (6 Kerne) 10 GB DDR4 240 GB SSD 1 Gbit / s von $ 20 oder wie teilt man den Server? (Optionen sind mit RAID1 und RAID10, bis zu 24 Kernen und bis zu 40 GB DDR4 verfügbar).

Dell R730xd 2 mal günstiger? Nur wir haben

2 x Intel TetraDeca-Core Xeon 2x E5-2697v3 2,6 GHz 14C 64 GB DDR4 4 x 960 GB SSD 1 Gbit / s 100 TV von 199 US-Dollar in den Niederlanden! Dell R420 - 2x E5-2430 2,2 GHz 6C 128 GB DDR3 2x960 GB SSD 1 Gbit / s 100 TB - ab 99 US-Dollar! Lesen Sie mehr über

den Aufbau eines Infrastrukturgebäudes. Klasse mit Dell R730xd E5-2650 v4 Servern für 9.000 Euro für einen Cent?