Ich habe beschlossen, diese Notiz über Habré auf Russisch und Englisch zu schreiben, um einen Link dazu sowohl in englisch- als auch in russischsprachigen Foren und Gruppen zu verbreiten. Der russische Text ist keine Übersetzung des Englischen und umgekehrt - ich habe nur zweimal eine Notiz geschrieben (ich hasse es zu übersetzen). Diejenigen, die mein Englisch kritisieren wollen, werden sofort an das Ende des Beitrags geschickt, wo sie in einem stundenlangen Video von meinem Akzent schockiert werden. Ich sehe meine Betonung nicht als Fehler, sondern als Merkmal. Wir alle wissen, dass viele Amerikaner zum Beispiel einen nasopharyngealen britischen Akzent attraktiv finden. Es ist an der Zeit, einem strengen russischen Akzent den gleichen Status zu verleihen. Dazu müssen möglichst viele Russen bei verschiedenen internationalen Veranstaltungen Reden halten. Unser Passwort lautet "Jahre mi Speak From May Hart".

Aber zuerst über die Ausstellung.

Millionen von Gadget-Verbrauchern auf der ganzen Welt sehen sich die Consumer Electronics Show (CES) an, die im Januar in Las Vegas stattfindet. Sie, die nie wussten, was ein D-Trigger ist, argumentieren vor allem, dass vier Gigahertz in den neuesten Prozessoren von AMD und Qualcomm besser sind als drei. Es gibt jedoch eine Ausstellung, die sich nicht an Verbraucher, sondern an Elektronikentwickler richtet. Diese Ausstellung heißt Design Automation Conference (DAC) und findet in einigen Jahren auch in Las Vegas statt, jedoch nicht im Dezember, sondern im Juni.

Jedes Jahr sehen Millionen von Gadget-Liebhabern die Consumer Electronics Show (CES), die im Januar in Las Vegas stattfindet. Diejenigen, die nie die Funktion eines D-Flip-Flops und die Berechnung des statischen Timings gelernt haben, diskutieren Gigahertz-Frequenzen, nachdem sie die neuesten Artikel im Wired-Magazin gelesen haben, die sie als technische Veröffentlichung wahrnehmen. Es gibt jedoch eine andere Konferenz, nicht für die Verbraucher, sondern für die Entwickler von Elektronik. Diese Konferenz heißt Design Automation Conference (DAC) und findet auch in Las Vegas statt, allerdings nicht jedes Jahr und nicht im Januar, sondern im Juni.

Die Branche der Electronic Design Automation (EDA) stellt Software für Hardware-Designer her. EDA wird von drei großen Unternehmen kontrolliert: Synopsys, Cadence und Mentor Graphics (jetzt Teil von Siemens). Sowohl Synopsys als auch Cadence verfügen über einen vollständigen Satz von Produkten, die zum Entwerfen und Simulieren eines digitalen Chips auf mehreren Ebenen erforderlich sind. Der Entwurfsablauf, RTL2GDSII genannt, beginnt mit der Spezifikation und Codierung des Zyklusverhaltens der Schaltung in der Hardwarebeschreibungssprache (Verilog oder VHDL), setzt die Synthese dieser Beschreibung in einem Diagramm logischer Elemente (Netzliste) fort und setzt die Netzliste dann in einer physischen Liste fort Blaupause des Chips und Verlegen von On-Chip-Drähten zum Verbinden der Standardzellen, der Bausteine von ASICs (Application-Specific Integrated Circuits).

Drei große Unternehmen dominieren die Automatisierungsbranche für das Elektronikdesign: Synopsys, Cadence und Mentor Graphics (die Siemens vor einigen Jahren gekauft hat). Synopsys und Cadence haben eine Software entwickelt, die den gesamten RTL2GDSII-Entwurfsweg abdeckt. Ich habe diese Route vor vier Jahren in meinem

vorherigen DAC-Artikel kurz beschrieben:

In den letzten 25 bis 30 Jahren wurde das Design der Mikroschaltung meist in der Sprache der Gerätebeschreibung Verilog (in Europa und beim Militär - VHDL) geschrieben. Danach verwandelt ein spezielles Programm (Logiksynthese) das Design in einen Graphen aus Drähten und logischen Grundelementen, ein anderes Programm (statische Zeitanalyse). teilt dem Designer mit, ob es in das Geschwindigkeitsbudget passt, und das dritte Programm (Ort und Route) legt dieses Design auf der Stelle des Chips fest.

Wenn das Design alle Phasen durchläuft: Codierung auf einem Veril, Debugging, Verifizierung, Synthese, statische Timing-Analyse, Grundrissplanung, Place-n-Route, Extraktion von Parasiten usw. - Es stellt sich heraus, dass eine Datei namens GDSII an die Fabrik gesendet wird und die Fabrik Chips backt. Die bekanntesten Fabriken dieses Typs gehören der Taiwan Semiconductor Manufacturing Company (TSMC).

John Sanguinetti, seit den 1980er Jahren ein Verilog-Guru. John war Gründer einer Firma namens Chronologic Simulation, die bereits in den 1990er Jahren VCS, einen Verilog Compiled Code Simulator, entwickelte. Dieser Simulator ist jetzt eine Eigenschaft von Synopsys. VCS wird von den meisten großen Elektronikunternehmen verwendet. VCS brachte Synopsys Milliarden Dollar Umsatz ein.

An der Seite des Showrooms steht John Sanguinetti, ein früher Verilog-Guru aus den 1980er Jahren und Gründer von Chronologic Simulation. Dieses Unternehmen gab der Welt den schnellen VCS-Simulator (Verilog Compiled Code Simulator), der jetzt Eigentum von Synopsys ist. Dieser Simulator wird von den meisten großen Chipentwicklern verwendet. VCS bringt Synopsys Milliarden von Dollar:

Mentor Graphics ist jetzt Teil von Siemens, dem drittgrößten EDA-Unternehmen. Im Gegensatz zu Synopsys und Cadence verfügt Mentor Graphics nicht über eine vollständige Reihe von RTL2GDSII-Tools. Die beiden bekanntesten Einnahmequellen sind Calibre, eine Reihe von Tools zur Überprüfung des physischen Designs, und Veloce, ein Hardware-Emulator. Das Kaliber enthält beispielsweise ein Werkzeug, das die geometrischen Entwurfsregeln (Breite, Abstand, Gehäuse) auf den endgültigen "Blaupausen" des Chips überprüft. Veloce verwendet FPGA-ähnliche Chips, die

das schnelle Emulieren von Verilog-Designs

simulieren .

Mentor Graphics, das drittgrößte Unternehmen der EDA-Branche, wurde Ende 2016 Teil von Siemens. Im Gegensatz zu Synopsis und Keydens verfügt Mentor nicht über die gesamte Programmkette, die die RTL2GDSII-Route abdeckt. Die beiden Haupteinnahmequellen von Mentor sind das Calibre-Softwarepaket, das in der letzten Phase des Chipdesigns Überprüfungen durchführt, und der Veloce-Emulator (ausgesprochen Velochi). Ein Beispiel für die Überprüfung in Calibre ist der Mindestabstand zwischen den Spuren auf dem Chip,

damit keine Antenneneffekte auftreten .

UPD: korrigiert auf der Grundlage des Kommentars der Amartologie : Bei der Antenne handelt es sich im Allgemeinen um eine andere. Es tritt auf, wenn eine Spur so groß wird, dass sie wie eine Antenne zu arbeiten beginnt und ein Signal mit der Frequenz von Plasmaoszillationen zum Ätzen während der Produktion empfängt.Und der Veloce-Emulator verwendet FPGA-förmige ASICs, um schnell Emulationen von Schaltkreisen zu

simulieren , die auf der logischen Ebene, dh auf der Veril, beschrieben wurden.

Neben hochprofitablen Calibre- und Veloce-Projekten hatte Mentor immer eine große Anzahl anderer Projekte, Produkte, Dienstleistungen, Schulungen und Bildungsprogramme. Zum Beispiel kultiviert Mentor den Bereich der Funktionsüberprüfung, ein kritisch wichtiger Teil des Workflows für digitales Design.

Neben hochprofitablen Projekten wie Calibre und Veloce hat Mentor viele andere Projekte, Produkte, Dienstleistungen, Forschungsprojekte und Bildungsprogramme. Bei Mentor beschäftigen sie sich beispielsweise mit der Funktionsüberprüfung, einem wichtigen Teil des Produktionsprozesses:

Eine Reihe kleiner Unternehmen, darunter Doulos, Willamette HDL und Sunburst Design, verkaufen Hardware-Verifizierungsschulungen an große und mittlere Elektronikunternehmen. Eine solche Nische besteht, weil die Universitäten die Kunst der funktionalen Verifikation nicht richtig lehren und seit Jahrzehnten keine neuen Technologien wie SystemVerilog, UVM, formale Verifikation mit gleichzeitigen Behauptungen, tragbaren Stimuli usw. in ihren Lehrplan aufnehmen. Selbst Stanford hat es meines Wissens nicht im Lehrplan, wenn ich mit ihren Absolventen spreche.

Die Funktionsüberprüfung speist mehrere kleine Unternehmen, die SystemVerilog- und UVM-Schulungen zu erfrischend hohen Preisen an große Unternehmen verkaufen, beispielsweise ein paar tausend Dollar pro Person. Dazu gehören Doulos, Willamette HDL, Sunburst Design und andere:

Eine andere kleine Firma namens Verific. Sie haben nur eine Handvoll Leute, aber sie sind in ihrer Nische sehr erfolgreich. Verific verkauft SystemVerilog-Parser, die von großen und kleinen EDA-Unternehmen eingesetzt werden.

Hier ist ein weiteres kleines, nur wenige Leute, aber sehr erfolgreiches Unternehmen dieser Art namens Verific. Sie verkauft den Parser von Verilog, den viele EDA-Unternehmen verwenden:

Der Gründer von Verific gibt ein Interview auf einer beliebten EDA-Website namens EDA Cafe. Es gibt mehrere andere beliebte EDA-Websites, darunter John Cooleys deepchip.com, aber ich habe John Cooley diesmal nicht auf der DAC-Etage getroffen.

Hier ist der Gründer von Verific, der EDA Cafe, einer in der Branche beliebten Website, ein Interview gibt:

Lassen Sie uns nun über FPGA sprechen.

Lassen Sie uns jetzt über FPGAs sprechen, sie sind PPVM (sie werden mich jetzt korrigieren), sie sind FPGAs.

Was es ist, habe ich auch in meinem

vorherigen DAC-Artikel vor vier Jahren kurz beschrieben:

In der einfachsten Version besteht ein FPGA aus einer Matrix homogener Zellen, von denen jede mithilfe von Multiplexern, die mit den Bits des Konfigurationsspeichers verbunden sind, in ihre Funktion umgewandelt werden kann. Eine Zelle kann ein UND-Gatter mit vier Eingängen und einem Ausgang werden, ein anderes - ein Einzelbitregister usw. Wir laden eine Folge von Bits aus dem Speicher in den Konfigurationsspeicher - und die gegebene elektronische Schaltung wird im FPGA gebildet, das ein Prozessor, ein Anzeigecontroller usw. sein kann.

FPGAs / FPGAs sind keine Prozessoren. Durch „Programmieren“ von FPGAs (Füllen des Konfigurationsspeichers von FPGAs) erstellen Sie eine elektronische Schaltung (Hardware), während Sie beim Programmieren eines Prozessors (feste Hardware) eine Kette von sequentiellen Programmanweisungen hineinschieben (Software).

Zwei der größten Hersteller von FPGA sind Xilinx und Altera, die jetzt zu Intel gehören.

Die beiden größten Unternehmen, die FPGAs herstellen, sind Xilinx und Altera, die jetzt zu Intel gehören:

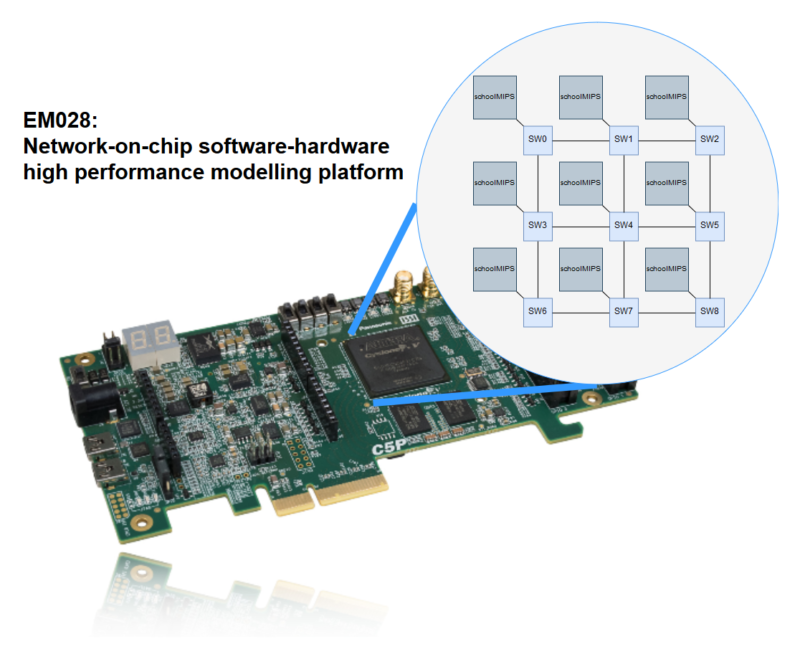

Diese Woche sammelt Intel Stimmen für die erste Runde des Innovate FPGA-Wettbewerbs. Einer der russischen Einträge verwendet ein Netz aus winzigen schoolMIPS-Prozessorkernen.

schoolMIPS implementiert eine Teilmenge der MIPS-Architektur. Es gibt verschiedene Varianten, darunter Einzelzyklus ohne Datenspeicher (der einfachste), eine Version mit Interrupts, eine Pipeline-Version usw.:

Übrigens stimmt Intel diese Woche beim Innovate FPGA-Wettbewerb ab, an dem auch

russische Teams teilnehmen. Ein Projekt ist der

Prototyp eines NoC-basierten Multiprozessorsystems . Dies ist ein Prototyp eines Netzwerks auf einem Chip mit einer großen Anzahl von Knoten, die auf Prozessoren von Stanislav Zhelnio

Sparf basieren (basierend auf Harris & Harris 'Buch „Digitale Synthese und Computerarchitektur“)

https://github.com/MIPSfpga/schoolMIPS . Macht 4-Jahres-Student an der MIEM NRU HSE:

Die Welt der FPGAs ist nicht auf Xilinx und Altera / Intel beschränkt. Es gibt mehrere viel kleinere Anbieter wie Lattice und Microsemi / Actel und sogar kleine Unternehmen, die die Endchips nicht selbst entwerfen, lizenzieren das Design von FPGA-Zellenblöcken an ASIC-Unternehmen. Eine nützliche Anwendung wäre die Erstellung eines rekonfigurierbaren Coprozessors, der an einen festen Hochfrequenz-CPU-Kern angeschlossen ist. Eine andere Anwendung ist die Sicherheit: Einige Unternehmen möchten ihre Geheimnisse in rekonfigurierbarer Logik verbergen, anstatt einem motivierten Forscher mit Elektronenmikroskop und viel Zeit das Layout ihrer festen Logik zu zeigen.

Es gibt jedoch weniger Player in der FPGA-Welt. Hier sind beispielsweise zwei Unternehmen, die das Design von FPGA-Blöcken lizenzieren, die in Festnetzschaltungen mit mehreren Durchläufen eingebettet werden können, um ihnen Flexibilität zu bieten.

Jeder DAC hat mehrere Anbieter von FPGA-Karten. Nicht die Anbieter billiger Studenten-Boards wie Digilent und Terasic, die ab 55 US-Dollar erhältlich sind, sondern FPGA-Boards für ASIC-Prototypen, die 30.000, 100.000 oder mehr US-Dollar kosten können.

Der DAC wird traditionell von Herstellern von FPGA-Karten besucht. Sie verkaufen keine billigen Studentenausweise für 55 Dollar, sondern ernsthafte FPGA-Boards für 55 Tausend Dollar und mehr. Ihr Kunde ist kein Student, sondern ein strenges ASIC-Entwicklungsteam, das große Boards für das Prototyping verwendet.

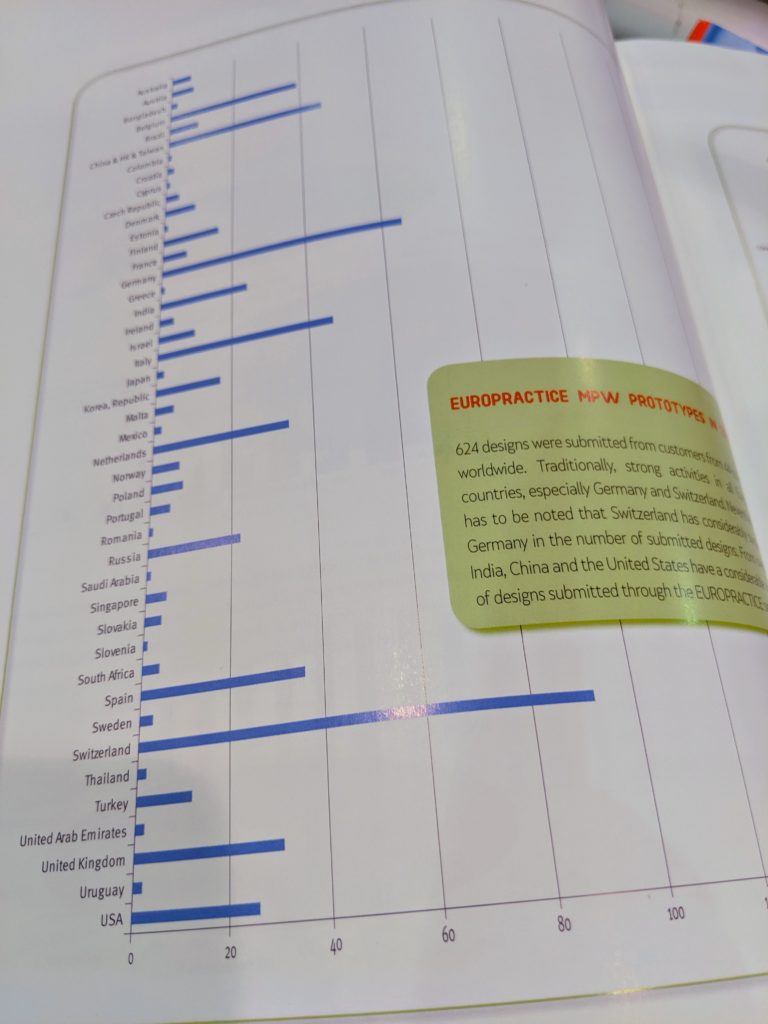

Was wäre, wenn ein Forscher einen Proof of Concept mit FPGA durchführen würde und nun seinen eigenen ASIC herstellen möchte? Ein typischer kommerzieller Auftrag zur Herstellung eines ASIC erfordert normalerweise die anfängliche Zahlung von ~ 300.000 bis ~ 3.000.000 USD, abhängig von der Prozesstechnologie. Es gibt jedoch spezialisierte Unternehmen, Europractice in Europa und MOSIS in den USA, die kleine Shuttle-Dienste oder MPW-Dienste (Multi-Project Wafer) verkaufen, beginnend mit nur 3000 US-Dollar für 180-nm-Technologie oder nur zehntausend US-Dollar für etwas Modernes wie 28nm.

Aber was ist, wenn ein Student oder eine harte Firma einen echten ASIC in einer Fabrik herstellen wollte und es wenig oder wenig Geld gibt? Oder, wenn nicht leid, ist es ein Testchip oder eine sehr kleine Charge? Zu diesem Zweck gibt es in Amerika eine Firma MOSIS und in Europa Europractice. Ein paar tausend Dollar - und Sie haben den Chip in der Hand, den Sie für Technologien wie 180 Nanometer entwickelt haben. Ein paar Zehntausende - und Sie haben Ihren Chip in der Hand über neuere Technologien, zum Beispiel 28 Nanometer, wie das fünfte iPhone. Ich stelle fest, dass für die kommerzielle Massenproduktion die anfängliche Zahlung an die Fabrik von Hunderttausenden von Dollar für alte Technologien bis zu zwei oder drei Millionen für neue Technologien reicht.

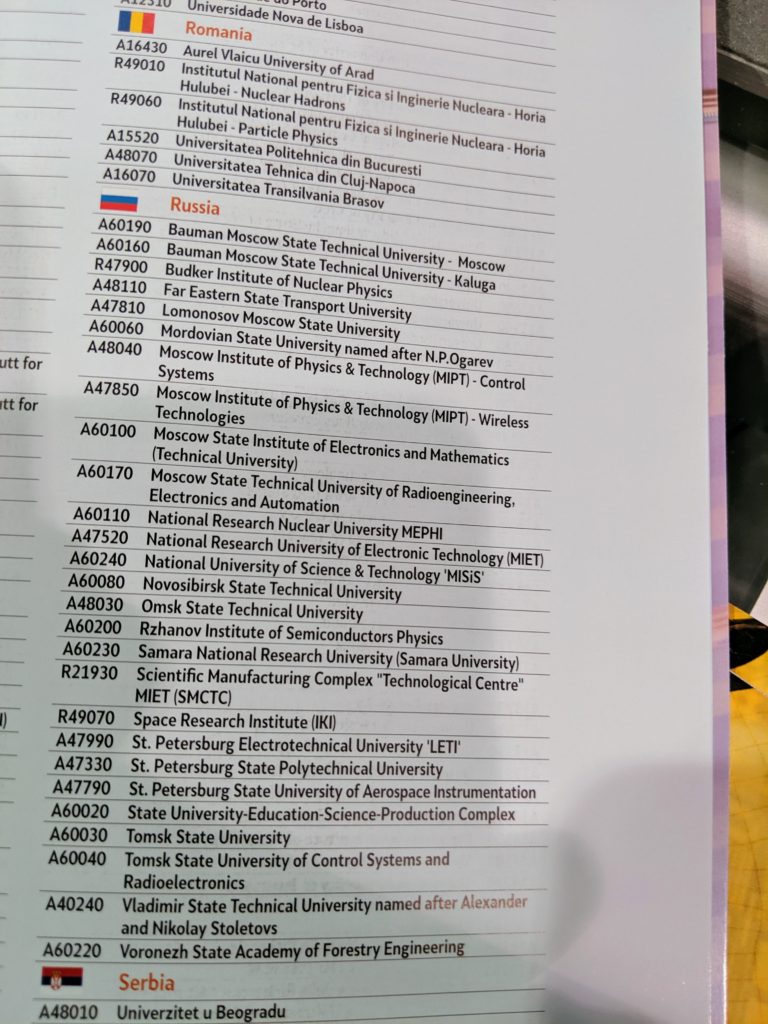

Es ist interessant, dass Europractice Kunden in Russland hat, sogar in Omsk. Geben Sie zu, wer die ASICs in Omsk entwirft.

Europractice hat eine Reihe russischer Unternehmen, darunter jemanden in Omsk:

Es gibt Unternehmen mit Geschäftsmodellen, die mir etwas rätselhaft sind. Zum Beispiel verstehe ich nicht, wie diese Firma unten auf einem Nischen-Eclipse-Plugin überleben kann. Ich denke, sie erzielen die meisten Einnahmen mit dem Verkauf einiger Beratungsdienste.

Es gibt Unternehmen, bei denen ich nicht verstehe, wie sie verdienen. Zum Beispiel verkauft dieses ein sehr Nischen-Eclipse-Plugin. Sicherlich leben sie nicht von ihm, sondern von einer Art Beratung.

Ein weiteres Nischenunternehmen mit nicht offensichtlichem Geschäftsmodell. Sie übersetzen eine Beschreibung von durch Software sichtbaren Registern in Verilog-Klebelogik und andere Schnittstellendateien. Ich denke, dieses Unternehmen hat möglicherweise einen großen Kunden vom Typ Cisco, der sich vor langer Zeit auf seine Technologie verliebt hat und sie seitdem bezahlt.

Ein weiteres Nischenunternehmen mit einem nicht offensichtlichen Geschäftsmodell. Sie übersetzen die Beschreibung der Register, die dem Programmierer zur Verfügung stehen, in Verilog- und Schnittstellendateien. Sie haben wahrscheinlich einen großen Kunden wie Cisco, der sich vor vielen Jahren in sein Tool verliebt hat und seitdem bezahlt, da es ein Mist ist, einen Kunden für die Verwaltung seines Ingenieurs einzustellen.

Ein melancholischer Gentleman von Huawei beschrieb ihre Erfolge bei der Vernetzung von Chips. Huawei ist offensichtlich mehr von US-amerikanischen EDA-Tools abhängig als von Android Market- und ARM-CPU-Kernen. Der Geldbetrag und die Anzahl der technischen Experten, die für die Entwicklung eines Äquivalents des Synopsys IC-Compilers erforderlich sind, sind meiner Meinung nach viel größer als die Ressourcen, die für die Entwicklung eines High-End-Konkurrenten für ARM-Kerne erforderlich sind.

Ein Vertreter von Huawei saß ebenfalls mit einem Ausdruck heller Traurigkeit im Gesicht auf der Ausstellung. Ich stelle fest, dass, wenn die US-Regierung US-amerikanische EDA-Unternehmen zwingt, die Chinesen zu verbieten, die chinesische Situation viel schlimmer sein wird als jetzt, da es technisch schwieriger ist, Synopsys IC Compiler zu klonen als ARM- und Android Market-Prozessorkerne.

In jedem DAC seit 1998 entwickelte mindestens ein Unternehmen einen weiteren C-to-Verilog-Compiler. 1998 war es

mein eigenes Startup . Dieses Jahr ist es jemand anderes:

Seit 1998 gibt es mindestens ein Unternehmen auf DAC, das C in Verilog kompiliert. 1998 war ein solches Unternehmen mein eigenes Startup. Dieses Jahr jemand anderes:

Dieser Herr verdient seinen Lebensunterhalt mit dem Verkauf von Lösungen, die dem sogenannten "Zakladki" (ein russischer Begriff, ein Plural von "Zakladka") entgegenwirken. Ich erklärte ihm die Bedeutung des Begriffs und er stimmte zu, dass er dies verkauft.

Hier ist ein Begleiter, der in Prozessoren Lesezeichen für lebende Analysatoren erstellt:

Ich habe meine Studententochter zum DAC gebracht, damit sie sehen kann, wie Papa seinen Lebensunterhalt verdient:

Ich brachte meine Tochter nach Las Vegas, damit sie sehen konnte, wie Menschen in der rauen Industriewelt der Elektronikindustrie Geld verdienen, und erkannte, dass die Dollars ihres Vaters nicht auf Bäumen wuchsen:

Party nach der Ausstellung:

Auf der Party nach der Ausstellung:

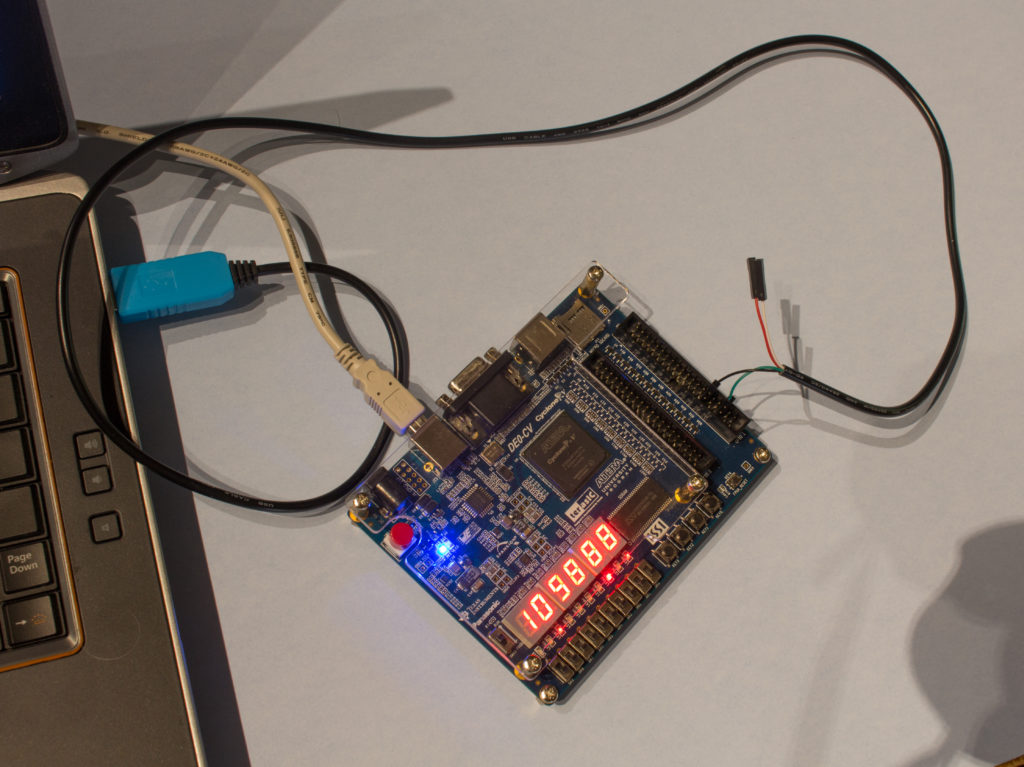

Nach der Ausstellung habe ich zusammen mit meinen Kollegen von Wave Comnputing den MIPS Open Developer Day durchgeführt. Wir haben eine Reihe von Leuten von einigen der oben genannten Unternehmen + meine russischen Freunde von

VivEng , einem kalifornischen Silicon Valley Mixed-Signal-Design-Service, der auch einige Kunden in Zelenograd, einem russischen Silicon Valley, hatte. Zuerst machten wir eine

Präsentation , dann machten die Teilnehmer einige Übungen auf Digilent Nexys4 DDR- und Terasic DE10-Lite FPGA-Boards.

Dann führte ich zusammen mit meinen Kollegen das MIPS Open-Seminar durch. Er wurde von Kameraden einiger der beschriebenen Unternehmen besucht, darunter diejenigen, die eingebettete FPGA- und EDA-Tools lizenzieren, Dienstleistungen für die Produktion verkaufen, Schulungen zur Verifizierung durchführen und auch Chips als solche herstellen. Und auch meine alten Freunde von der russischen Firma

VivEng . Meine Kollegen und ich zeigten

diese Folien , woraufhin die Teilnehmer Beispiele für FPGAs Digilent Nexys4 DDR und Terasic DE10-Lite ausprobierten.

Um die Ergebnisse zu wiederholen, können Sie zwei Pakete herunterladen und kombinieren:

Wenn Sie die Ergebnisse reproduzieren möchten, können Sie Folgendes tun:

- Gehen Sie zu https://www.mipsopen.com/mips-open-components/mips-open-fpga-getting-started-guide .

- Laden Sie das Standardpaket MIPSfpga 2.0 herunter.

- Gehen Sie zu https://github.com/MIPSfpga/mipsfpga-plus .

- Git-Klon github.com/MIPSfpga/mipsfpga-plus.git

- Kopieren von RTL-Kerndateien aus dem MIPS Open FPGA-Paket in das Kern-Unterverzeichnis des MIPSfpga + -Pakets - siehe Anleitung unter https://github.com/MIPSfpga/mipsfpga-plus/tree/master/core

Auf Ihrem Computer müssen entweder Intel FPGA Quartus Prime Lite Edition oder Xilinx Vivado sowie die Codescape GCC Bare Metal Toolchain installiert sein. Danach können Sie den Anweisungen auf den Folien folgen:

Auf Ihrem System muss Intel FPGA Quartus Prime Lite Edition oder Xilinx Vivado sowie die Codecape GCC Bare Metal Toolchain installiert sein. Danach können Sie den Anweisungen auf den Folien folgen:

- cd your_git_directory / board / board_directory (zum Beispiel de10_lite oder nexys4_ddr)

- mach alles laden

- Drücken Sie Reset (oder bei einigen Karten KEY 0), um den Prozessor zurückzusetzen.

- Das fest codierte Standardprogramm sollte funktionieren.

- cd your_git_directory / programme / 00_counter (oder ein anderes programm)

- mache das Programm srecord uart

- Wenn der Computer eine andere serielle Verbindung als ttyUSB0 (Standardeinstellung) verwendet, gilt Folgendes:

- make program srecord uart UART = 1 (oder 2, 3 usw.)

- Das über USB-zu-UART hochgeladene Programm läuft jetzt.

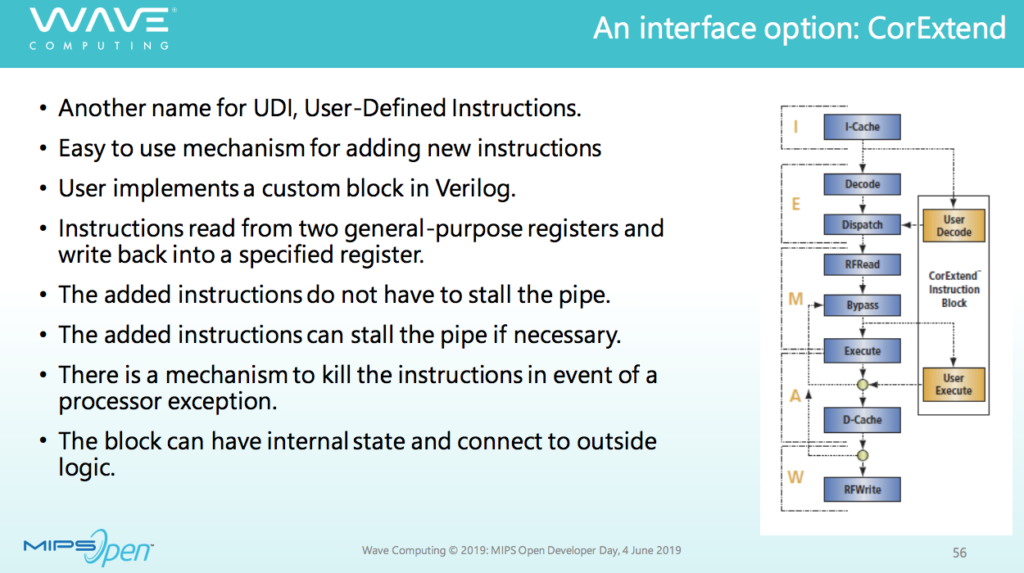

In der Präsentation habe ich gezeigt, wie ein Block in den Prozessor eingebettet wird, der zusätzliche Anweisungen für das Hauptsystem von Befehlen decodiert und ausführt, die vom Systemdesigner auf einem Chip bestimmt werden können. Der Block kann synthetisiert werden und Teil der Mikroschaltung werden oder im FPGA / FPGA konfiguriert werden.

Zusätzliche Anweisungen werden zusammen mit den Hauptanweisungen entlang der Prozessor-Pipeline verschoben. Sie empfangen Daten aus allgemeinen Registern, die für den Programmierer sichtbar sind, und können das Ergebnis an das Register zurückgeben. Diese Anweisungen können auch einen bestimmten Status im Coprozessor speichern. Sie können durch Ausnahmen gelöscht werden, wenn eine Ausnahme auftritt, z. B. in der Pipeline, die dieser Anweisung folgt:

Die Präsentation enthält eine ausführliche Erklärung, wie Sie dem MIPS microAptiv UP-CPU-Kern benutzerdefinierte Prozessoranweisungen hinzufügen und diese zusammen mit einem einfachen SoC für FPGA-Karten synthetisieren können:

Verilog-Hardware-Code-Snippet aus dem Beispieltext. Dieser Code implementiert auf der Registerübertragungsebene (RTL) eine spezielle Anweisung zum Berechnen eines neuronalen Faltungsnetzwerks:

Ein Fragment eines benutzerdefinierten CorExtend-Moduls, das eine benutzerdefinierte Anweisung (User-Defined Instruction, UDI) für einen speziellen Fall der Berechnung des neuronalen Netzes implementiert:

Morgen fliege ich nach Russland, um bei einem weiteren Seminar zu helfen, nicht für Elektronik- und EDA-Profis, sondern für Kinder, die sich für Karrieren im Bereich digitales mikroelektronisches Design interessieren. Für diese Reise habe ich einen einfachen 2D-Videoprozessor erstellt, der in den MIPS Open FPGA-Kern integriert ist, sowie ein Beispiel für ein reines Hardware-Spiel (keine CPU oder Software) für VGA. Kinder mögen Spiele und ich werde Spieldesign verwenden, um ihnen die Grundlagen der RTL-Methodik beizubringen:

Und am kommenden Montag

, dem 8. Juli, werde ich in Zelenograd die Grundlagen der Entwicklung digitaler Schaltkreise für Schulkinder vermitteln .

Für ihn habe ich Beispiele für die Implementierung einfacher Sprite-Grafiken auf FPGA geschrieben. Eine aus Verilog synthetisierte Schaltung zeichnet Sprites auf einem VGA-Bildschirm.

Hier ist ein funktionierendes Beispiel für eine saubere Hardware (

Quellcodes auf Github ). Eine Variante des Seekampfes, bei der ein roter Torpedosatellit nach einem feindlichen blauen Kreuz jagt:

Und hier ist ein Beispiel für eine Kombination aus Hardware und Software - ein Gruß von Sprites.

Hardware- und

Softwareteil :

Ja, und ich habe versprochen, meine Reden in Las Vegas zu halten. Hier ist ein Stück:

Blick auf den Las Vegas Strip, wenn es dunkel wird, aber es gibt noch keine Menschenmassen:

Und der Blick auf die Straße auf dem Strip, wenn es schon Abend ist, aber es gibt noch keine Menschenmassen:

Während zwei Tagen in Las Vegas hatte ich keine Chance zu spielen, also spielte ich mit 1 Dollar, als unser Flugzeug zurück nach San Jose am Flughafen von Las Vegas einstieg:

Während dieser ganzen Zeit habe ich nie in Las Vegas gespielt, weil ich durch die Ausstellung gelaufen bin und über elektronische Themen gesprochen habe, dann habe ich ein Seminar abgehalten. Aber beim Einsteigen in das Flugzeug habe ich trotzdem einen Dollar verloren: