Dieser Artikel beschreibt die Installation und Verwendung von freier Software zur Modellierung digitaler Logikschaltungen in Verilog als Alternative zu kommerziellen Produkten Incisve von Cadense und ModelSim von MentorGraphics. Vergleich von Simulationen in ModelSim und Verilator. Eine universelle Verifizierungsmethode, UVM, wird ebenfalls in Betracht gezogen.

Installation der SystemC UVM-Software

1. Der Verilator

Eine der Hardwarebeschreibungssprachen ist Verilog. Sie können ein Modul in dieser Sprache schreiben.

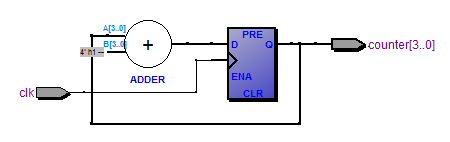

Zum Beispiel gibt es ein Zählerschema:

Der Code sieht folgendermaßen aus:

reg [3:0]counter; always @(posedge clk or posedge reset) if(reset) counter <= 4'd0; else counter <= counter + 1'd1;

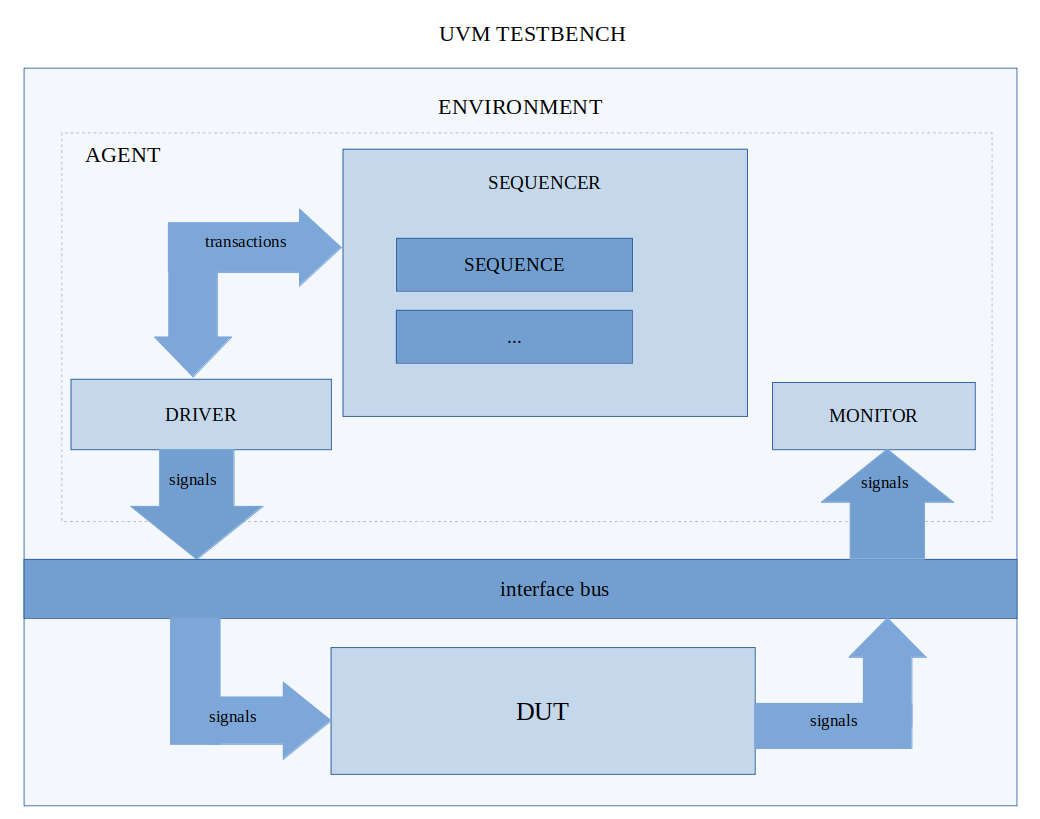

Nach der Simulation erhalten wir die Wellenformen:

Es ist ersichtlich, dass der nächste Wert, einer mehr als der vorherige, in die Zählerregister entlang der Taktfrequenzfront geschrieben wird.

Ein geschriebenes Modul kann eine komplexere Struktur haben, bei der es schwierig ist, alle Zustände von manuell zu überprüfen. Wir brauchen automatisierte Tests. Dazu ist es notwendig, eine Testumgebung in einer der Programmiersprachen zu entwickeln. Die Testumgebung gibt uns die Möglichkeit, eine vollständige Funktionsprüfung des Geräts durchzuführen.

Zum Testen des Projektcodes können Sie zusätzlich zu Sprachen wie Verilog, SystemVerilog, Python (zum Schreiben von Modellen) die

SystemC- Sprache verwenden. SystemC ist eine Entwurfs- und Überprüfungssprache auf Systemebene für Modelle auf Systemebene, die als Open Source C ++ - Bibliothek implementiert sind.

Eine Möglichkeit, Verilog-Module mit SystemC zu überprüfen, besteht darin, Verilog-Dateien in C ++ zu übersetzen. Helfen Sie uns mit diesem Verilator.

Verilator ist der schnellste kostenlose Verilog HDL-Simulator, der die meisten kommerziellen Simulatoren übertrifft. Verilator kompiliert synthetisierten SystemVerilog (normalerweise ist dies kein Testbed-Code) sowie einige Anweisungen von SystemVerilog und Synthesis in C ++ - oder SystemC-Code mit einem oder mehreren Threads. Verilator wurde für große Projekte entwickelt, bei denen die Simulationsleistung von größter Bedeutung ist, und eignet sich besonders gut zum Generieren ausführbarer Prozessormodelle für eingebettete Softwareentwicklungsteams. Verilator wird verwendet, um viele sehr große Gateway-Designs im Wert von mehreren Millionen Dollar mit Tausenden von Modulen zu simulieren. Es wird von vielen IP-Technologieanbietern unterstützt, darunter IP von Arm und allen renommierten RISC-V-IP-Anbietern.

Verilator ist möglicherweise nicht die beste Wahl, wenn Sie für ein sehr kleines Projekt einen voll ausgestatteten Ersatz für NC-Verilog, VCS oder einen anderen kommerziellen Verilog-Simulator oder Verilog-Verhaltenssimulator erwarten. Wenn Sie jedoch nach einer Möglichkeit suchen, synthetisiertes Verilog nach C ++ oder SystemC zu portieren, und Ihr Team nur C ++ - Code schreiben kann, ist dies ein kostenloser Verilog-Compiler für Sie.

So installieren Sie die neueste Version unter Ubuntu: Laden Sie das Archiv

über den Link von der offiziellen Website herunter.

Installieren:

2. GTK Wave

GTKWave ist ein voll funktionsfähiger Wellenform-Viewer, mit dem Sie Dateien bequemer und schneller vom VCD- in das FST-Format konvertieren können.

Installieren:

sudo apt-get install gtkwave

3. SYSTEMC

Eine Sprache zum Entwerfen und Überprüfen von Modellen auf Systemebene, die in Form einer Open Source C ++ - Bibliothek implementiert sind.

Wie bereits erwähnt, unterstützt Verilator systemc. Daher müssen Sie ein Projekt erstellen, in dem der Testbenchmark in systemc und die Quelldateien in synthetisiertem verilog beschrieben werden. Dazu benötigen wir die von Accelera bereitgestellten g ++ - Compiler-Bibliotheken. Die Accellera Systems Initiative ist eine unabhängige, gemeinnützige Organisation, die sich der Erstellung, Unterstützung, Förderung und Förderung von Design-, Simulations- und Verifizierungsstandards auf Systemebene für den Einsatz in der globalen Elektronikindustrie widmet.

Laden Sie das Archiv herunter:

http://accellera.org/images/downloads/standards/systemc/systemc-2.3.1a.tar.gzInstallieren:

tar -xvf systemc-2.3.1a.tar.gz cd systemc-2.3.1a mkdir objdir sudo ./configure --prefix=/usr/local/systemc-2.3.1a/ sudo make sudo make install cd ../

4. UVM für SYSTEMC

In diesem Artikel wird ein Projekt beschrieben, das UVM-Überprüfungstools implementiert. Die Überprüfung ist eine Bestätigung der Konformität des Endprodukts mit vordefinierten Referenzanforderungen. Eines ihrer Überprüfungswerkzeuge können Tests sein. Um Testsequenzen auf Modellen realer Geräte auf der Ebene der RTL-Beschreibungen auszuführen, muss eine Testumgebung entwickelt werden.

UVM - (Universal Verification Methodology) ist eine universelle Verifizierungsmethode, ein Standard, der die effiziente Entwicklung und Wiederverwendung von IP-Blockvalidierungsumgebungen ermöglicht. UVM ist eine Verifizierungsmethode, deren Aufgabe darin besteht, eine effektive Umgebung um das zu testende Gerät herum zu organisieren. Seine Vorteile:

- klare Struktur in Form von dedizierten Blöcken, die spezifisch entscheiden

- Aufgaben

- die Fähigkeit, Blöcke in nachfolgenden Projekten wiederzuverwenden;

- die maximal mögliche Automatisierung der Überprüfung;

- Die umfassendsten Berichtsinformationen, die es ermöglichen, im Fehlerfall die Ursachen so schnell und genau wie möglich zu identifizieren und Lösungen vorzuschlagen.

UVM-Methoden bestehen aus zwei Teilen: einem Regelwerk zum Erstellen einer Testumgebung und einer Bibliothek von Blockleerzeichen zur Überprüfung, z. B. einem Textgenerator, einem Statistiksammler usw. Der Hauptvorteil von UVM ist seine Vielseitigkeit und Kompatibilität mit Umgebungen von Drittanbietern.

Da systemc die UVM-Methode unterstützt, fahren wir mit der Installation der erforderlichen Bibliotheken fort.

Laden Sie das Archiv herunter:

https://www.accellera.org/images/downloads/drafts-review/uvm-systemc-1.0-beta2.tar.gzInstallieren:

tar -xvf uvm-systemc-1.0-beta2.tar.gz cd uvm-systemc-1.0-beta2/ mkdir objdir sudo ./configure --prefix=/usr/local/systemc_uvm/ --with-systemc=/usr/local/systemc-2.3.1a sudo make sudo make install

Wir bilden eine Allianz:

sudo mkdir /usr/local/uvm_systemc_aliance

Kopieren Sie den Inhalt der Ordner / usr / local / uvm_systemc_aliance / und /usr/local/systemc-2.3.1/ in diesen Ordner

Laden Sie das fertige Projekt unter folgendem Link herunter:

https://github.com/paprikun/SYSTEMC/Öffnen Sie den Verilator-Beispielordner.

Der Ordner rtl enthält eine Beschreibung des Geräts. In diesem Beispiel handelt es sich um einen PWM-Controller.

In der Makefile-Datei des Sim-Ordners zum Erstellen des Projekts.

Im tb-Ordner befindet sich der Code für den Verifizierer. Der Ordner tb / uvm enthält ein Beispiel für eine uvm-Umgebung. Die Hauptdatei ist ein Einstiegspunkt beim Testen und verbindet das zu testende Gerät mit der UVM-Umgebung.

Wir versuchen, das Projekt mit dem Befehl make all aus dem Ordner sim zu erstellen. Wir sehen einen Fehler:

/usr/local/uvm_systemc_aliance//include/systemc.h:120:16: error: 'std::gets' has not been declared using std::gets;

Wir beheben das Problem, indem wir Zeile 120 ersetzen:

#if defined(__cplusplus) && (__cplusplus < 201103L) using std::gets; #endif

Wir versuchen erneut, die Testbench auszuführen und stoßen auf eine Warnung:

/usr/local/uvm_systemc_aliance//include/sysc/packages/boost/get_pointer.hpp:21:40: warning: 'template<class> class std::auto_ptr' is deprecated [-Wdeprecated-declarations] template<class T> T * get_pointer(std::auto_ptr<T> const& p)

Ändern Sie auto_ptr in unique_ptr.

Projektmontage und Simulation

Nachdem die Bibliotheken installiert sind und funktionieren, erstellen wir das Projekt: make all. Die ausführbare Datei von simu sollte im Ordner sim angezeigt werden. Dies ist ein vom Compiler erstelltes Objekt. Wir beginnen es mit dem ./simu Team. Folgendes sollte angezeigt werden:

SystemC 2.3.1-Accellera --- Jun 28 2019 11:39:29 Copyright (c) 1996-2014 by all Contributors, ALL RIGHTS RESERVED Universal Verification Methodology for SystemC (UVM-SystemC) Version: 1.0-beta2 Date: 2018-10-24 Copyright (c) 2006 - 2018 by all Contributors See NOTICE file for all Contributors ALL RIGHTS RESERVED Licensed under the Apache License, Version 2.0 UVM_INFO @ 0 s: reporter [RNTST] Running test ... simulation real time = 9 sec UVM_INFO uvm_default_report_server.cpp(666) @ 179490249010 ps: reporter [UVM/REPORT/SERVER] --- UVM Report Summary --- ** Report counts by severity UVM_INFO : 1 UVM_WARNING : 0 UVM_ERROR : 0 UVM_FATAL : 0 ** Report counts by id [RNTST] 1 UVM_INFO @ 179490249010 ps: reporter [FINISH] UVM-SystemC phasing completed; simulation finished

Wenn die Simulation beendet ist, endet die Aufzeichnung der Wafeform. Die Datei simu.vcd kann mit gtkwave geöffnet werden:

Um die Signale auf der linken Seite anzuzeigen, wählen Sie SystemC, halten Sie die Umschalttaste gedrückt, wählen Sie alle Signale aus und klicken Sie auf Anhängen. QuickInfos werden in der Symbolleiste angezeigt, wenn Sie den Mauszeiger bewegen. Der Mauslauf funktioniert, Sie müssen Shift oder Cntrl gedrückt halten.

Es gibt auch Möglichkeiten, diese Datei in eine andere kleinere zu konvertieren.

Wenn es Modelle gibt, wird die Konvertierung durchgeführt. Geben Sie im Terminal den Befehl vsim ein. In den Terminalmodellenim:

vcd2wlf simu.vcd simu.wlf

Oder mit gtkwave im Linux-Terminal:

vcd2lxt simu.vcd simu.lxt vcd2lxt2 simu.vcd simu.lxt2

Um die Simulationszeit zu vergleichen, wurde ein ähnliches Projekt erstellt, jedoch bereits für

Modelsim . Ordner modelsim_example. Ähnlich erstellte UVM-Umgebung. Die Syntax ist trotz der Tatsache, dass verschiedene Sprachen ähnlich sind. Wenn Sie Modelsim mit UVM-Unterstützung installiert haben, können Sie den Befehl make all ausführen.

Zusätzlich zur Umgebung wurde in beiden Projekten eine Echtzeitsimulation von Messungen durchgeführt.

Der Zeitunterschied ist:

Wie Sie der Tabelle entnehmen können, hat der Verilator einen Vorteil. Die Daten werden für einen PC mit 8 GB RAM, einem 8-Kern-Prozessor mit 800 MHz und einem Kern angezeigt.

Vergleichen Sie die Dateigröße:

Hier verliert der Verilator, aber Sie können mit dem Erstellen von Wellenformen und der Spurentiefe experimentieren, die Aufzeichnungsperiode (Beginn und Ende der Wellenformaufzeichnung können verschoben werden). Mit welcher Datei Sie arbeiten möchten, liegt bei Ihnen.

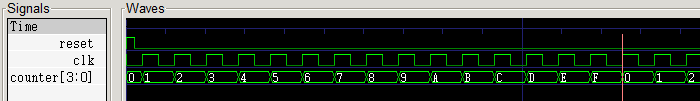

Während des Testens wurde zusätzlich zum Zeitpunkt der Simulation selbst eine Diskrepanz beim Lesen der Eingabedaten vom In-Bus festgestellt. Wenn sich die Daten vom In-Bus während der Clk-Front ändern, liest Modelsim die Daten nach dem Front-Verilator vor:

input clk; input [7:0] in; reg [7:0] in_last_ ; ... always @(posedge clk) begin ... in_last_ <= in; ... end

Beim Testen muss dieser Punkt berücksichtigt werden, da ein Teil der Testumgebung für verschiedene Simulatoren unterschiedlich funktioniert.

Außerdem berücksichtigt der Verilator nicht den "x" -Zustand des Signals und übersetzt alles in "0";

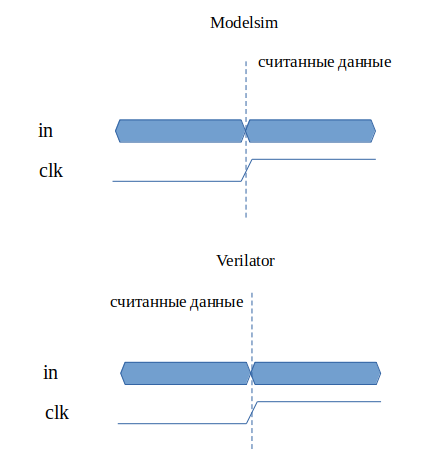

UVM TESTBENCH

Betrachten Sie die Testumgebung, den Ordner tb / uvm.

UVM-Testbench ist die Umgebung über dem Gerät. In diesem Beispiel ist das Gerät ein PWM-Controller. UVM-Umgebungsdiagramm:

Wie Sie im Diagramm sehen können, besteht UVM aus Blöcken (Klassen). Jeder Block erfüllt seine Funktionen. Das Beispiel zeigt eines der möglichen Layouts der Testumgebung. Der Name und die Funktionalität jeder Klasse entsprechen der Klasse, von der sie geerbt wurde. Lassen Sie uns jede Klasse genauer betrachten.

Umgebungsdatei env.h oder env.svh. Dies ist eine Klasse, die eine oder mehrere Agentenklassen enthalten kann, in denen drei Klassen verbunden sind: Sequenzer, Treiber, Monitor. Das Beispiel enthält keinen Agenten, aber seine Funktion ist in der env-Klasse implementiert. Für den Test müssen wir eine Sequenz von Aktionen schreiben - Sequenzierung.

Fahren wir mit dem Startcode für die Sequenzierung fort:

sequence_[n]->start(sqr, NULL);

Sequenzer (Sequenzer) - Datei sequncer.h. In System Verilog wurde der Standard-Sequenzer verwendet. Eine Klasse, die eine oder mehrere Sequenzen (Sequenz) enthält (Dateien sequence_a.h, sequence_a.svh). Jede Sequenz ist eine Kette von Aktionen. Eine dieser Aktionen kann das Senden einer Transaktion sein. Transaktion - Übertragung von Daten von einer Klasse zu einer anderen. Die Klasse, in der die Transaktionen beschrieben werden, ist bus_trans. Nachfolgend finden Sie eine Beschreibung von zwei Klassen, von denen jede ideologisch ihre eigenen spezifischen Funktionen hat: Treiber und Monitor.

Treiber - Datei drv.h, drv.svh. Eine Klasse, die Transaktionen von einem Sequenzer empfängt und in Signale übersetzt. Der Fahrer dient als Sequenzerassistent auf einer niedrigeren Ebene. Ziehen Sie in Betracht, ein Paket zu senden.

Die Sequenz öffnet ein Transaktionsfenster, der Treiber erkennt dieses Ereignis und beginnt mit dem Empfang von Daten. Die Sequenz wartet auf eine Antwort des Fahrers. Der Treiber simuliert die Signale für das Gerät und signalisiert dem Sequenzer, dass das Fenster geschlossen werden kann. Die Idee ist, dass der Sequenzer auf einem hohen Niveau und der Treiber auf einem niedrigeren Niveau arbeitet.

Die Signale werden über den Schnittstellenbus mit dem Gerät verbunden. Die Schnittstelle ist in den Dateien vip_if.h, vip_if.svh beschrieben.

Als nächstes müssen Sie überprüfen, ob die Ausgangssignale mit den erwarteten übereinstimmen. Es gibt zwei Lösungen:

- Schreiben eines Modells für ein Gerät

- Signalüberprüfung durch UVM Agent

Im Beispiel wird die zweite Option berücksichtigt. Um das Gerät auf Funktionsebene zu testen, muss die Ausgabe mit der erwarteten verglichen werden. Die Anforderung an das Gerät war die Richtigkeit des gegebenen Arbeitszyklus des Signals und der Periode des Signals. Um die Ausgangssignale zu überwachen, wird eine neue Klasse geschrieben - Monitor (Datei monitor.h, monitor.svh). Normalerweise überträgt der Monitor in einer Testumgebung die Signale in der Transaktion (auf eine höhere Ebene) und wird an die Vergleichsklasse - Anzeigetafel - gesendet.

In diesem Beispiel werden die Signale sofort überprüft. Bei Abweichungen zwischen dem erwarteten und dem gemessenen Wert stoppt der Test.