Zwischenfertigungsprozesse, verschiedene Arten von Transistoren und viele andere Optionen erhöhen die Unsicherheit des Elektronikfertigungsprozesses.

Die Elektronikhersteller bereiten sich auf die nächste Welle innovativer Herstellungsprozesse vor, aber ihre Kunden werden mit einer Reihe verwirrender Optionen verwirrt sein - ob sie Chips mit der 5-nm-Prozesstechnologie entwickeln, 3 nm warten oder etwas dazwischen wählen.

Der Weg zu 5 nm ist im Gegensatz zu 3 nm gut definiert. Danach wird die Landschaft verwirrt, da Fabriken Zwischenfertigungsprozesse wie 6 nm und 4 nm hinzufügen. Die Umstellung auf einen dieser technischen Prozesse ist sehr teuer und die Vorteile liegen nicht immer auf der Hand.

Ein weiterer Grund zur Sorge ist die schrumpfende Produktionsbasis. Bei den fortschrittlichsten technischen Prozessen ist die Auswahl der Hersteller gering. Es gab mehrere führende Hersteller in der Branche, aber im Laufe der Zeit hat sich dieser Bereich aufgrund eines starken Anstiegs der Kosten und eines Rückgangs der Anwenderbasis verengt. Je weniger Hersteller, desto weniger Optionen für Technologie und Preis.

Heute sind Samsung und TSMC die

einzigen beiden Hersteller, die mit technologischen Prozessen von 7 nm oder weniger arbeiten, obwohl sich dies ändern kann. Intel und das chinesische Unternehmen SMIC entwickeln fortschrittliche Herstellungsverfahren. Intel, nicht der größte Anbieter auf dem Gebiet der kommerziellen Produktion, hat Probleme mit der Entwicklung der 10-nm-Prozesstechnologie. Und es ist unklar, ob SMIC 7 nm ausgeben kann, da sich dieses Thema noch in der Forschungs- und Entwicklungsphase befindet (dasselbe passiert mit Intel mit der 10-nm-Prozesstechnologie).

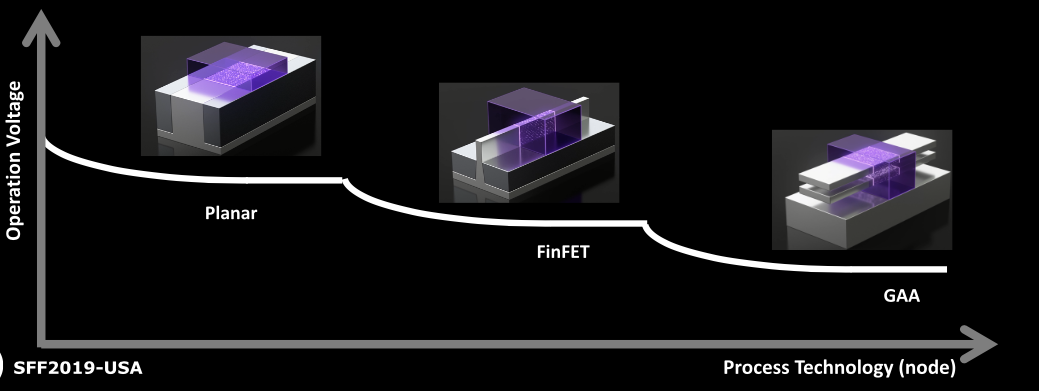

Bei fortgeschritteneren Herstellungsverfahren arbeiten Samsung und TSMC mit 7 nm unter Verwendung von FinFET-Transistoren, und beide Hersteller werden dies bei 5 nm fortsetzen. Im Gegensatz zu herkömmlichen planaren Transistoren sind FinFETs dreidimensionale Strukturen mit besserer Leistung und geringerer Leckage.

Bei 3 nm wird Samsung dann vom FinFET zur neuen Nanoblatt-FET-Transistorarchitektur übergehen, die eine Entwicklung der FinFET-Technologie darstellt. TSMC hat seine Pläne für 3 nm noch nicht bekannt gegeben, so dass viele Kunden in der Schwebe bleiben. Laut Quellen wiegt TSMC eine Vielzahl von Optionen ab, darunter Nanoschichten, Nanodrähte und erzwungene FinFETs. Intel, TSMC und andere arbeiten ebenfalls an neuen Formen fortschrittlicher Verpackungen als mögliche Optionen für das Downscaling.

Bei 3 nm kann die Größe der Transistortechnologie jedoch in verschiedene Richtungen gehen. FinFET kann immer noch abgespielt werden, aber diese Technologie benötigt einige Durchbrüche. Offensichtlich muss sich die Branche auf den Übergang zur neuen Architektur der 3-nm-Prozesstechnologie und der nächsten Zwischenprozesstechnologie bei 2 nm vorbereiten, gemessen an den Entwicklungsplänen einer in diesem Bereich tätigen Organisation.

"5 nm ist immer noch FinFET", sagte Naoto Horiguchi, Programmdirektor bei Imec. - Nehmen wir an, wir treten bei 3 nm in eine Übergangsperiode vom FinFET zu anderen Architekturen ein. Wir glauben, dass dies Nanoschichten sein werden. “

Nanolayer-FETs beziehen sich auf die Architektur von Gate-Allround-Transistoren (GAA). Und dies ist nicht die einzige Option. „Die Branche ist sehr konservativ. Die Teilnehmer werden versuchen, alles vom FinFET bis zum Limit zu quetschen “, sagte Horiguchi. - Beim 3-nm-Herstellungsprozess haben wir die Möglichkeit, FinFET zu verwenden. Wir müssen jedoch einige FinFET-Innovationen vornehmen und diese allgemein verbessern. “

Bleiben die Chiphersteller auf der 7-nm-Prozesstechnologie, migrieren sie auf 5 nm, 3 nm oder auf das Zwischenprodukt? 7 nm bietet genügend Leistung für fast alle Anwendungen, sodass dieser Prozess lange anhält. Draußen gibt es mehrere Hochleistungsoptionen, die alle mehr kosten. Und wir werden sehen, ob diese Technologien Zeit haben, pünktlich zu erscheinen.

Die Betriebsspannung verschiedener Herstellungsprozesse beträgt planare Transistoren, FinFET und Nanoschicht-FET.

Die Betriebsspannung verschiedener Herstellungsprozesse beträgt planare Transistoren, FinFET und Nanoschicht-FET.Produktionsruine

Der Chip besteht aus vielen Transistoren, die als Schalter wirken. Über viele Jahrzehnte hinweg stimmte der Fortschritt integrierter Schaltkreise mit dem Moore'schen Gesetz überein, wonach sich die Dichte von Transistoren auf einem Gerät in einem Zeitraum von 18 bis 24 Monaten verdoppelt.

In einem ähnlichen Rhythmus führten die Hersteller neue technologische Verfahren mit einer höheren Dichte an Transistoren ein, die es der Industrie ermöglichten, die Kosten für Chips in Bezug auf die Anzahl der Transistoren zu senken. Bei jedem Herstellungsprozess skalierten die Hersteller die Transistorspezifikationen um das 0,7-fache, sodass die Industrie die Produktivität bei gleichem Energieverbrauch und zweifacher Flächenreduzierung um 40% steigern konnte.

Die Industrie für integrierte Schaltkreise folgte dieser Formel und florierte. Seit den 1980er Jahren ebnet es den Weg für schnelle PCs zu ermäßigten Preisen.

Bis 2001 gab es bereits mindestens 18 Hersteller mit Fabriken, in denen sie Chips bei 130 nm herstellen konnten, was laut IBS zu diesem Zeitpunkt ein fortschrittlicher technischer Prozess war. Außerdem erschienen mehrere neue Hersteller, die in den Fabriken anderer Leute maßgeschneiderte Chips herstellten. Darüber hinaus wurde die Chipherstellung für Laboratorien praktiziert, die sie entwickelten, aber keine eigene Produktion hatten.

Bis zum Ende des Jahrzehnts stiegen die Kosten für Produktions- und Herstellungsprozesse. Viele Chiphersteller konnten den Preisanstieg nicht bewältigen und wechselten zum Fab Lite-Modell. Sie produzierten einige Chips zu Hause und der Rest wurde ausgelagert.

Im Laufe der Zeit stellten weniger Chiphersteller fortschrittliche Geräte in ihren eigenen Einrichtungen her. Einige haben die Produktion komplett eingestellt oder das Geschäft verlassen.

In den 2000er Jahren erschien jedoch ein Geschäftsmodell für Siliziumwerkstätten. Die Workshops blieben hinter Intel und anderen Technologieunternehmen zurück, ermöglichten Designunternehmen jedoch den Zugang zu verschiedenen Prozessen.

Die nächste große Änderung erfolgte im 20-nm-Stadium, als herkömmliche planare Transistoren gegen eine Wand stießen und auf

einen Kurzkanaleffekt stießen. Als Reaktion darauf stellte Intel 2011 bei 22 nm auf die Transistortechnologie der nächsten Generation, finFET, um. Die Workshops wurden bei 16/14 nm auf FinFET umgestellt.

FinFET hat gegenüber planaren Transistoren mehrere Vorteile. „Bei diesem Schema erstreckt sich der gesamte Transistor vertikal, sodass der Kanal über das Substrat steigt und das Ventil drei Seiten der Rippe umschließt. Die vergrößerte Kontaktfläche des Ventils ermöglicht eine bessere Kontrolle des Leckstroms “, schreiben Matt Kogorno und Toshihiko Miyashita von Applied Materials. Kogorno ist der Direktor des globalen Produktmanagements und Miyashita ist der Cheftechnologe.

FinFET ist auch komplexer, es ist schwieriger, sie für jeden nachfolgenden technischen Prozess herzustellen und zu skalieren. Infolgedessen stiegen die Kosten für Forschung und Entwicklung in den Himmel. Jetzt ist der Rhythmus einer vollwertigen Prozessänderung von 18 Monaten auf 2,5 Jahre oder mehr angewachsen.

Auch die Preise für integrierte Schaltkreise steigen weiter. Die Kosten für die Entwicklung eines planaren Geräts bei 28 nm variieren laut Gartner zwischen 10 und 35 Millionen US-Dollar. Zum Vergleich: Die Kosten für den Entwurf eines Single-Chip-Systems (SoC) bei 7 nm variieren zwischen 120 und 420 Millionen US-Dollar.

"Die Entwicklungskosten hängen stark von der Komplexität des SoC ab", sagte Samuel Wen, Analyst bei Gartner. - Zwei Drittel fließen in die Entwicklung des Chips. Der Rest ist die Entwicklung von U-Booten, die Kosten für Masken und eine verbesserte Leistung. Mit der Zeit sinken auch die Designkosten. “

Die Preisentwicklung hat jedoch die Landschaft der Welt der integrierten Schaltkreise verändert. Mit der Zeit können es sich weniger Unternehmen leisten, für das Chipdesign für die fortschrittlichsten Herstellungsprozesse zu bezahlen. Viele von ihnen verlassen sich bei Produktionsfragen auf Workshops.

Ein Rückgang der Kundenzahl sowie ein Anstieg der Produktionskosten beeinflussten die Landschaft der Werkstätten, in denen fortschrittliche Chips hergestellt wurden. Zum Beispiel gibt es auf dem 16/14-nm-Markt noch fünf Hersteller / Werkstätten: GlobalFoundries, Intel, Samsung, TSMC und UMC. SMIC arbeitet auch mit finFET an einer 14-nm-Prozesstechnologie.

Und bei 7 nm geschah ein weiterer Übergang. Die technologischen Prozesse und die Produktionskosten stiegen weiter an, und die Kapitalrendite war bereits fraglich. Infolgedessen haben GlobalFoundries und UMC im vergangenen Jahr aufgehört, eine 7-nm-Prozesstechnologie zu entwickeln. Beide Unternehmen sind weiterhin auf dem 16/14-nm-Markt tätig.

Samsung und TSMC versuchen sich weiterzuentwickeln und rasen mit voller Geschwindigkeit bis zur Wende von 7 nm und darüber hinaus. Nach mehreren Verzögerungen plant Intel, die Produktion Mitte 2019 bei 10 nm und bis 2021 bei 7 g zu starten. SMIC verspricht keine Fristen.

Aber nicht alle Werkstattkunden benötigen fortschrittliche Herstellungsverfahren. Es gibt einen florierenden Markt für 28-nm-Chips. "Es hängt alles von den Eigenschaften des Produkts ab", sagte Ven von Gartner. - Einige Produkte erfordern maximale Leistung. Entwickler können weiterhin veraltete technische Prozesse verwenden. Und Chips für Anwendungen, die keine hohe Leistung erfordern, können von den Herstellungsprozessen N-1 und N-2 leben. “

Andere wiederholen ihn. „Wie viele Unternehmen können sich heute aus wirtschaftlicher Sicht das neueste Silizium leisten? Ihre Zahl nimmt ab. In Märkten, die eine extrem hohe Leistung erfordern, wird dies immer der Fall sein. In der Lieferkette bildet sich jedoch volumenmäßig ein Bruch in der Mitte. Die anspruchsvollsten Kunden benötigen technologische Prozesse bei 7, 5 und möglicherweise eines Tages bei 3 nm. Aber alle anderen haben sich etwas verlangsamt “, sagte Walter Eun, Vice President of Business Management bei UMC.

In bestimmten Fällen werden jedoch die fortschrittlichsten Chips benötigt - dies sind Server und Smartphones. Es gibt auch eine Menge neuer Startups im Zusammenhang mit KI-Chips. Viele Unternehmen entwickeln Chips für maschinelles Lernen und Deep Learning.

„Niemand argumentiert, dass die Notwendigkeit, etwas zehnmal schneller als heute zu zählen, auch in nichttechnischen Märkten immer wirtschaftlich nützlich und wettbewerbsfähig sein wird. All diese einzigartigen Errungenschaften der Deep-Learning-Technologie sind ein Beweis dafür. Anfragen nach immer größerer Computerleistung haben buchstäblich kein Ende “, sagte Aki Fujimura, Direktor von D2S.

"Die Anforderungen an die Rechenleistung haben mehrere große Veränderungen erfahren - zuerst war es die GPU und später das tiefe Lernen", sagte Fujimura. - Deep Learning ist eine massive Technologie, um geeignete Muster zu finden, und das Training neuronaler Netze ist die Aufgabe einer konsequenten Optimierung. Nachdem die Welt einen Mechanismus entwickelt hat, mit dem eine große Datenmenge verarbeitet und in nützliche Informationen in Form eines Programms umgewandelt werden kann, das logische Schlussfolgerungen ziehen kann, wächst die Anzahl der erforderlichen Berechnungen mit der verfügbaren Datenmenge. Und da die Datenmenge in allen Bereichen exponentiell wächst, werden die Anforderungen an die Rechenleistung zumindest im Bereich Deep Learning garantiert erheblich steigen. “

Ob die AI-Chips technische Prozesse von 5 nm oder mehr erfordern, bleibt unklar, aber es gibt definitiv Anforderungen für eine Erhöhung der Rechenleistung. Die Migration zu diesen technologischen Prozessen wird jedoch nicht einfacher oder billiger.

5 nm vs 3 nm

Anfang 2018 erreichte TSMC einen weiteren Meilenstein und war damit der weltweit erste Hersteller, der die 7-nm-Prozesstechnologie einsetzte. Samsung nahm später am 7-nm-Rennen teil. Das Verfahren zur Herstellung von Chips bei 7 nm basiert hauptsächlich auf FinFET und besteht aus der Herstellung von Chips mit einem Gate-Schritt von 56 bis 57 nm und einem Mindestschritt zum Platzieren von Metallleitern [Metallabstand] bei 40 nm nach Informationen von IC Knowledge und TEL.

In der ersten Version von 7 nm verwendete TSMC 193 nm

Immersionslithographie und Mehrfachstrukturierung. In diesem Jahr verspricht TSMC die Veröffentlichung einer neuen Version von 7 nm mit extremer Ultraviolettlithographie (EUV). EUV vereinfacht die Prozessschritte, ist jedoch eine teure Technologie und hat ihre eigenen Schwierigkeiten.

TSMC bereitet seine neue 5-nm-Prozesstechnologie für die Veröffentlichung im ersten Halbjahr 2020 vor. Neue Technologien von TSMC bei 5 nm sind 15% schneller als 7 nm und verbrauchen 30% weniger Energie. Die zweite Version der 5-nm-Prozesstechnologie, die nächstes Jahr herauskommt, wird 7% schneller sein. Beide Versionen verwenden EUV.

TSMC erhält bereits Aufträge bei 5 nm. "Von Apple, HiSilicon und Qualcomm werden Großaufträge erwartet", sagte Handel Jones, IBS Director. "Das Volumen der Substrate wird bis zum vierten Quartal 2020 40.000 - 60.000 pro Monat betragen."

Die Übergangsgeschwindigkeit bei 5 nm für TSMC beträgt weniger als 7 nm. Erstens ist 5nm ein völlig neuer Prozess mit aktualisierten EDA-Tools und Patenten. Außerdem ist es teurer. Laut Gartner variieren die Kosten für die Entwicklung eines Geräts bei 5 nm im Durchschnitt zwischen 210 und 680 Millionen US-Dollar.

Einige Chiphersteller möchten von 7 nm wegkommen, ohne so viel Geld wie 5 nm auszugeben. Aus diesem Grund hat TSMC kürzlich eine neue 6-nm-Prozesstechnologie eingeführt, die zwar billiger ist, jedoch einige Kompromisse aufweist.

"Die Zahlen N6 und N5 scheinen nicht unterschiedlich zu sein, aber tatsächlich ist die Lücke groß", sagte S. S. Wei, Direktor von TSMC beim letzten Treffen. - Bei N5 ist die logische Dichte im Vergleich zu N7 um 80% erhöht. N6 im Vergleich zu N7 nur 18%. Wie Sie sehen können, gibt es einen großen Unterschied zwischen der logischen Dichte und der Effizienz von Transistoren. Infolgedessen ist der Gesamtstromverbrauch des N5-Chips geringer. Der Wechsel zu N5 bietet viele Vorteile. Aber N5 ist ein vollwertiger technischer Prozess, und es braucht Zeit, bis Kunden neue Produkte dafür entwickeln. Das Schöne an N6 ist, dass sie, wenn sie bereits ein Projekt unter N7 haben, nur sehr wenig Aufwand betreiben müssen. Sie können auf N6 upgraden und erhalten bestimmte Vorteile. Und abhängig von den Eigenschaften des Produkts und des Marktes entscheiden die Kunden, was zu tun ist. “

In der Zwischenzeit hat Samsung 5 nm eingeführt, das in der ersten Hälfte des Jahres 2020 erscheinen wird. Im Vergleich zu 7 nm bietet die neue 5-nm-Prozesstechnologie von Samsung bei finFET bis zu 25% Logikverdichtung und 20% weniger Stromverbrauch oder 10% mehr Geschwindigkeit.

Samsung führte auch eine neue 6-nm-Prozesstechnologie ein, die den Kunden eine weitere Option bietet. "6nm hat den Vorteil der Skalierbarkeit mit 7nm und der Wiederverwendung von geistigem Eigentum", sagte Ryan Lee, Vice President Marketing für Workshops bei Samsung. Und Samsung plant bereits die Entwicklung des 4-nm-FinFET mit Prozesstechnologie. Bisher gibt es praktisch keine offenen Informationen zu dieser Technologie.

Nach 5 nm kostet eine Reihe vollwertiger Herstellungsprozesse 3 nm. Aber 3 nm ist nichts für Weicheier. Die Kosten für die Entwicklung eines Geräts für die 3-nm-Prozesstechnologie liegen laut IBS zwischen 500 und 1,5 Milliarden US-Dollar. Die Kosten für den Entwicklungsprozess variieren zwischen 4 und 5 Milliarden US-Dollar und für die Produktion zwischen 15 und 20 US-Dollar. "Die Kosten für 3-nm-Transistoren sollten 20-25% über 5 nm bei gleicher Verfügbarkeit liegen", sagte Jones von IBS. „Wir können eine Effizienzsteigerung von 15% und eine Reduzierung des Energieverbrauchs um 25% im Vergleich zu 5-nm-FinFET erwarten.“

Samsung ist das einzige Unternehmen, das Pläne zur Entwicklung einer 3-nm-Prozesstechnologie bekannt gibt. Zu diesem Zweck wird der Workshop auf die Architektur von Kreistransistoren, Nanoschichten, umstellen. TSMC hat noch keine Pläne bekannt gegeben, weshalb einige glauben, dass das Unternehmen im Rückstand ist. "Mit 3 nm wird Samsung höchstwahrscheinlich 2021 in die Serienproduktion gehen", sagte Jones. "TSMC beschleunigt die Entwicklung, indem es versucht, mit Samsung Schritt zu halten."

Bei 3 nm untersucht TSMC Nanolayer-FETs, Nanodraht-FETs und sogar FinFETs. Eine Möglichkeit zur Erweiterung der FinFET-Technologie ist die Verwendung von Materialien mit hoher Mobilität in den Kanälen, nämlich in Deutschland. Heutige FinFET-Bauelemente verwenden Silizium oder Silizium-Germanium (SiGe) in Kanälen. Durch Erhöhen der Beimischung von Germanium können Sie die Mobilität des Kanals erhöhen, dh die Geschwindigkeit des Durchgangs von Elektronen durch das Gerät. Und hier ist das Problem das Fehlermanagement.

Die Erweiterung der FinFET-Technologie ist sinnvoll. Der finFET bei 3 nm liefert einen Übergangspfad von 5 nm. Es gibt jedoch Probleme. Theoretisch stößt die FinFET-Technologie auf eine Sackgasse, wenn die Rippenbreite 5 nm erreicht, was nahe am aktuellen Zustand liegt. "Heute verwenden wir zwei Flossen für NMOS und drei für PMOS in einer Standardzelle", sagte Horiguchi von Imec. - Einer der wichtigen Aspekte von 3 nm ist, dass wir für Standardzellendesigns auf eine Single-Fin-Architektur umsteigen müssen. Eine einzelne Flosse sollte gut genug funktionieren. Um die FinFET-Technologie auf N3 zu erweitern, benötigen wir eine spezielle Technologie, um die Leistung einer einzelnen Finne zu verbessern und Hintergrundstörungen zu reduzieren. “

Neben der hohen Mobilität von FinFET ist GAA die nächste Option. 2017 führte Samsung den Multi Bridge Channel FET (MBCFET) für 3 nm ein. MBCFET - Nanolayer-FET. Samsungs Test-MBCFET wird im Jahr 2020 verfügbar sein.

Nanolayer-Chips haben Vorteile gegenüber FinFET. Beim FinFET biegt sich der Verschluss von drei Seiten um die Finne. In Nanoschichten befindet sich der Verschluss an vier Seiten der Rippe, wodurch der Strom besser gesteuert werden kann.

Im Vergleich zu 5 nm bieten die Nanolayer-FETs von Samsung eine Steigerung der Effizienz des logischen Bereichs um bis zu 45% und eine Reduzierung des Stromverbrauchs um 50% oder der Geschwindigkeit um 35%. „Die FinFET-Struktur hat ihre eigenen Einschränkungen hinsichtlich der Skalierbarkeit, da die Versorgungsspannung nicht unter 0,75 V gesenkt werden kann. Unsere Innovation unter Verwendung von Nanoschichten ermöglicht es uns, die Spannung auf Werte unter 0,7 V zu reduzieren“, sagte Samsung Lee.

Es gibt verschiedene Arten von GAA-Technologien, einschließlich Nanolayer-FET und Nanodraht-FET. GAA selbst ist der nächste Schritt nach dem FinFET. In diesem System befindet sich der FinFET auf seiner Seite und wird dann in horizontale Teile geteilt. Stücke bilden Kanäle. Das Verschlussmaterial wird um jede Schicht gewickelt.

Im Vergleich zu Nanodraht-FET hat eine solche Schaltung breitere Kanäle, dh eine höhere Produktivität und einen höheren Erregerstrom. "Nanoschichten haben effektivere Breiten", sagte Imec Horiguchi. "Nanodrähte sind mit Elektrostatik viel besser." Ihr Querschnitt ist jedoch sehr klein. Dies bietet keine Vorteile hinsichtlich der effektiven Kanalbreite. "

GAA-Architekturen weisen mehrere Probleme auf. Normalerweise ergeben sie einen extrem geringen Anstieg im Vergleich zu FinFET bei 5 nm. Die Herstellung von Chips mit dieser Technologie ist ziemlich schwierig.

"Die GAA der nächsten Generation bei 3 nm und darunter erhöht die Komplexität der Fertigung noch weiter", sagte Richard Gotshaw, Vice President und technischer Direktor von Lam Research . - Auf den ersten Blick sieht es nach einer Modifikation des FinFET aus. Die Anforderungen steigen jedoch und die Komplexität dieser GAA-Architektur ist erheblich höher als bei FinFET. “Bei der Herstellung von Nanoschichtchips besteht der erste Schritt darin, dünne abwechselnde Schichten aus SiGe und Silizium auf dem Substrat zu platzieren. „Wir bekommen einen Stapel Silizium, Silizium-Germanium, Silizium. Wir nennen es Übergitter “, sagte Namsun Kim, Chief Engineering Officer bei Applied Materials, kürzlich in einem Interview. "Mit Germaniumgehalt muss man es mit einer guten Isolationsschicht versehen."Die Packung sollte mindestens aus drei Schichten SiGe und drei Silizium bestehen. Dann werden winzige Blattstrukturen auf die Packung aufgebracht. Danach wird eine Isolierung mit Rillen und dann inneren Trennwänden gebildet.Dann werden SiGe-Schichten aus dem Übergitter entfernt, wobei Siliziumschichten mit einem leeren Raum zwischen ihnen verbleiben. Jede Siliziumschicht bildet die Basis der Folie oder des Kanals in der Vorrichtung. Dann müssen Sie ein Material mit einer hohen Dielektrizitätskonstante auftragen, um einen Verschluss zu erzeugen. „Zwischen Nanodrähten besteht ein Mindestabstand. Sehr klein. Das Problem besteht darin, dort Metall mit Arbeitsdicke zu platzieren “, sagte Kim.Die Branche hat im Laufe der Jahre an der Entwicklung der GAA-Technologie gearbeitet, aber es gibt immer noch einige Probleme. "Einer der wichtigsten ist der parasitäre Tank", sagte Kim. - Wenn Sie mich fragen, was die Hauptprobleme der GAA-Technologie sind, dann gibt es zwei davon. Interne Trennwände und Substratisolierung. "Was weiter?

Wie lange reicht GAA-Technologie oder Nanoschichten aus? „Nanoschichten werden die zwei oder drei der nächsten Prozesstechnologie überleben. Workshops können Nanoschichten auf N3 herstellen. Die nächste Generation ist sicher. Danach müssen Sie möglicherweise die Integration von Nanoschichten oder Architektur ändern. Aber es wird immer noch eine Nanolayer-Architektur sein “, sagte Horiguchi von Imec.Die Industrie sucht nach Möglichkeiten zur Verbesserung der GAA- und FinFET-Technologien in fortschrittlichen Herstellungsprozessen. GAA-Geräte bieten derzeit einen leichten Vorteil gegenüber FinFET. Beispielsweise betrug der Verschlussabstand des vorherigen Imec-Nanoschichtchips 42 nm und der minimale Abstand der Metallleiter 21 nm. Im Vergleich dazu können FinFETs bei 5 nm einen Gate-Abstand von 48 nm und einen minimalen Abstand von Metallleitern von 28 nm aufweisen.Im Labor demonstrierte Imec die Skalierbarkeit eines p-Halbleiterbauelements mit einem Doppelstapel aus GAA und Germanium im Kanal. Imec hat unter Verwendung einer erweiterungsfreien Schaltung einen Nanodraht mit einer Gatelänge von etwa 25 nm entwickelt. Es kann für Nanoschichten angepasst werden. Wie bei der vorherigen Version beträgt die Drahtgröße 9 nm.Germanium kann eine Rolle bei der weiteren Verwendung von FinFET außerhalb der 5-nm-Prozesstechnologie spielen. Imec zeigte Ge nFinFET mit Rekordhoch Gmsat / SSsat und PBTI. Sie wurden erreicht, indem der Ersatz von Material mit hohem Dielektrikum verbessert wurde.Wir werden auch sehen, ob die FinFET-Technologie auf 3 nm erweitert werden kann. Es ist auch unklar, ob Nanolayer-Chips rechtzeitig erscheinen werden. Es gibt viele Unbekannte und Unsicherheiten in dieser sich verändernden Landschaft, und es gibt keinen Zeitplan für die Klärung der Situation.