Schließlich wurde in Russland ein

Lehrbuch über SystemVerilog auf einem höheren Niveau als für Anfänger veröffentlicht . Das Lehrbuch beschreibt die Technologien und Techniken, die für Interviews bei NVidia, Intel, AMD, Apple und anderen elektronischen Unternehmen benötigt werden: die Verwendung gleichzeitiger Behauptungen und funktionaler Abdeckung, für die jetzt nicht nur Verifizierungsingenieure, sondern auch Chipdesigner erforderlich sind; der Algorithmus des Simulators mit Delta-Zyklen; vernünftige Erklärung der statischen Timing-Analyse; Kommunikationsdiagramme von Hardwareeinheiten über Hardware-Warteschlangen; die Implementierung dieser Kommunikation unter Verwendung von Finite-State-Maschinen mit Datenpfaden usw.

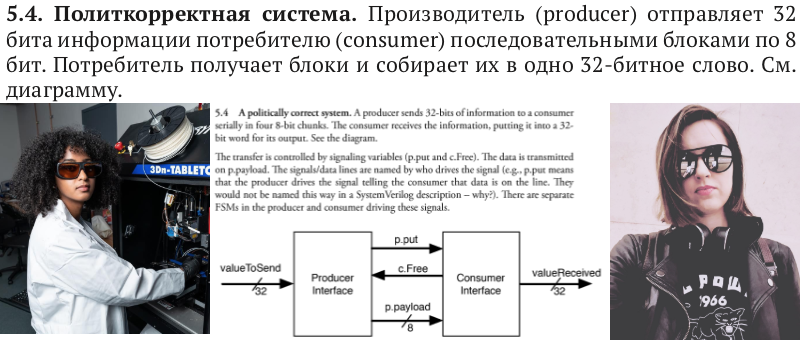

In dem Kapitel über Letzteres kann der russische Leser durch die Erwähnung eines „politisch korrekten Systems“ verwirrt sein. Was würde das bedeuten? Dies ist wahrscheinlich eine Anspielung auf den

Vorfall, der sich 2003 in Los Angeles County ereignete . Beamte aus Los Angeles forderten Hersteller, Zulieferer und Auftragnehmer auf, die Verwendung der Begriffe "Master / Slave" für Computerausrüstung einzustellen, da einer der Mitarbeiter des Landkreises an die Sklavenvergangenheit erinnert wurde.

Jetzt meiden Autoren der technischen Literatur die Begriffe Master / Slave. Afroamerikanische Ingenieure arbeiten auch im modernen Amerika (zum Beispiel Sofia Mvokani aus Kamerun - auf dem Foto links), und die Verwendung alter Begriffe sieht archaisch aus, da beispielsweise die Begriffe „Pan / Slave“ in der ukrainischen Fachliteratur anstelle des akzeptierten „Lead / Lead“ aussehen würden ( Russischer "Führer / Sklave").

Dies ist nicht das erste Mal, dass das Thema des Kampfes der Afroamerikaner für Bürgerrechte in der russischen elektronischen Bildung auftaucht. Zum Beispiel trägt Tatyana Volkova, eine bekannte Spezialistin für Elektronikausbildung, ein T-Shirt mit dem Emblem von „Black Panthers“, der kalifornischen Bewegung, die einst den friedlichen Protest für unzureichend hielt und sich auf bewaffneten Protest einließ.

Das vollständige Bild des Emblems unter der Haut von Tatyana Alexandrovna ist unter dem Schnitt, aber hauptsächlich werde ich über Delta-Zyklen und Zustandsmaschinen sprechen:

Unten sehen Sie einen Screenshot des Artikels über Master / Slave und das versprochene Black Panther-Emblem. Danach fahren wir mit dem Buch als solchem fort.

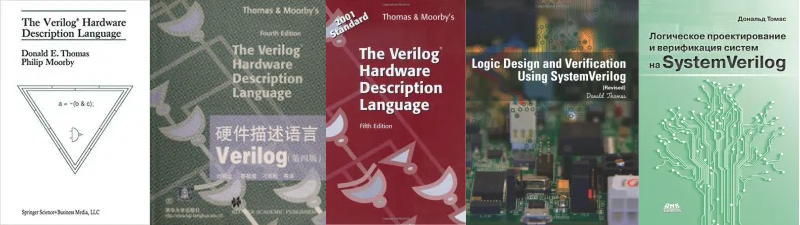

Zunächst ist Donald Thomas, Autor des Buches

„Logisches Design und Verifizierung von Systemen auf SystemVerilog“ (2019 in russischer Sprache von DMK-Press, 2016 in englischer Sprache) derselbe Donald Thomas, der zusammen mit Philip Murbi 1991 ein Buch verfasst hat Die Verilog Hardware Description Language von Donald Thomas und Philip Moorby. 1991 entwarfen viele Elektronikunternehmen noch immer Mikrochips auf die alte Art und Weise und zeichneten sie mit der Maus auf den Bildschirm. logische Synthesetechnologien haben gerade das Labor für die Produktion verlassen; Hardwarebeschreibungssprachen wurden als zum Schreiben von Modellen und Tests gedacht angesehen und nicht als Quellcodes zum Erstellen endgültiger Schaltkreise. Zusätzlich zu VHDL und Verilog, die zu dieser Zeit geschlossen waren, gab es viele kleine und proprietäre Sprachen wie Abel, CUPL, PALASM; und Intel und MIPS hatten interne Hardwarebeschreibungssprachen.

In dieser Situation erschien das Buch von Thomas und Murbi, das für die Designer digitaler Schaltungen der neunziger Jahre das gleiche war wie das Buch für Kernigan-Richie für die Programmierer für C und die Bücher von Bjarni Straustrup für die C ++ - Programmierer. Das Buch hat fünf Ausgaben überlebt - von 1991 bis 2002, aber für die Ära der iPhones war es eindeutig unzureichend. Und im Jahr 2016 beschloss Donald Thomas, ein neues Buch zu veröffentlichen, in dem er die wichtigsten Innovationen in Sprache und Methodik über 25 Jahre beschrieb. In den 25 Jahren, in denen Verilog zu einer gemeinsamen Basis für die gesamte Branche geworden ist, werden Pläne für alles geschrieben, von den berüchtigten iPhones und Steuercomputern in Tesla bis hin zu russischen Militärhubschraubern.

Als nächstes werde ich meine Kommentare mit blauem Text hervorheben, um sie von den Bildern aus dem Buch zu trennen.

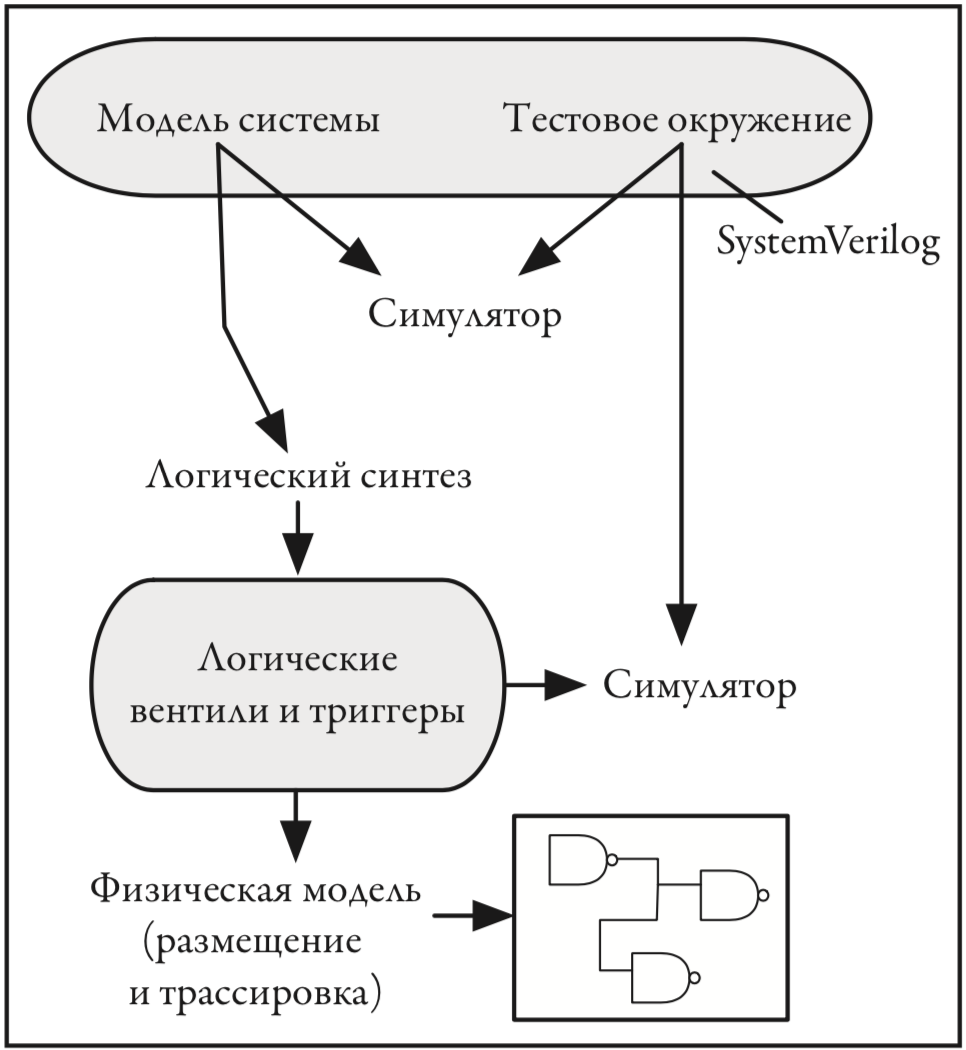

Noch vor dem Haupttext des Buches gibt es das Vorkapitel „Kontext: Design auf der Ebene der Registerübertragungen“, damit ein Programmierer, ein Schulkind oder beispielsweise ein Liebhaber von Übungen mit Steckbrettern sofort versteht, worum es geht und wie er das Buch verwenden kann. Es heißt:Digitale Systeme werden mit Milliarden von Transistoren auf einem Chip hergestellt. Ein Amateur kann natürlich mehrere Logikgatter zeichnen und sie als Spezifikation mit Drähten verbinden (für die Implementierung auf einem Steckbrett), aber für kommerzielle Projekte ist dies eine alte Geschichte ... Moderne Systeme werden in Hardwarebeschreibungssprachen wie SystemVerilog spezifiziert.

Gleichzeitig ist hier ein so vereinfachtes Bild, um zu veranschaulichen, wie sich der Text auf der Veril in der Fabrik in Spuren und Transistoren der Mikroschaltung verwandelt:

Das erste Wort im Buch nach dem Vorwort ist "Simulator". Um die Hardwarebeschreibungssprachen zu verstehen, müssen Sie sich darüber im Klaren sein, dass die synthetisierte Teilmenge des Verilog keine Programmiersprache ist, sondern eine Sprache zur Beschreibung elektrischer Schaltkreise. Angenommen, HTML ist keine Programmiersprache, sondern eine Sprache zur Beschreibung von Webseiten. Während eine Programmiersprache in eine Kette von Prozessoranweisungen kompiliert werden soll, soll eine Hardwarebeschreibungssprache (insbesondere) in Prozessoreisen als solches umgewandelt werden. In diesem Fall muss vor dem Gießen in Eisen der Code in der Hardwarebeschreibungssprache überprüft werden. Zu diesem Zweck dient ein spezialisierter Interpreter, der als Simulator bezeichnet wird.

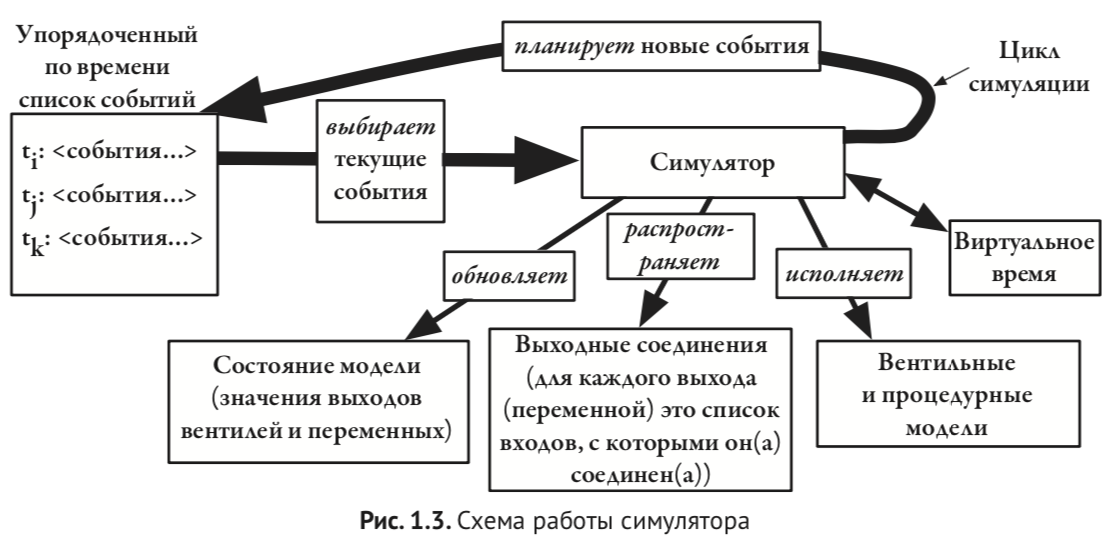

Zu Beginn des Buches zeigt Donald Thomas ein vereinfachtes Bild des Simulators, und am Ende des Buches erklärt und ergänzt er es:

Der Simulator verfügt über Ereigniswarteschlangen und simulierte Zeit:

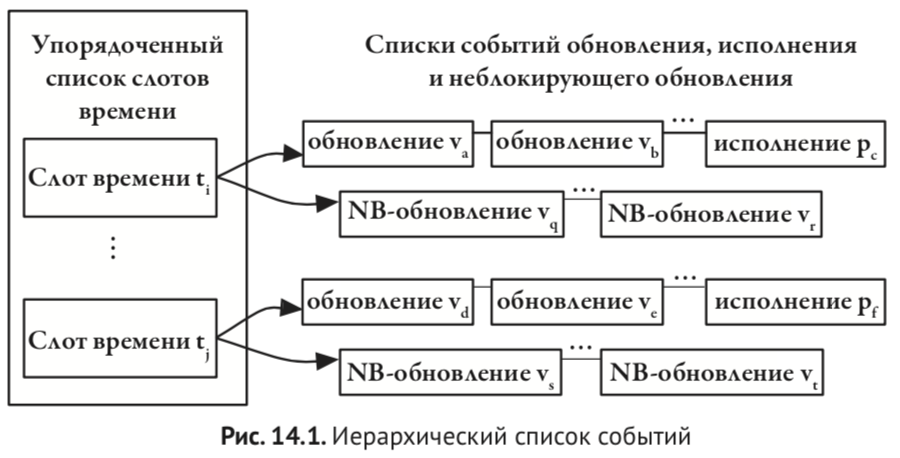

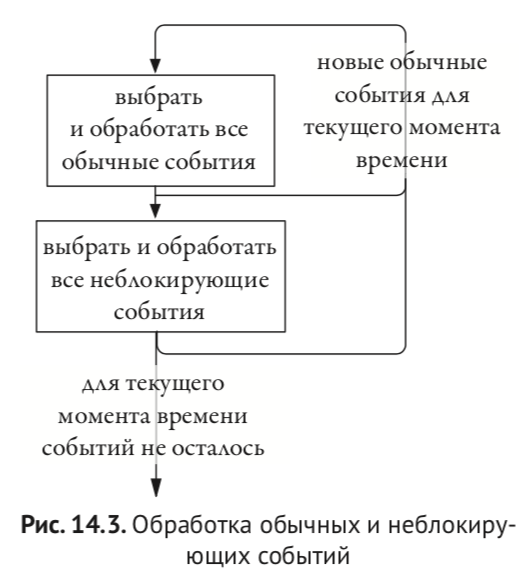

Ein Ereignis kann sowohl zum aktuellen Zeitpunkt der Simulation (im aktuellen Delta-Zyklus) als auch in der Zukunftsform zu einem neuen Ereignis führen. Im aktuellen Delta-Zyklus werden zuerst alle Ereignisse verarbeitet, die durch die sogenannten Blockierungszuweisungen erzeugt werden, und dann werden Ereignisse verarbeitet, die durch nicht blockierende Zuweisungen erzeugt werden. Dies ist notwendig für die korrekte Simulation der parallelen Semantik der Ausbreitung elektrischer Signale in Eisen:

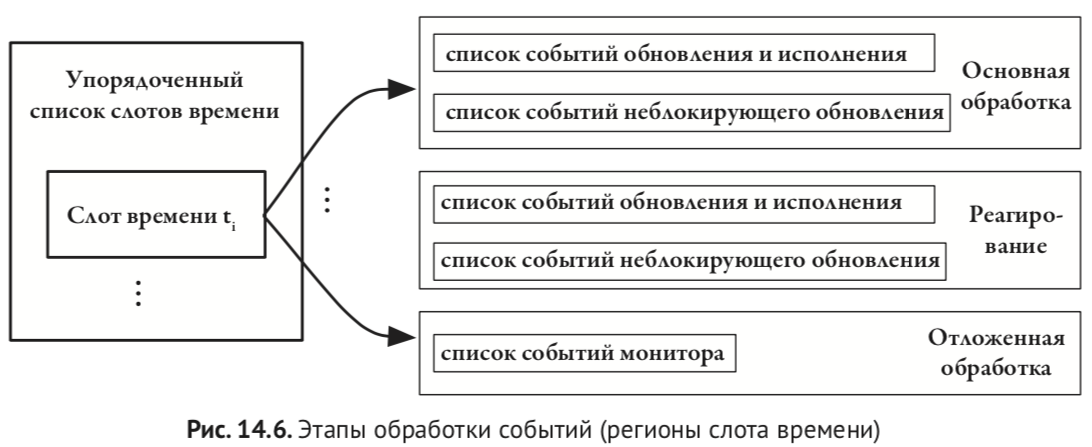

Zusätzlich zu der synthetisierten Teilmenge des Verilog gibt es auch eine nicht synthetisierte Teilmenge. Es soll die Testumgebung und die Tests beschreiben und kann nun als eine Art Programmiersprache betrachtet werden. Für Testumgebungsereignisse und -monitore werden zusätzliche Simulatorschritte eingeführt:

Eine genaue Kenntnis des Algorithmus des Simulators ist sehr nützlich, um eine Vielzahl von Fehlern zu vermeiden, die mit dem sogenannten Rennen (Race Condition) verbunden sind. Wenn ich Ingenieure interveniere, bitte ich sie immer, ein Beispiel für die Rennbedingungen in Verilog zu geben. Wenn für junge RTL Design- und Design Verification Engineers ein solches Wissen sehr wünschenswert ist, aber nicht in allen Aspekten 100% notwendig, dh Berufe, in denen Geld direkt für dieses Wissen bezahlt wird. Ich spreche von Programmierern, die in den Teams Synopsys VCS, Cadence IES und Mentor ModelSim arbeiten.

Synopsys und Cadence sind zwei Unternehmen in Kalifornien, die innerhalb von 15 Autominuten voneinander entfernt sind. Sie beschäftigen nur wenige tausend Mitarbeiter, kontrollieren aber die Entwicklung von Mikroschaltungen auf der ganzen Welt - in Intel, Apple, Samsung, Huawei, sogar in geheimen russischen Instituten, die Chips für militärische Ausrüstung herstellen.

Wenn die Genossen Putin, Rogozin und Vekselberg wirklich eine Importsubstitution in Russland einführen wollen, könnten sie die Entwicklung des russischen analogen Synopsys VCS (zur Simulation des Verilog), des Synopsys Design Compiler (zur logischen Synthese des Verilog) und des Synopsys IC Compiler (zur physischen Platzierung der Ergebnisse der logischen Synthese) finanzieren ) In Russland gibt es wahrscheinlich mehrere tausend mathematisch versierte Programmierer.

Obwohl Lizenzen für diese Softwareprodukte relativ leicht zu brechen sind, ist es schwierig, sie ohne Support zu verwenden. Wenn Huawei von Synopsys und Cadence getrennt wird, sind sie in gewisser Weise schlechter als wenn sie von Android- und sogar ARM-Kernen getrennt werden.

Ja, hier ist der verfeinerte Algorithmus am Ende von Donald Thomas 'Buch. Wenn Sie es nicht auswendig lernen, ist es sinnlos, in die Simulationsgruppen von Synopsys, Cadence, Siemens / Mentor, Xilinx einzugreifen. Dort werden Sie gebeten, es an die Tafel zu zeichnen und Vorschläge zur Optimierung eines bestimmten Falls zu machen:

Nachdem Donald Thomas die Simulation zu Beginn des Buches geklärt hat, beschreibt er die SystemVerilog-Sprache als solche. Diese Sprache entstand 2002 als Verilog-Obermenge, als Ergebnis der Zusammenführung der Sprachen Verilog-2001, Vera und Superlog und unter Hinzufügung von Ideen aus der Property Specification Language (PSL), die in SystemVerilog Assertions (SVA) umgewandelt wurden.

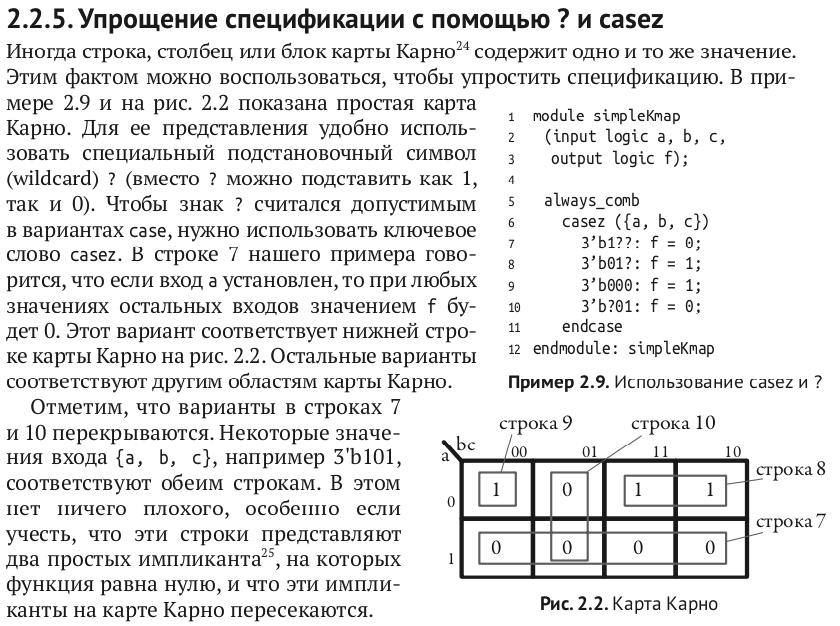

Donald Thomas glaubt, dass Sie die Grundlagen des digitalen Designs bereits irgendwo gelernt haben, und verwebt daher verschiedene bekannte Stücke wie Carnot-Karten in den Erzählstoff. Carnot-Karten wurden in den 1960er Jahren für das manuelle Design von Schaltkreisen verwendet. Danach wurde diese Methode durch die automatische Optimierung der Logik unter Verwendung des Quine-McClusky-Algorithmus und des automatischen Logikoptimierers Espresso ersetzt. Daher sind Carnot-Karten in allen Lehrbüchern der Universität zum Design digitaler Logik vorhanden, aber sie scheinen in der Luft zu hängen. Und hier fügt Donald Thomas Carnot-Karten dem Leben eines Designers auf einem Verilo des 21. Jahrhunderts hinzu:

Außerdem schreibt Donald Thomas über endliche Zustandsmaschinen und gibt 1) eine strenge mathematische Definition; 2) Diagramme; 3) Code; 4) danach beginnt es, sie zu endlichen Zustandsmaschinen mit einem Datenpfad zu erweitern - Hardwareflüsse; 5) Danach beginnen diese Flüsse mit ihm zu interagieren, sowohl nach einfachen "politisch korrekten" (siehe oben) Protokollen als auch unter Verwendung von Hardware-Warteschlangen.

Hier ist der Code für einen einfachen Automaten mit einem Datenpfad, den Thomas als erstes Beispiel nennt:

Als nächstes hat Thomas ein Kapitel über die statische Timing-Analyse. Nichts Besonderes, aber sauberer als auf vielen beliebten indischen Websites: "Wie komme ich durch das VLSI-Interview?" Und auch ausführlicher als in einigen Büchern über Veril, die mühsam an der Syntax der Sprache kauen, aber nicht wirklich zeigen, wie man sie benutzt.

Warum brauchen wir eine statische Timing-Analyse? In der realen Hardware durchläuft im Gegensatz zu der Illusion, dass der Prozessor dem Programmierer zeigt, jede Berechnung ein Zeitintervall, in dem sich der gesamte Müll auf den Drähten befindet - nicht nur klar berechnete Nullen und Einsen, sondern auch zufällige Störungen, dh Störungen und allgemein nicht digitale Werte in der verbotenen Zone. Wenn Sie beispielsweise alle Spannungen über 0,7 Volt als digitale Einheit und alle Spannungen unter 0,3 Volt als digitale Null betrachten, werden möglicherweise 0,4 Volt am Kabel angezeigt.

Am Ende gehen alle Signale in der Schaltung ihren eigenen Weg und die Situation beruhigt sich, aber dies "am Ende" sollte kleiner sein als der Zyklus des Taktsignals (Takt). Dieser Zyklus ist umgekehrt proportional zu der Frequenz, mit der die Schaltung arbeitet (Gigahertz, Megahertz).

Wenn das festgelegte Ergebnis von Berechnungen oder logischen Operationen zum Zeitpunkt der Apertur (dem Intervall um die Änderung eines solchen Signals) nicht in das D-Flip-Flop (minimales Speicherelement) fällt, wird der Zustand der Schaltung zu Müll - der Satellit oder die Drossel explodieren, das iPhone beantwortet keine Anrufe mehr. Der gesamte Ausrüstungsdesigner muss nicht weniger ironisch als logisch wissen.

Warum ist die Analyse statisch? In den 1980er Jahren war es dynamisch - Verzögerungen wurden durch Simulation geklärt. Dies erwies sich für Schaltungen mit Hunderttausenden, Millionen und Milliarden von Transistoren als unzuverlässig, und jetzt werden alle Verzögerungen statisch berechnet, basierend auf der Analyse der Signalpfade nach der Synthese.

Das Taktsignal kann auch mit einer gewissen Verzögerung in verschiedenen Teilen der Mikroschaltung ankommen, was dieser Küche eine weitere Unsicherheit hinzufügt, die beseitigt werden muss (zum Glück nicht manuell, sondern mit Hilfe von Taktsynthesebaumprogrammen und anderen Methoden):

In dem Kapitel über Flows erläutert Thomas verschiedene grundlegende Optionen, wie parallele Betriebszustandsmaschinen mit Datenpfaden Informationen austauschen können, einschließlich der Verwendung von Puffern und Warteschlangen. Wie im Entwurf / in der Schaltung selbst, auf der Ebene der Registerübertragungen, so im Verhaltensmodell oder in der Testumgebung der Schaltung. Wenn Sie Thomas lesen, ist es schön, selbst Beispiele für alle Fälle der von ihm beschriebenen Protokolle zu schreiben und zu debuggen. Tatsache ist, dass sie während eines Interviews der zweiten Ebene in Elektronikunternehmen gerne Code zu solchen Themen schreiben (eine kleine steuernde Zustandsmaschine, ein Datenfluss zwischen zwei Modulen, Pipeline-Datenpfade oder nur ein Code für eine Hardware-Warteschlange). Wenn Sie in 20 Minuten ein Beispiel für eine der von Thomas beschriebenen Kombinationen mit einem Code von 30-50 Zeilen schreiben können, machen Sie einen guten Eindruck. Schwer zu lernen - einfach im Kampf.

Die Testumgebung für Router (Abb. 8.3) mit Warteschlangen für mehrere Ports ist ein beliebtes Beispiel zur Erläuterung der Überprüfungsmethoden. Wahrscheinlich, weil einige dieser Methoden von Cisco und anderen Unternehmen erfunden wurden, die Chips für Netzwerkhardware entwickeln.

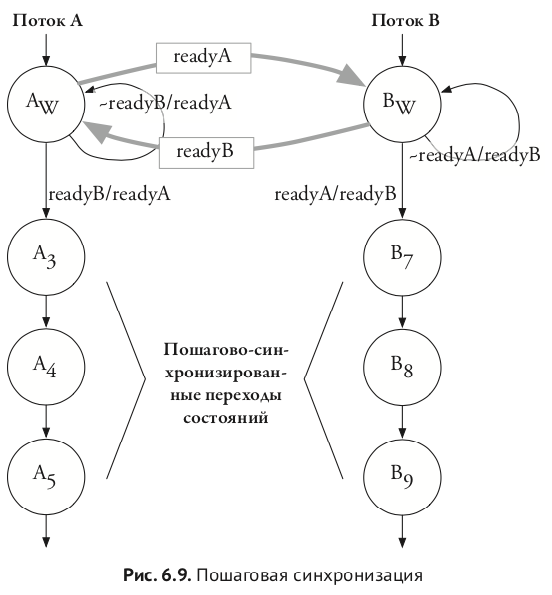

In Kapitel 6.2.2. Thomas beschreibt eine der Optionen für das Zusammenspiel von Threads - die schrittweise Synchronisation (Lock-Step). Eine der Lock-Step-Anwendungen sind hochzuverlässige Systeme, beispielsweise in der Automobilelektronik. Ein Sonderfall: Zwei Prozessoren können dasselbe Programm mit einer Verzögerung von mehreren Zyklen ausführen, und während dieser Ausführung kann eine Sonderschaltung überprüfen, ob sie dieselben Ergebnisse erzielen.

Thomas war eindeutig um Zuverlässigkeit bemüht, da er zusätzlich zum Sperrschritt die Verwendung von CRC zitiert, einem zyklisch redundanten Code zur Erkennung von Fehlern bei der Datenübertragung. Gleichzeitig erklärt Thomas, wie CRC mit LFSR, einem linearen Rückkopplungsschieberegister, berechnet wird. Sowohl das als auch ein anderer müssen in der Lage sein, einen jungen Ingenieur zu finden. Dies ist der Vorteil von Thomas 'Buch - obwohl es nicht immer tief greift, berührt es viele Themen und zeigt, wo man graben muss:

Bei der Beschreibung von CRC verweist Thomas auf ein sehr interessantes und missverstandenes Buch von Hacker's Delight in Russland:

Donald Thomas geht in seinem neuen Buch auf drei Technologien ein, die im alten Buch überhaupt nicht enthalten waren:

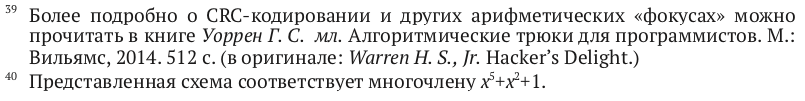

- Automatische Generierung von Pseudozufallstransaktionen mit eingeschränkten Regeln (eingeschränkte Zufallstransaktionen / Einschränkungslöser).

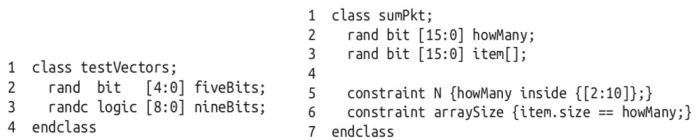

- Berücksichtigung der Abdeckung interessanter Szenarien, die während der Bombardierung eines Entwurfs durch Transaktionen mit begrenzten Zufällen entstehen, funktionale Abdeckung.

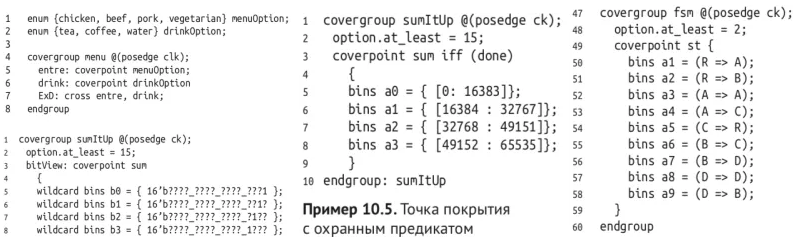

- Die Sprache der Aussagen der zeitlichen Logik (gleichzeitige Behauptungen) und ihre Verwendung sowohl in der Simulation als auch beim automatischen Nachweis von Entwurfseigenschaften unter Verwendung formaler Verifizierungsprogramme.

Diese drei Technologien sind erst im 21. Jahrhundert auf gute Weise in die Branche eingetreten, aber sie sind ziemlich fest eingetreten. Anfangs wurden sie alle verwendet, um Testumgebungen von Verifizierungsingenieuren zu erstellen. Jetzt müssen jedoch auch Designer über die Funktionsabdeckung und die Sprache für die zeitliche Bestätigung (SystemVerilog Assertions - SVA) informiert werden. Thomas hat ein bestimmtes Minimum, das Ihnen hilft, nicht in einem Telefoninterview abgeschnitten zu werden, aber für echte Arbeit müssen Sie viel mehr wissen. Darüber hinaus nicht nur die Sprache der zeitlichen Anweisungen als solche, sondern auch die Praxis des Debuggens der vom Simulator für jede Anweisung generierten parallelen Finite-State-Maschinen mit ihrer Hilfe sowie die Verwendung formaler Verifizierungsprogramme. Die auf Behauptungen basierende formale Überprüfung wurde in den letzten Jahren in Apple, AMD und anderen derartigen Unternehmen stark implementiert.

Ich habe einen Freund, der

dieses Buch über die Sprache der zeitlichen Aussagen heruntergeladen und alle Neujahrsferien studiert hat, anstatt mit Mädchen nach Hawaii zu reisen. Von hier aus können Sie verstehen, wie wichtig SystemVerilog Assertions (SVA) für Karriere und Industrie sind. Der Vollständigkeit halber muss ich erwähnen, dass er der Sohn von Auswanderern aus Taiwan ist und sie eine strengere Einstellung zu solchen Dingen haben als Russen.

So geht Thomas mit der Erzeugung pseudozufälliger Transaktionen um (eine Transaktion mit Rand-Feldern und deren Einschränkung mithilfe des Constraint-Konstrukts):

Und so geht Thomas mit der funktionalen Abdeckung um - Deckungsgruppe / Deckungspunkt / Bins, wobei Kombinationen mehrerer variabler Bedeckungen (Kreuz) berücksichtigt werden, wobei Platzhalter, Wertebereiche sowie Übergangsabdeckung in Zustandsautomaten verwendet werden:

Hier ist ein Beispiel für die einfachste zeitliche Aussage: "Wenn q bei der positiven Flanke des Taktsignals wahr ist, muss die Sequenz s2 durch den Zyklus ausgeführt werden, in dem r zuerst wahr ist und s in drei weiteren Zyklen ist."

Was ist vor und nach dem Buch „Logisches Design und Verifizierung von Systemen auf SystemVerilog“ von Donald Thomas zu lesen?

Wenn Sie in meinem Beitrag überhaupt nichts verstehen, können Sie versuchen, das Buch

„Digitale Schaltkreise und Computerarchitektur“ von David Harris und Sarah Harris zu lesen. Das Buch Harris & Harris kann von allen verstanden werden, die lesen und zählen können, vorausgesetzt, der Leser hat Motivation. Das Buch beginnt auf der Highschool-Ebene - Spannungen, Binärzahlen - und endet mit dem Entwurf eines eigenen Prozessors auf der Veril.

Spoiler: David Harris und Sarah Harris sind nicht Ehemann und Ehefrau und nicht einmal Bruder und Schwester. Sie sind nur Namensvetter, die versehentlich als Lehrer an derselben Universität angefangen haben, während der sie ein Buch geschrieben haben.

Hier links auf dem Foto ist das Mädchen Irina vom Nowosibirsk Academgorodok zu sehen, das die englische Ausgabe von Harris & Harris hält, und rechts ist ihre russische Ausgabe.

Nach dem Buch von Donald Thomas empfehle ich, Artikel von Cliff Cummings herunterzuladen. Er ist der bekannteste Veril-Trainer für Synthese und Verifikation. Während ich das Buch von Donald Thomas las, kam mir der Gedanke, dass es der Vollständigkeit halber „oft schön wäre, so und so ein Stück von Cliff Cummings einzufügen“.

Cliff nimmt je nach Dauer des Seminars (von Tag zu Woche) 1.000 bis 3.000 US-Dollar für jeden Studenten an den Seminaren ein, und Elektronikunternehmen zahlen, um die Qualität ihrer Ingenieure zu verbessern, die an Universitäten nicht gut ausgebildet sind. Selbst in Stanford lernt das leider nicht jeder - ich hatte einen Praktikanten aus Stanford, das weiß ich von ihm. Wenn Sie nach dem Lesen von Donald Thomas alle kostenlosen Artikel von Cliff Cummings herunterladen, sparen Sie all dieses Geld.Diese beiden Artikel sind erforderlich - sie fragen gerne überall im Interview nach:CDC-Entwurfs- und Verifikationstechniken (Clock Domain Crossing) unter Verwendung von Systemverilog-Simulations- und Synthesetechniken für den asynchronen FIFO-Entwurf mit asynchronen Zeigervergleichen, , FSM c FSM «case (1'b1) // synopsys parallel_case… state[STATE_N]: ...», , Sun Microsystems, :

Asynchronous & Synchronous Reset Design Techniques — Part DeuxCoding And Scripting Techniques For FSM Designs With Synthesis-Optimized, Glitch-Free OutputsSynthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 Enhancements, , 1980- . , static timing analysis, , inertial transport delays , , :

Correct Methods For Adding Delays To Verilog Behavioral Models: