Wenn Sie dachten, dass Intels "Bande" die loyalsten Befürworter

von Moores Gesetz ist , dann haben Sie wahrscheinlich noch nicht gehört, wie sich Philip Wong zu diesem Thema verbreitet. Wong, Vizepräsident für Unternehmensforschung bei Taiwan Semiconductor Manufacturing Corp (TSMC), hielt kürzlich auf einer Hot Chips-Konferenz einen Vortrag, in dem er erklärte, dass Moores Gesetz nicht nur lebendig und gut ist, sondern mit einer Reihe von technologischen Tricks immer noch nicht wahr ist weniger als drei Jahrzehnte.

"Er ist nicht tot", sagte er den Anwesenden bei Hot Chips. "Er wird nicht langsamer, er hustet nicht einmal."

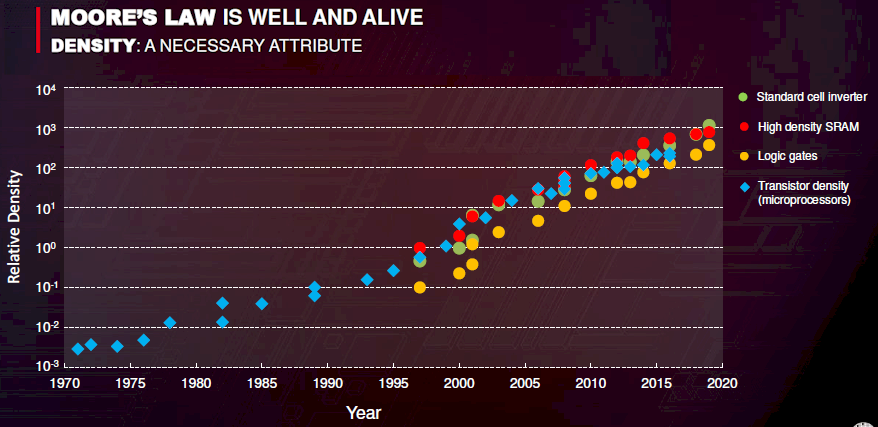

Hören Sie Wong zu, daher ist die einzige notwendige Maßnahme zur Aufrechterhaltung des Mooreschen Gesetzes die Verbesserung der Dichte. Und obwohl er zugibt, dass die Taktfrequenz ihre Obergrenze erreicht hat und damit das Ende

von Dennards Skalierungsgesetz markiert, sagt er, dass es die Dichte der Transistoren ist, die Geschwindigkeit und Energieeffizienz verbessern wird.

Moores Gesetz lebt

Moores Gesetz lebtLetztendlich spielt es keine Rolle, wie viel höhere Dichte erreicht wird. Wong glaubt, dass die Hauptsache ist, dass Unternehmen mehr Transistoren auf ein kleineres Volumen mit besserer Energieeffizienz stopfen können. Kurzfristig kann dies auf die alte, bewährte Weise erreicht werden, indem die Herstellungstechnologie von CMOS so verbessert wird, dass sich herausstellt, dass Transistoren mit einer kürzeren Gatelänge hergestellt werden.

TSMC beherrscht bereits die 7-nm-Prozesstechnologie und bewegt sich in Richtung 5-nm. Wong sagte, dass das 5-nm-Ökosystem für die Entwicklung von Prozesstechnologien bereits fertig ist und das Unternehmen bereits mit der Produktion riskanter Proben begonnen hat - das heißt, die Prozesstechnologie und die Entwicklungswerkzeuge sind fertig und es werden Arbeitssubstrate hergestellt. Auf der letzten Aktionärsversammlung gab TSMC bekannt, dass die Massenproduktion von Chips bei 5 nm im ersten Halbjahr 2020 beginnen soll. Es stellt sich heraus, dass die Pläne des Unternehmens bereits eine 3-nm-Prozesstechnologie beinhalten.

Aber all diese Technologien basieren auf

planaren [flachen] Chips, und Wong räumt ein, dass dieser Ansatz irgendwann nicht mehr skalierbar sein wird. "Wenn wir dem Weg der zweidimensionalen Zunahme folgen, haben wir bereits mehrere hundert Atome erreicht, und bald werden alle unsere Atome ausgehen", erklärte er.

Dies bedeutet jedoch nicht das Ende der Zunahme der Dichte. Er stellte fest, dass einige Innovationen in der Halbleiterindustrie auch am Ende der Dennard-Skalierung ein Aufwärtsdichtediagramm unterstützten. Insbesondere erschien die Technologie des gespannten Siliziums und des

High-k-Dielektrikums , und dann folgte FInFet (Fin Field Effector Transistor), die Technologie dreidimensionaler Strukturen. Um über 7 nm hinauszugehen, wird derzeit die DTCO-Technologie (Design Technology Co-Optimization) untersucht.

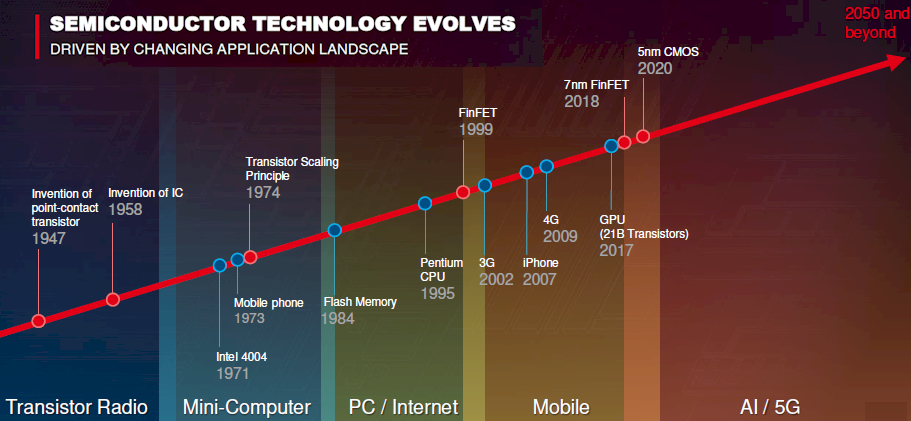

All diese Innovationen erfolgten, weil neue Computerplattformen entwickelt werden mussten, die schnellere und energieeffizientere Hardware erforderten. Diese Entwicklung brachte in den 1970er Jahren Minicomputer, in den 1980er Jahren PCs, in den 1990er Jahren das Internet und heute mobile Geräte hervor. Jede Stufe erforderte eine Erhöhung der Dichte durch verbesserte Halbleiterherstellung. Wong glaubt, dass die folgenden Anfragen von künstlicher Intelligenz und 5G kommen werden.

Entwicklung der Halbleitertechnologie

Entwicklung der HalbleitertechnologieWelche Innovationen sind erforderlich, um sicherzustellen, dass Moores Law Party nicht aufhört?

Kurzfristig werden die Gesamtberechnungsdichte und die Speicherdichte die Verwendung von Chipsätzen erhöhen, die zum Erstellen von Mehrchip-Gehäusen mit 2,5D-Strukturen verwendet werden, selbst wenn die Chips selbst nicht dichter werden. Wong sagte, dass dieser Prozess die spezifische Prozesstechnologie eines einzelnen Chiplets bereits zu einem weniger wichtigen Parameter macht als die Fähigkeit, diese Komponenten in ein einziges Paket zu integrieren.

TSMC verfügt über eine eigene Version des 2,5-D-Chassis mit Chip-on-Wafer-on-Substrate-Technologie (CoWoS) (Embedded Multi-Die Interconnect Bridge (EMIB) von Intel konkurriert mit dieser Technologie). Mit CoWoS können Sie Multi-Chip-Gehäuse erstellen, Chipsätze und einen geeigneten Speicher auf dem Interposer befestigen und diese über die vertikalen TSV-Kontakte verbinden. Die interessanteste Implementierung von CoWoS ist der Nvidia Tesla V100 GPU Accelerator, bei dem die GV100 GPU mit einem Speicher mit hoher Bandbreite (HBM) ausgestattet ist. Weitere Chipsätze werden von Intel, AMD und Xilinx integriert.

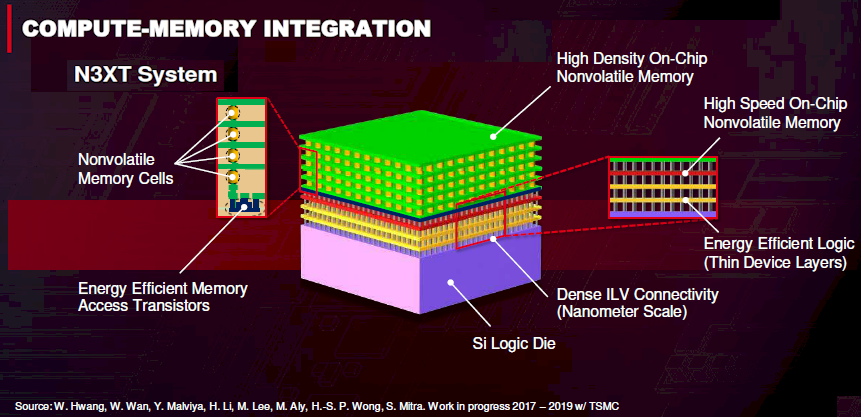

Die Möglichkeiten von 2.5D zur Erhöhung der Dichte sind jedoch nicht unbegrenzt. Eine skalierbarere Lösung erfordert wirklich dreidimensionale Transistorplatzierungstechnologien. Dafür ist laut Wong die monolithische dreidimensionale N3XT-Technologie aufgrund neuer Materialien und einer engen Integration des Speichers in die Logik am besten geeignet. N3XT, die "Nanoengineering-Technologie von Computersystemen", wird seit 2015 in der Wissenschaft diskutiert. Jetzt, da Unternehmen wie TSMC damit begonnen haben, es ernst zu nehmen, besteht eine gute Chance auf eine Kommerzialisierung.

Wong zeigte Folien mit Diagrammen, wie ein solches Gerät aussehen könnte. Es besteht aus Schichten energieeffizienter Logik (gelb), Hochgeschwindigkeitsspeicher (rot) und nichtflüchtigen Speichern mit hoher Kapazität (grün), die abwechselnd übereinander angeordnet sind. Und das alles sitzt auf einem gewöhnlichen Silizium-Logikkristall (lila).

N3XT-System

N3XT-SystemDie Hauptsache hier ist, die verschiedenen Schichten durch ILV, Inter-Layer-Via (vertikaler Zwischenschichtzugriff) zu kombinieren. Im Gegensatz zu einem TSV im Mikrometerbereich kann ILV im Nanometerbereich gebildet werden. Obwohl dies ein äußerst wichtiger Teil der N3XT-Technologie ist, konnte Wong nicht viel darüber erzählen. Es ist jedoch offensichtlich, dass TSMC eng daran arbeitet und bereits mehrere damit verbundene Patente angemeldet hat.

Bei dreidimensionalen Chips ist die Verschachtelung von Speicher und Logik sehr wichtig, da Sie so den Abstand zwischen ihnen verringern können, wodurch ein hoher Durchsatz und eine geringe Latenz der Informationsübertragung sichergestellt werden, die für Anwendungen wie AI und 5G erforderlich sind. In CMOS können Speicher und Logik nicht verschachtelt werden, da das Ätzen von Logiktransistoren eine Temperatur in der Größenordnung von 1000 Grad Celsius erfordert, die benachbarte Schichten in der Produktion zerstören würde. Es erfordert etwas, das bei Temperaturen in der Größenordnung von 400 Grad hergestellt werden kann.

Es stellt sich heraus, dass Forscher in den letzten Jahren neue Materialien untersucht haben, die für die Herstellung von Hochgeschwindigkeitstransistoren bei relativ niedrigen Temperaturen geeignet zu sein scheinen. Im Gegensatz zu den heute in der Produktion verwendeten Siliziummaterialien werden dort Monoschichten aus Dichalkogenid-Übergangsmetallen (TMD) auf Basis von Elementen wie Molybdän, Wolfram und Selen eingesetzt.

TMD-Materialien zeigen eine hohe Mobilität von Ladungsträgern - Elektronen wandern leicht durch sie hindurch - mit engen Kanälen. Was praktisch ist, sind genau solche Eigenschaften erforderlich, um Transistoren mit einer Größe von weniger als 2-3 nm zu erzeugen. Wong sagte, das TSMC-Labor teste experimentelle TMD-Substrate auf der Basis von Wolframdisulfid.

Ein weiterer Kandidat für Nanomaterialien sind Kohlenstoffnanoröhren. Wong sagte, dass ihre experimentellen Variationen gemacht wurden und ein gutes Materialverhalten als Halbleiter zeigten. Es wurden bereits funktionierende Prototypen von Logik und SRAM auf Basis von Kohlenstoffnanoröhren zusammengestellt, einschließlich der RISC-V-Variante von Forschern am MIT.

Was den Speicher betrifft, so sind laut Wong die wahrscheinlichsten Kandidaten für eine dreidimensionale Integration: SST-MRAM (magnetoresistiver Direktzugriffsspeicher mit Spinübertragungsdrehmoment, magnetoresistiver Direktzugriffsspeicher, der die Aufzeichnung des Elektronenspinimpulses zur Aufzeichnung verwendet); PCM-

Phasenwechselspeicher ;

Direktzugriffsspeicher ReRAM; Speicher basierend auf programmierbarer Metallisierung der CBRAM-Zelle;

Ferroelektrischer Direktzugriffsspeicher von FERAM. All dies ist ein nichtflüchtiger Speicher mit wahlfreiem Zugriff, für den keine Zelle gelöscht werden muss, bevor neue Informationen in sie geschrieben werden. Einige Optionen sind bereits auf dem Markt - Everspin MRAM, Samsung MRAM, Crossbar ReRAM und Intel 3D XPoint (das laut den meisten eine Variante von PCM ist).

Neue Arten von Speicher

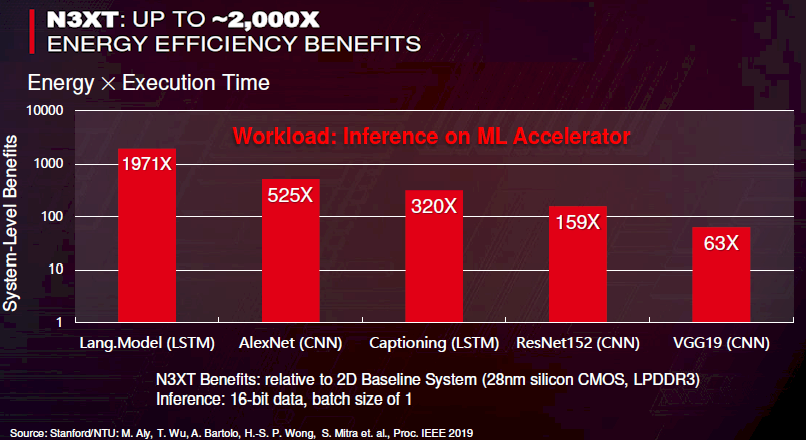

Neue Arten von SpeicherDie Forscher simulierten die Leistung von N3XT-Geräten und verglichen sie mit herkömmlichen zweidimensionalen Chips mit ungefähr der gleichen Logik und Speicherkapazität. Laut ihrer Forschung, bei der verschiedene Methoden zur Messung der Geschwindigkeit von Algorithmen für maschinelles Lernen verwendet wurden, erwiesen sich die Geräte der N3XT-Technologie als 63-1971-mal effizienter als zweidimensionale.

Der Vorteil des N3XT gegenüber zweidimensionalen Systemen

Der Vorteil des N3XT gegenüber zweidimensionalen SystemenDas klingt vielversprechend. Wong hat jedoch nicht bekannt gegeben, wie genau diese Technologien in den nächsten 30 Jahren die für Moores Gesetz erforderliche Geschwindigkeit der Technologieverbesserung aufrechterhalten können. Zum Beispiel wird der Übergang zu neuen Nanomaterialien zu einer einmaligen Erhöhung der Dichte von Transistoren in Bezug auf zweidimensionale Komponenten führen. Aber dort werden wir am Ende auf atomare Beschränkungen stoßen.

Wenn Sie die Höhe dreidimensionaler Geräte alle 18 Monate verdoppeln können, können Sie theoretisch eine Erhöhung der Dichte pro Quadratfläche erzielen. Für mobile und eingebettete Geräte wird dieser Ansatz natürlich schnell zu umständlich, und die Chips für Computer in Rechenzentren nach sieben bis acht Generationen werden in einer 4-Meter-Decke ruhen.

Damit alles über mehrere Jahrzehnte weiter funktioniert und die Dichte weiterhin in die Kurve von Moores Gesetz passt, müssen andere technische Innovationen entwickelt werden, die Wong nicht erwähnt. Wenn Sie jedoch Chips wie TSMC herstellen, müssen Sie akzeptieren, dass Forscher Ihnen ständig neue Kandidaten für Technologien geben, für deren Markteintritt nur Anfragen von neuen, anspruchsvolleren Aufgaben erforderlich sind. Und wenn Sie sich an die Geschichte erinnern, werden solche Aufgaben sicherlich auftauchen.