Einführung

Einmal musste ich einen kleinen Block CAM (assoziativen Speicher) implementieren. Nachdem ich gelesen hatte, wie Xilinx dies auf BRAM (statische Speicherblöcke) oder auf SRL16 (16-Bit-Schieberegister) macht, war ich ein wenig traurig, da ihre Implementierungen ziemlich viel Platz in Anspruch nahmen. Ich beschloss, es selbst zu versuchen. Die erste Option war die Implementierung der Stirn. Mit Blick auf die Zukunft kam es mir fast sofort in den Sinn und die Zielfrequenz für das Design betrug nur 125 MHz.

Architektur

Betrachten Sie zunächst die Erklärung des Problems. Wir brauchen also eine kleine CAM mit einer Wortbreite von 8-64 Bit und einer Tiefe von 16-1024 Wörtern. Ich brauchte eine binäre Suche in CAM, aber später stellte sich heraus, dass das Erstellen von TCAM (ternärer assoziativer Speicher) ressourcenschonend ist und das Timing geringfügig beeinflusst. Die untere Frequenzgrenze liegt bei der Kintex7- Familie bei 125 MHz. Fangen wir an! Unser CAM besteht aus diesen Zeilen, von denen jede einer Adresse entspricht und ein Wort speichert:

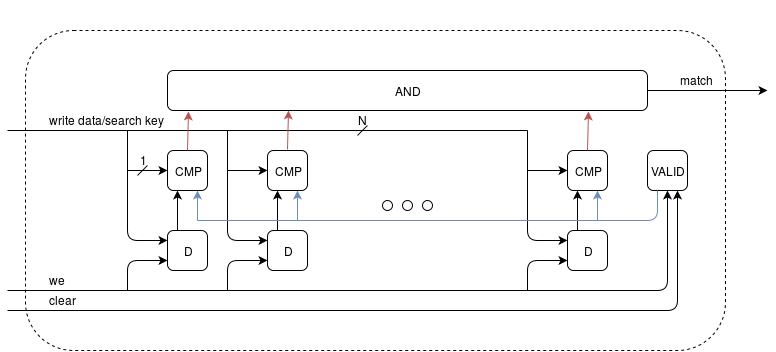

Abbildung 1. Die Struktur einer CAM-Linie

In Fig. 1 ist D ein regulärer D-Trigger zum Speichern von Daten, wobei die Anzahl dieser Trigger in der Zeile der Breite des Eingabedatenworts in CAM entspricht. GÜLTIG - D-Trigger, der '1' speichert, wenn die Daten in der Zeile relevant sind. CMP ist ein Komparator, der den Wert des entsprechenden Suchschlüsselbusbits vergleicht, wenn VALID = '1' ist. Daten schreiben - Datenbus schreiben , bitweise mit dem entsprechenden D ( N - CAM Wortbreite) verbunden, wir - Schreibflag, Clear - Reset VALID (Ungültigmachung der Datenleitung). UND - logisches UND von N Ausgängen der Komparatoren, Match - Flag wird zu '1', wenn die Suche in dieser Zeile erfolgreich ist.

Wir haben also eine Zeile, in der wir suchen können. Kombinieren Sie sie jetzt:

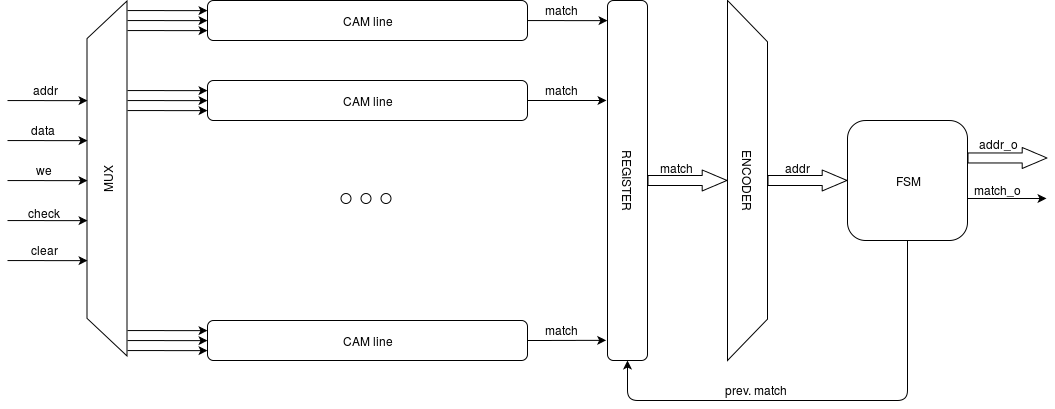

Abbildung 2. CAM-Struktur

In Fig. 2 ist CAM_line die CAM-Leitung selbst aus Fig. 1, MUX ist der Eingangsadressenmultiplexer, MATCH REGISTER ist ein Register, das Übereinstimmungsflagwerte speichert, ENCODER ist ein Decoder, der den Übereinstimmungsbus in die niedrigste gefundene Übereinstimmungsadresse konvertiert. FSM ist eine steuernde Finite-State-Maschine . match entfernt aus MATCH REGISTER das Bit, das der gesendeten Adresse entspricht, sodass ENCODER zur nächsten gefundenen Adresse wechselt. Die Schnittstelle unseres CAM lautet wie folgt:

Tabelle 1. CAM-Schnittstelle

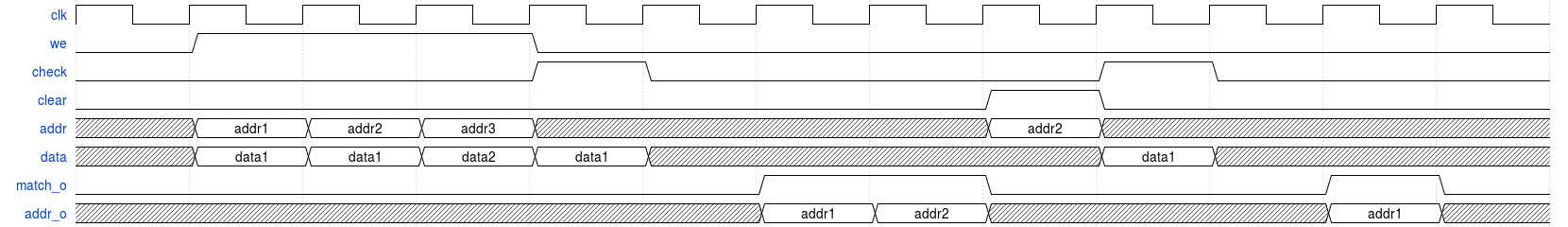

Unten in Fig. 3 ist ein Zeitdiagramm des Betriebs dieser Schnittstelle dargestellt, das zuerst die Aufzeichnung von drei Wörtern in CAM, dann eine erfolgreiche Suche, Löschung und erneute Suche zeigt:

Abbildung 3. Zeitdiagramm der Schnittstelle zum CAM

Wir haben also eine Beschreibung von CAM. Fahren wir mit der Synthese fort.

Synthese

Wir werden in Xilinx ISE synthetisieren, um die Ergebnisse mit denen in XAPP1151 zu vergleichen.

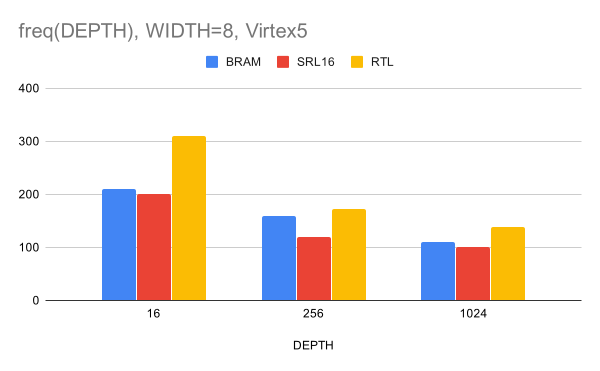

Abbildung 4. Frequenzabhängigkeit nach XST (Synthesizer als Teil von ISE) von der CAM-Tiefe für die 8-Bit-Datenbusbreite

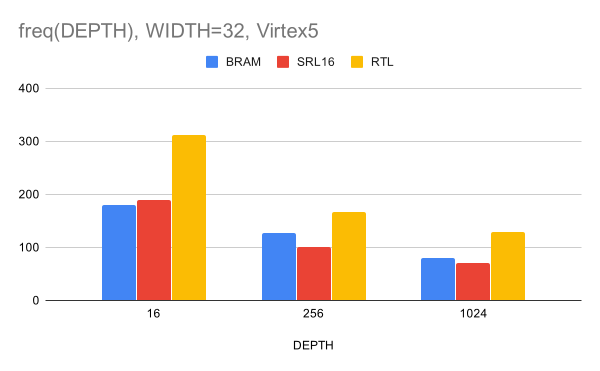

Abbildung 5. Frequenz nach XST im Verhältnis zur CAM-Tiefe für die 32-Bit-Datenbusbreite

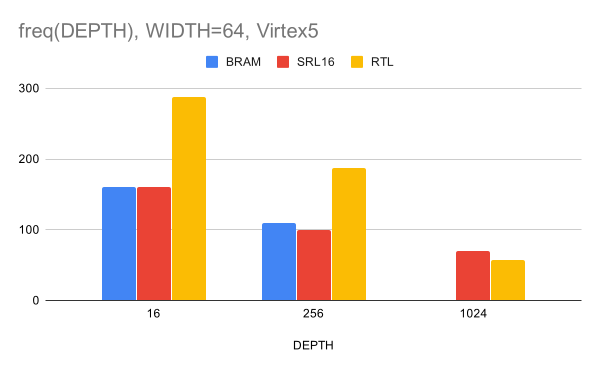

Abbildung 6. Frequenz nach XST im Verhältnis zur CAM-Tiefe für die 64-Bit-Datenbusbreite

In 6 gibt es keine Daten für Virtex5 , da CAM dieser Größe nicht in das vorhandene BRAM passte. Wir stellen außerdem fest, dass unser Ergebnis bei einer Breite von 64 Bit und einer Tiefe von 1024 etwas schlechter war als das der Implementierung auf SRL16. Fahren wir nun mit der Vivado-Synthese für den XC7K325T fort . Die Ergebnisse sind wie folgt:

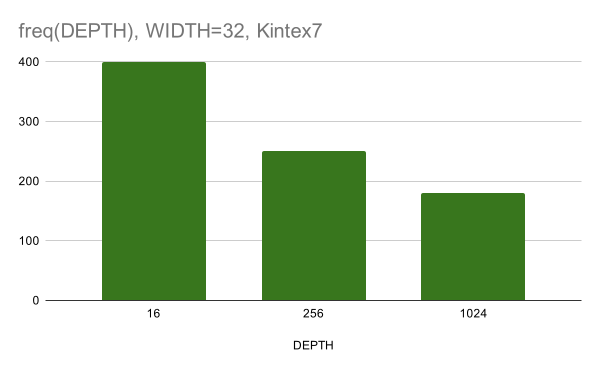

Abbildung 7. Frequenzabhängigkeit nach PnR (Platzierung von Blöcken auf dem Chip und Signalverfolgung) von der CAM-Tiefe für eine 32-Bit-Datenbusbreite

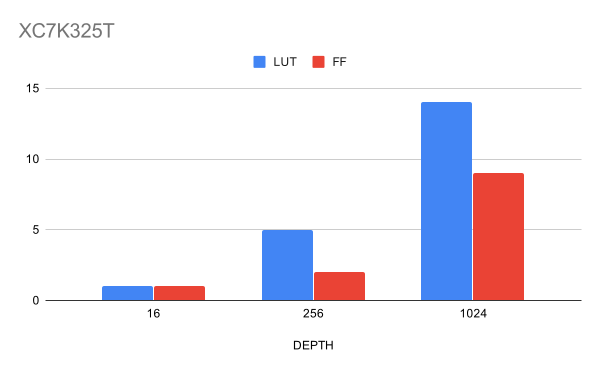

Abbildung 8. Verwendung von Ressourcen für verschiedene CAM-Tiefen für eine Datenbreite von 32 Bit in%

Es ist wichtig zu beachten, dass die Ergebnisse auf Vivado nach PnR erhalten wurden, was bedeutet, dass das Design keine Schwierigkeiten bei der Rückverfolgung hat.

TCAM

Wie oben erwähnt, war es kein besonderes Problem, mit diesem Ansatz von CAM TCAM zu kommen. Es reicht aus, einen Maskierungsbus für die Datenbits hinzuzufügen und ihn Stück für Stück an die Komparatoren zu verteilen, damit sie beim Vergleich der Daten mit dem Schlüssel deren Wert berücksichtigen. Eine solche Änderung führte nicht zu einem Frequenzabfall oder einer ernsthaften Erhöhung des Ressourcenverbrauchs, sodass wir TCAM kostenlos erhielten.

Schlussfolgerungen

So konnten wir die Aufgabe erledigen. Das resultierende Design ermöglicht es der 7. Xilinx-FPGA-Familie, ausreichend große CAM mit einer Frequenz über dem Ziel von 125 MHz zu empfangen. Das Ergebnis des Vergleichs mit XAPP1151 stellte sich für mich als unerwartet heraus. Ich ging davon aus, dass die Implementierung auf BRAM, obwohl sie in Bezug auf Ressourcen sehr teuer ist, die frontale Implementierung in der Häufigkeit überholen wird. Feiern Sie den Sieg jedoch nicht so früh, dieses Dokument beschreibt den Xilinx CAM IP-Kern, mit dem beispielsweise CAM mit einer Tiefe von 32K-Zellen und einer Frequenz von 155 MHz basierend auf BRAM erhalten werden kann. Dieses Ergebnis kann wahrscheinlich in der im Artikel vorgeschlagenen Version erzielt werden, entweder durch Hinzufügen der Stufen der Pipeline oder durch Sammeln großer CAM von kleinen, aber ich kann nicht sofort vorhersagen, ob es in den Chip passt. In Zukunft werde ich versuchen, etwas Ähnliches auf BRAM zu implementieren, aber vorerst vielen Dank für Ihre Aufmerksamkeit.