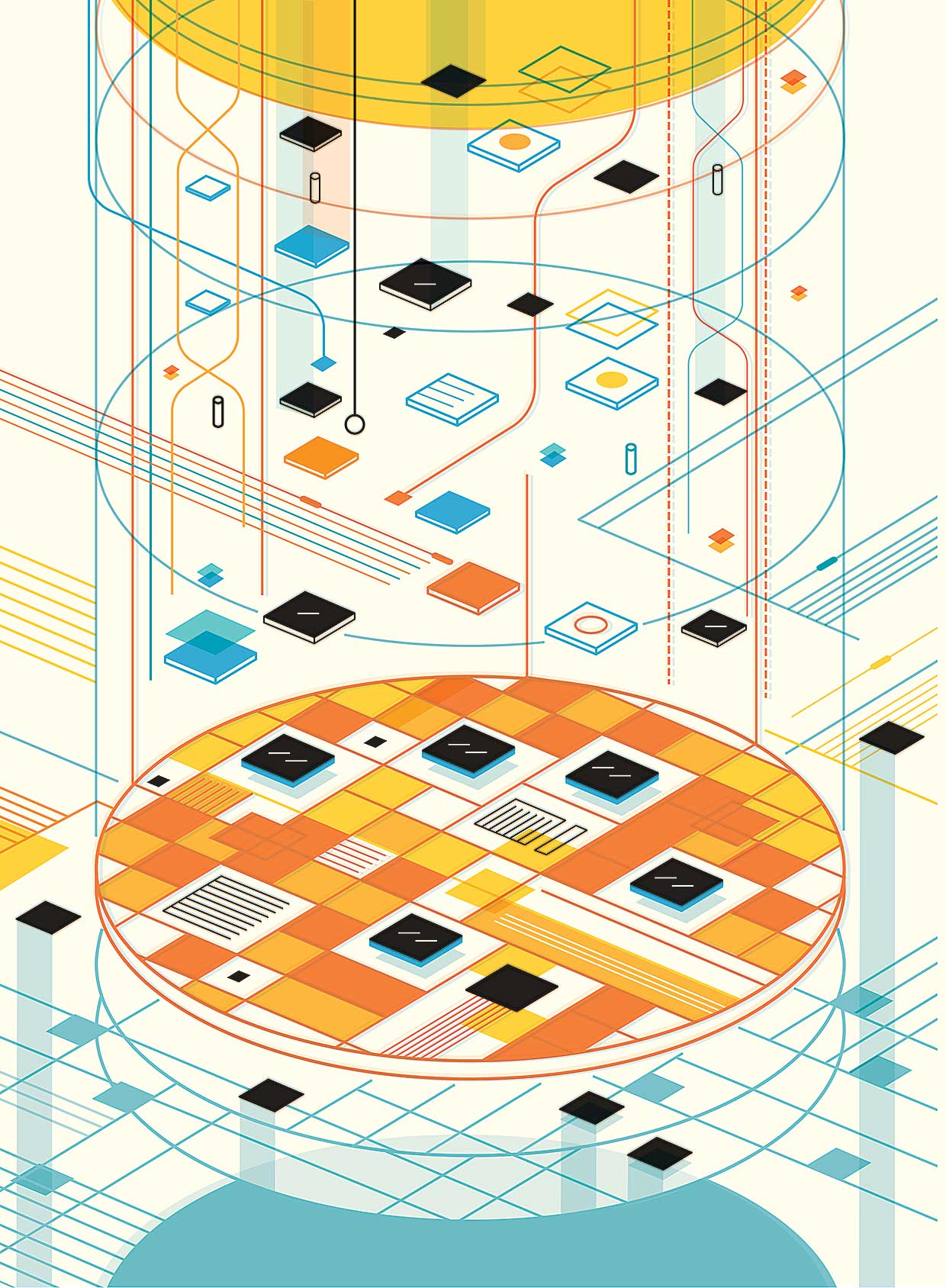

Wenn Sie nackte Chipsätze in einem Siliziumnetzwerk platzieren, können Sie kleinere Computer und mehr Rechenleistung herstellen

Die Notwendigkeit, bestimmte Geräte immer weniger und andere immer mehr herzustellen, war lange Zeit der Hauptmotivator für Innovationen in der Elektronik. Die erste Option zeigt sich von Laptops über Smartphones bis hin zu Smartwatches, Smart Headphones und anderer „unsichtbarer“ Elektronik. Die zweite Option bestimmt die Konfiguration moderner Rechenzentren - Megawatt-Monster, die weltweit speziell für sie gebaute Speicher füllen. Interessanterweise wird der Fortschritt in beiden Fällen durch dieselbe Technologie begrenzt - nur aus verschiedenen Gründen.

Wir argumentieren, dass die Leiterplatte der Schuldige ist. Unsere Lösung besteht darin, es vollständig loszuwerden.

Unsere Studie zeigt, dass Leiterplatten durch dasselbe Material ersetzt werden können, aus dem die darauf gelöteten Chips bestehen - also Silizium. Ein solcher Ansatz würde es ermöglichen, sowohl Systeme mit kleinerer Größe und geringerem Gewicht, die für tragbare Elektronik und andere Geräte mit begrenzter Größe geeignet sind, als auch unglaublich leistungsstarke Hochgeschwindigkeitscomputer zu schaffen, die die Rechenleistung von einem Dutzend Servern in ein Siliziumsubstrat von der Größe eines Speisetellers schieben können.

Eine ähnliche All-Silizium-Technologie, die wir als Silizium-Verbindungsnetzwerk bezeichnen, ermöglicht es Ihnen, nackte Chips direkt mit einzelnen Siliziumfragmenten zu verbinden. Im Gegensatz zu Spuren auf Leiterplatten hat der Kontakt zwischen den Chips auf unserem Substrat die gleiche Größe wie die Spuren in den Chips. In dieser Hinsicht können viel mehr Verbindungen in das Substrat gelegt werden, und alle von ihnen sind in der Lage, Daten mit weniger Stromverbrauch schneller zu übertragen.

Das Silizium-Verbindungsgewebe (Si-IF) bietet einen weiteren zusätzlichen Vorteil. Dies ist eine großartige Möglichkeit, die relativ großen, komplexen und unbequemen Single-Chip-Produktionssysteme (System-on-a-Chip, SoC) aufzubrechen, auf denen heute alles ruht, vom Smartphone bis zum Supercomputer. Anstelle von SoC könnten Systementwickler Konglomerate kleinerer, einfacher im Design und bei der Herstellung von Chiplets verwenden, die auf Si-IF eng miteinander verbunden sind. Eine solche Revolution der Chipsätze ist bereits im Gange - AMD, Intel, Nvidia und andere Unternehmen bieten Chipsätze an, die in fortschrittlichen Gehäusen montiert sind. Ein Interconnect-Silizium-Netzwerk erweitert diese Idee, indem es den Systemfall aufbricht und es Ihnen ermöglicht, den gesamten Computer darin einzubeziehen.

Überlegen Sie, was mit einem typischen SoC passiert, um den vollen Nutzen der Eliminierung einer Leiterplatte zu verstehen. Aufgrund der Entwicklung der Elektronik nach dem Moore'schen Gesetz können Sie auf einem Quadratzentimeter Silizium fast alles verpacken, was ein Smartphone benötigt, um zu funktionieren. Leider befindet sich dieses Stück Silizium aus vielen Gründen, die mit den Merkmalen der Leiterplatte zusammenhängen, in einem Kunststoffgehäuse, das manchmal 20-mal so groß wie der Chip selbst ist.

Der Größenunterschied zwischen dem Chip und dem Gehäuse verursacht mindestens zwei Probleme. Erstens ist das Gewicht und Volumen eines gepackten Chips größer als das eines Siliziumstücks. Dies ist natürlich ein Problem für alle Geräte, die klein, dünn und leicht sein müssen. Zweitens, wenn ein fertiges Produkt mehrere Chips erfordert, die Daten miteinander austauschen (und die meisten Systeme haben einen), erhöht sich die Entfernung, die das Signal zurücklegen muss, um mehr als das Zehnfache. Dies ist ein Engpass für Geschwindigkeit und Stromverbrauch, insbesondere beim Austausch großer Datenmengen. Dies ist wahrscheinlich die größte Herausforderung bei der Implementierung datenabhängiger Anwendungen - Grafik, maschinelles Lernen und Suche. Schlimmer noch, Chips sind in solchen Fällen schwerer zu kühlen. Die Wärmeableitung ist seit mehreren Jahrzehnten ein begrenzender Faktor in der Elektronik.

Aber wenn diese Fälle so problematisch sind, warum nicht sie loswerden? Wegen der Leiterplatte.

Die Aufgabe der Leiterplatte besteht darin, Chips, passive Komponenten und andere Geräte zu einem funktionierenden System zu kombinieren. Diese Technologie ist jedoch nicht perfekt. Leiterplatten sind schwer perfekt zu machen - sie biegen sich oft. Chipgehäuse werden normalerweise mit Lottröpfchen an die Platine angeschlossen, die während der Produktion schmelzen und wieder löten. Einschränkungen der Löttechnologie zusammen mit der Oberflächenkrümmung führen dazu, dass die Tröpfchen nicht näher als 0,5 mm zueinander liegen. Mit anderen Worten, es können nicht mehr als 400 Kontakte pro Quadratzentimeter platziert werden. Für viele Anwendungen ist dies zu wenig für die Energie- und Signalübertragung zum und vom Chip. Auf einer kleinen Oberfläche, die vom Kristall des Intel Atom-Prozessors eingenommen wird, ist beispielsweise genügend Platz für Hunderte von Kontakten mit einer Größe von 0,5 mm vorhanden, und es werden 300 benötigt. Entwickler verwenden Fälle für Kristalle, damit die Mathematik mit der Anzahl der Kontakte pro Flächeneinheit konvergiert. Das Gehäuse nimmt winzige Kontakte eines Siliziumchips auf - von 1 bis 50 Mikrometer Breite - und erweitert sie auf die Platinenskala von 500 Mikrometern.

In jüngster Zeit hat die Halbleiterindustrie versucht, die mit Leiterplatten verbundenen Probleme durch die Entwicklung fortschrittlicher Gehäuse mit Silizium-Interposer-Technologie zu begrenzen. Interposer ist eine dünne Siliziumschicht, auf der eine kleine Anzahl von blanken Siliziumchips angebracht ist, die über eine große Anzahl von Kontakten miteinander verbunden sind. Gleichzeitig muss der Interposer mit seinen Chips immer noch im Gehäuse versteckt und auf der Leiterplatte platziert werden, sodass diese Option die Komplexität erhöht, ohne die verbleibenden Probleme zu lösen. Darüber hinaus sind Interposer notwendigerweise dünn, zerbrechlich und von begrenzter Größe - was bedeutet, dass es schwierig ist, große Systeme auf ihnen zu erstellen.

Wir glauben, dass die beste Option darin besteht, Gehäuse und Leiterplatten vollständig zu entfernen, indem die Chips auf einem relativ dicken (von 500 Mikrometer bis 1 mm) Siliziumsubstrat angebracht werden. Prozessoren, Speicherkristalle, HF-Chipsätze, Spannungsregelungsmodule und sogar passive Komponenten wie Induktivitäten und Kondensatoren können direkt an Silizium angeschlossen werden. Verglichen mit dem üblichen Material von Leiterplatten - Glasfaser- und Epoxidzusammensetzung FR-4 - ist das Siliziumsubstrat fest und kann auf eine nahezu perfekte Ebene poliert werden, sodass die Krümmung keine Angst davor hat. Da sich die Chips und das Substrat ausdehnen und zusammenziehen, wenn sich die Temperatur um den gleichen Betrag ändert, benötigen Sie keine große und flexible Verbindung zwischen dem Chip und dem Substrat mehr, z. B. Löten.

Lottropfen können durch im Substrat eingebettete Mikrometer-Kupferstifte ersetzt werden. Durch thermische Kompression - in der Tat durch präzise Anwendung von Heizung und Druck - können die Kupfer-Eingangs- / Ausgangskontakte der Chips direkt mit den Stiften verbunden werden. Durch eine gründliche Optimierung der Thermokompressionsverbindung können wir viel zuverlässigere Kontakte als durch Löten erhalten und gleichzeitig weniger verschiedene Materialien verwenden.

Durch die Beseitigung von Leiterplatten und deren Schwächen können E / A-Anschlüsse in einem Abstand von nur 10 Mikrometern anstelle von 500 Mikrometern angeordnet werden. Infolgedessen ist es möglich, 2500-mal mehr Ports auf einem Siliziumchip zu platzieren, ohne dass ein Gehäuse verwendet werden muss.

Noch besser ist, dass der Standardprozess zur Herstellung von Halbleitern neu konfiguriert werden kann, um mehrstufige Si-IF-Schaltpläne herzustellen. Ihre Spuren können viel dünner gemacht werden als auf Leiterplatten. Sie können nur um 2 Mikrometer und nicht um 500 Mikrometer voneinander getrennt sein, wie dies bei Leiterplatten der Fall ist. Mit dieser Technologie können Sie Chips sogar in einem Abstand von 100 Mikrometern voneinander platzieren, im Gegensatz zu Leiterplatten, bei denen sie mehr als 1 mm betragen sollten. Dadurch spart das Si-IF-System Platz, Energie und Signallaufzeit.

Darüber hinaus leitet Silizium im Gegensatz zu Leiterplatten und Materialien für IC-Gehäuse Wärme ziemlich gut. Auf beiden Seiten von Si-IF können Heizkörper montiert werden, um noch mehr Wärme abzuleiten - nach unseren Schätzungen 70% mehr. Und je mehr Wärme abgeführt wird, desto schneller können die Prozessoren arbeiten.

Obwohl Silizium eine gute Zugfestigkeit und Zähigkeit aufweist, ist es leicht spröde. Glücklicherweise hat die Halbleiterindustrie Methoden für die Arbeit mit großen Siliziumsubstraten entwickelt, um Risse über mehrere Jahrzehnte hinweg zu verhindern. Und nach all den notwendigen Si-IF-Produktionsverfahren erwarten wir, dass sie die meisten Zuverlässigkeitstests bestehen, einschließlich Schlagprüfung, zyklischer Erwärmung und Umwelteinwirkung.

Es ist nicht zu übersehen, dass kristallines Silizium teurer ist als FR-4. Obwohl die Kosten von vielen Faktoren abhängen, kann der Preis pro Quadratmillimeter einer 8-lagigen Leiterplatte zehnmal niedriger sein als der einer 4-lagigen Si-IF. Unsere Analyse zeigt jedoch, dass, wenn Sie die Kosten für das Platzieren der Chips in den Gehäusen und die komplexe Herstellung der Platinen abziehen und die Platzersparnis mithilfe der Si-IF-Technologie berücksichtigen, der Kostenunterschied unbedeutend ist und in einigen Fällen Si-IF sogar rentabler sein kann.

Interkomponentiges Siliziumnetzwerk im Vergleich zu Leiterplatte und Chips im Gehäuse. Am unteren Rand des Diagramms befindet sich eine ungefähre Skala zum Verständnis des Größenunterschieds.

Interkomponentiges Siliziumnetzwerk im Vergleich zu Leiterplatte und Chips im Gehäuse. Am unteren Rand des Diagramms befindet sich eine ungefähre Skala zum Verständnis des Größenunterschieds.Schauen wir uns einige Beispiele für die Vorteile der Verwendung von Si-IF in einem Computersystem an. In einer Studie zu Serverdesigns haben wir festgestellt, dass die Verwendung von Prozessoren ohne Gehäuse mit Si-IF die Leistung herkömmlicher Prozessoren aufgrund verbesserter Konnektivität und erhöhter Energiedissipation verdoppeln kann. Zusätzlich kann die Größe der Siliziumplatte (in Abwesenheit eines besseren Ausdrucks) von 1000 cm

2 auf 400 cm

2 reduziert werden. Ein derart schwerwiegender Rückgang wird sich erheblich auf das Volumen der Rechenzentrumsgebäude und die Größe der Kühlinfrastruktur auswirken. Am anderen Ende der Skala haben wir ein kleines System für das „Internet der Dinge“ untersucht, das auf dem Arm-Mikrocontroller basiert. In diesem Fall reduziert die Verwendung von Si-IF nicht nur die Plattengröße um 70%, sondern auch das Gewicht von 20 auf 8 Gramm.

Si-IF reduziert nicht nur vorhandene Systeme und steigert die Produktivität, sondern ermöglicht Entwicklern auch die Erstellung von Computern, die sonst nicht zu konstruieren wären - oder die sehr unpraktisch wären.

In einem typischen leistungsstarken Server kostet die Karte 2-4 Prozessoren. Einige Projekte mit hoher Rechenlast erfordern mehrere Server. Beim Verschieben von Daten zwischen verschiedenen Prozessoren und Karten treten Verzögerungen und Engpässe auf. Was aber, wenn alle Prozessoren auf einem einzigen Siliziumsubstrat platziert wären? Sie könnten so eng integriert werden, dass das gesamte System als ein großer Prozessor arbeiten würde.

Dieses Konzept wurde erstmals von Gene Amdahl in seiner Firma Trilogy Systems vorgeschlagen. Trilogy war jedoch nicht erfolgreich, da der Produktionsprozess keine ausreichende Qualität für das Arbeitssystem erbrachte. Bei der Herstellung eines Chips besteht immer die Möglichkeit von Defekten, und mit zunehmender Fläche steigt die Wahrscheinlichkeit einer Heirat exponentiell an. Wenn die Größe des Chips mit einem Teller vergleichbar ist, ist fast garantiert, dass das gesamte System der Ehe zerstört wird.

Wenn Sie jedoch über ein Silizium-Verbindungsnetz verfügen, können Sie mit den Chipsätzen beginnen, die wir bereits fehlerfrei herstellen können, und diese dann zu einem einzigen System kombinieren. Unser Forscherteam von der University of California in Los Angeles und der University of Illinois in Urbana-Campain hat ein solches System mit einem Substrat entwickelt, das 40 GPUs enthält. In Simulationen beschleunigte es die Berechnungen um mehr als das Fünffache und verbrauchte 80% weniger Energie als das entsprechende System von 40 GPUs, die mit fortschrittlichen Multi-Chip-Gehäusen und Leiterplatten erstellt wurden.

Die Ergebnisse waren überzeugend, obwohl die Aufgabe nicht einfach war. Wir mussten viele Einschränkungen berücksichtigen, insbesondere: die maximale Wärmemenge, die dem Substrat entzogen wird; wie die GPU Daten so schnell wie möglich austauschen kann; wie man Strom über den gesamten Bereich des Substrats liefert.

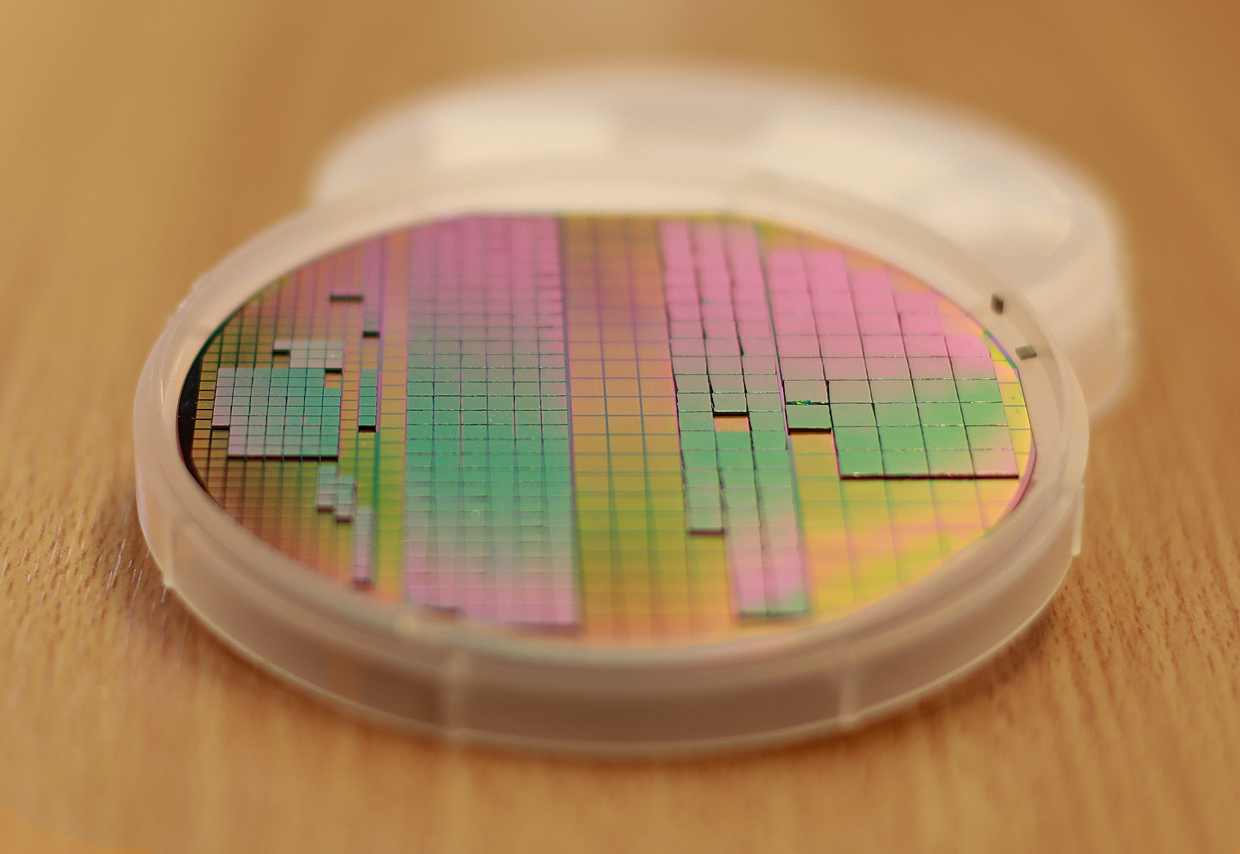

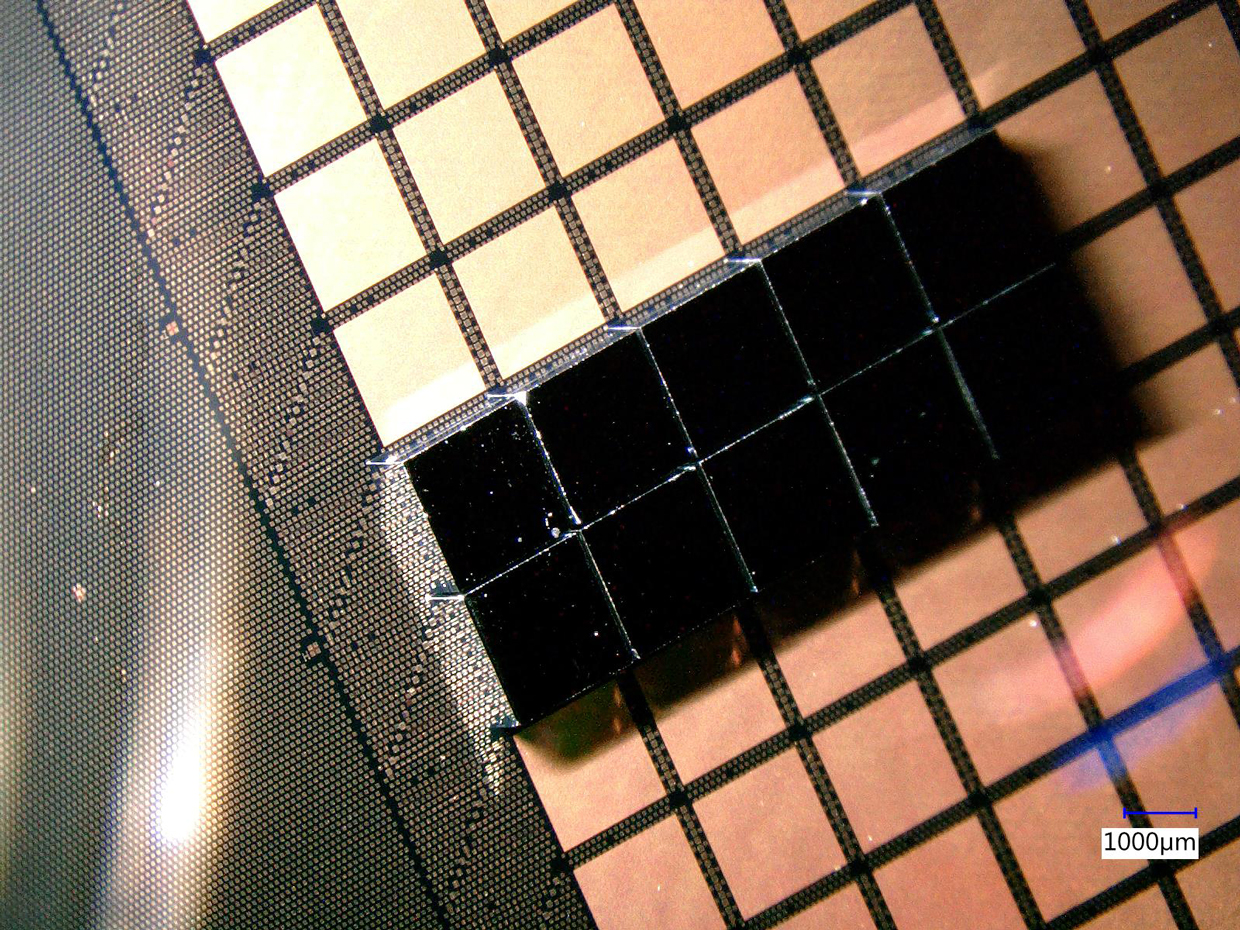

Dilets oder Chipsätze, integriert in ein miteinander verbundenes Siliziumnetzwerk, 100 mm Substrat. Dilets können im Gegensatz zu Chips auf einer Leiterplatte in einem Abstand von 100 Mikrometern voneinander platziert werden

Dilets oder Chipsätze, integriert in ein miteinander verbundenes Siliziumnetzwerk, 100 mm Substrat. Dilets können im Gegensatz zu Chips auf einer Leiterplatte in einem Abstand von 100 Mikrometern voneinander platziert werdenDie Hauptbeschränkung war die Ernährung. Bei einer Standard-Chipbetriebsspannung von 1 V müssten die dünnen Spuren des Substrats 2 kW verbrauchen. Stattdessen haben wir die Spannung auf 12 V erhöht und auf diese Weise Strom und Leistung reduziert. Zu diesem Zweck mussten die Spannungsregler und Kondensatoren im gesamten Substrat verteilt werden, und sie nahmen den Platz ein, der ansonsten zusätzlichen GPUs zugewiesen werden könnte. Inspiriert von den ersten Ergebnissen bauen wir jetzt einen Prototyp eines Computersystems zusammen, das wir bis Ende 2020 fertigstellen möchten.

Ein Interconnect-Silizium-Netzwerk kann eine Rolle in einem wichtigen Trend in der Computerindustrie spielen: Die Aufteilung von SoC in integrierte Sätze von Daylets [Dielet aus Chip, Kristall und –let, Schrumpfbox / ca. transl.] oder Chiplets (wir nennen sie lieber Daylets, da dies ihre Essenz als bloße Siliziumkristalle, ihre geringe Größe und möglicherweise unvollständige Funktionalität ohne andere Si-IF-Daylets hervorhebt). In den letzten zwei Jahrzehnten hat der Wunsch, die Leistung zu steigern und die Kosten zu senken, die Entwickler überzeugt, Chipsätze durch noch größere integrierte SoCs zu ersetzen. Und trotz ihrer Vorteile hat SoC eine ausreichende Anzahl von Nachteilen.

Erstens ist SoC ein großer Chip, und wie bereits erwähnt, ist es ziemlich schwierig, akzeptable Indikatoren für den Prozentsatz der Ausschussprodukte bei der Herstellung großer Chips zu erhalten, insbesondere in fortgeschrittenen Halbleiterindustrien (denken Sie daran, dass der Prozentsatz der Ausschussprodukte mit zunehmender Chipfläche exponentiell zunimmt). Ein weiterer Nachteil von SoC sind die hohen Kosten für das Entwerfen und Starten der Produktion. In den USA kann eine fotolithografische Maske beispielsweise ab 2 Millionen US-Dollar kosten, sodass die SoC-Option für die meisten Systeme nicht verfügbar ist. Darüber hinaus erfordert jede geringfügige Änderung des Schemas oder die Aktualisierung des Produktionsprozesses eine erhebliche Verarbeitung des gesamten SoC. Schließlich versucht der SoC-Ansatz, alle Subsysteme in einen Produktionsprozess einzubauen, selbst wenn einige dieser Subsysteme in einem anderen Prozess besser ausgeführt werden könnten. Infolgedessen erreicht nichts in SoC die höchstmögliche Effizienz oder Geschwindigkeit.

Die Integration auf Si-IF ohne die Beteiligung von Gehäusen vermeidet all diese Probleme, behält jedoch die geringe Größe und Geschwindigkeit von SoC bei und bietet Entwicklungsvorteile und -kosten. Es zerlegt SoC in seine Bestandteile und erstellt ein System auf einem Substrat, System-on-Si-IF (SoIF).

Ein solches System besteht aus unabhängig hergestellten Daylets, die über Si-IF verbunden sind. Der Mindestabstand zwischen Diletten (einige zehn Mikrometer) ist vergleichbar mit dem Abstand zwischen zwei SoC-Funktionsblöcken. Die Verdrahtung auf Si-IF ist die gleiche wie auf der oberen SoC-Ebene, daher ist die Dichte der Verbindungen vergleichbar.

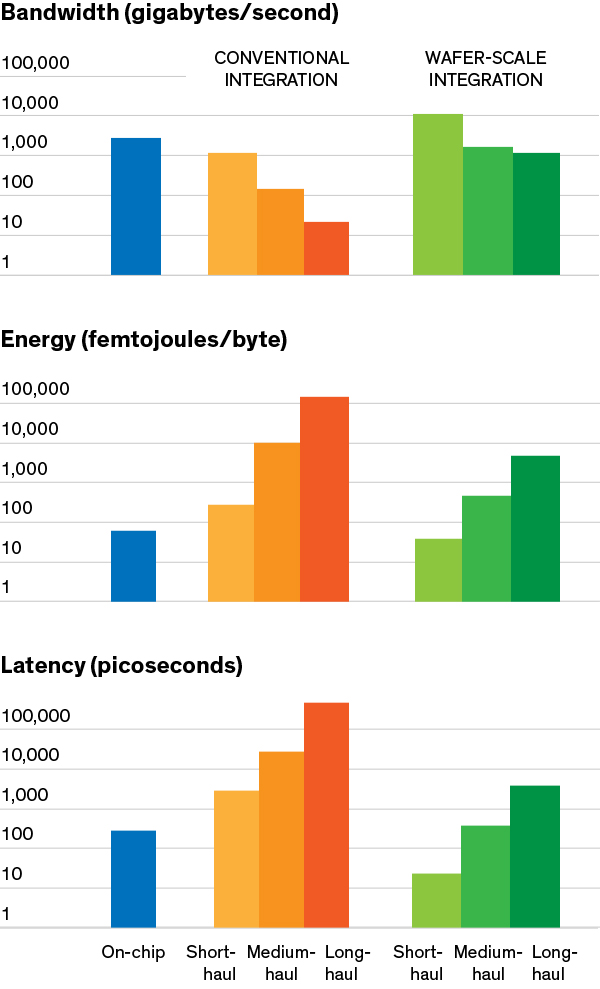

Von oben nach unten: Bandbreite (GB / s), Stromverbrauch (fJ / B), Verzögerung (ps).

Von oben nach unten: Bandbreite (GB / s), Stromverbrauch (fJ / B), Verzögerung (ps).

Blau - System auf einem Chip, Rottöne - normale Integration, Grüntöne - System auf SubstratDie Vorteile von SoIF gegenüber SoC sind auf die Größe der Verzögerung zurückzuführen. Kleine Löschvorgänge sind billiger zu produzieren als große SoCs, da sie aufgrund ihrer geringen Größe eine geringere Ausschussrate aufweisen. In SoIF hat nur das Substrat selbst eine große Größe. Es ist jedoch unwahrscheinlich, dass sie ein Problem mit der Ehe hat, da sie aus mehreren Schichten besteht, die leicht herzustellen sind. Der größte Teil des Verlusts aufgrund von Defekten ist auf Defekte in den Transistorschichten oder in überdichten unteren Metallschichten zurückzuführen, und dies ist bei einem miteinander verbundenen Siliziumnetzwerk der Fall.

Darüber hinaus wird SoIF alle Vorteile haben, bei deren Verfolgung die Branche auf Chipsätze umstellt. Beispielsweise sollte der Übergang von SoIF zum nächsten Herstellungsprozess einfacher und billiger sein. Jedes Dylet kann seine eigene Produktionstechnologie haben, und nur die Dylets, die es wirklich benötigen, können aktualisiert werden. Und Löschungen, die nicht besonders von reduzierten Transistoren profitieren, müssen nicht geändert werden. Durch diese heterogene Integration können Sie eine völlig neue Klasse von Systemen erstellen, die Mischer verschiedener Generationen und Technologien mischen, die normalerweise nicht mit CMOS kompatibel sind. Zum Beispiel hat unsere Gruppe kürzlich die Kombination eines Indiumphosphidkristalls mit SoIF als Beispiel für eine mögliche Verwendung in Hochfrequenzschaltungen demonstriert.

Da die Diletten vor dem Anschließen an SoIF hergestellt und überprüft werden, können sie in verschiedenen Systemen verwendet werden, wodurch sie erheblich eingespart werden. Infolgedessen können die Gesamtkosten für die Entwicklung und Herstellung von SoIF um 70% niedriger sein als die von SoC. Dies gilt insbesondere für große Systeme, die in kleinen Chargen hergestellt werden - wie dies in der Luft- und Raumfahrt- und Verteidigungsindustrie der Fall ist, wo nur Chargen in der Größenordnung von mehreren hundert oder tausend Einheiten nachgefragt werden. Kundenspezifische Systeme werden bei SoIF auch einfacher zu handhaben sein, da dies sowohl Kosten als auch Entwicklungszeit reduziert.

Wir glauben, dass solche Kosten- und Diversitätsvorteile zum Beginn einer neuen Ära der Innovation führen können, in der neue Hardware einer viel größeren Anzahl von Designern, Startups und Universitäten zur Verfügung stehen wird.

In den letzten Jahren haben wir erhebliche Fortschritte in der Si-IF-Integrationstechnologie erzielt, aber es bleibt noch viel zu tun. Zunächst muss ein kommerziell realisierbarer Si-IF-Produktionsprozess mit geringem Defekt gezeigt werden.

Die Herstellung von Substraten im Si-IF-Maßstab erfordert möglicherweise Innovationen in der maskenlosen Lithographie. Die meisten heute existierenden lithografischen Systeme können Substrate mit einer Größe von 33 x 24 mm herstellen. Daher benötigen wir ein System, das ein Substrat mit einem Durchmesser von 300 mm liefern kann.Wir brauchen auch Mechanismen zur Überprüfung von nackten Daylets und Si-IF. Die Industrie bewegt sich bereits in Richtung Test von bloßen Kristallen, da Chiphersteller auf Cheatlets in fortschrittlichen Paketen und dreidimensionaler Integration umsteigen.Dann brauchen wir neue Strahler oder andere Wärmeableitungsstrategien, die eine gute Wärmeleitfähigkeit von Silizium nutzen. Meine Kollegen an der University of California und ich entwickeln eine integrierte Substratkühlungs- und Ernährungslösung namens PowerTherm.Darüber hinaus benötigen Sie für die Montage kompletter Systeme Rahmen, Befestigungselemente, Steckverbinder und Kabel.Wir müssen auch einige Änderungen an der Entwicklungsmethodik vornehmen, damit eines der SoIF-Versprechen Wirklichkeit wird. Si-IF ist ein passives Substrat, in dem nur ein Leiter vorhanden ist. Daher sollten die Verbindungen zwischen den Flügen kurz sein. Für längere Spuren, die weit entfernte Diletten verbinden, benötigen wir Zwischendiletten, die Daten weiter unten in der Kette weitergeben. Es wird notwendig sein, die Entwurfsalgorithmen zu überprüfen, die für die Anordnung der Elemente und den Zweck der Kontakte verantwortlich sind, damit sie diese Art der Integration voll ausnutzen können. Außerdem müssen wir neue Wege entwickeln, um verschiedene Systemarchitekturen zu untersuchen, die die Heterogenität und Aktualisierbarkeit von SoIF nutzen.Wir müssen auch die Zuverlässigkeit der Systeme berücksichtigen. Wenn sich herausstellt, dass ein Dylet nach dem Anbringen defekt ist oder während des Betriebs ausfällt, ist es sehr schwierig, es auszutauschen. Daher ist es in SoIF, insbesondere in großen, erforderlich, Fehlertoleranz aufzubauen. Es kann auf Netzwerkebene oder auf Dayleet-Ebene implementiert werden. Auf Netzwerkebene muss sichergestellt werden, dass das Signal unter Umgehung der ausgefallenen Daylets weitergeleitet wird. Auf Daylet-Ebene können verschiedene Tricks mit physischer Redundanz in Betracht gezogen werden, beispielsweise die Verwendung mehrerer Kupferstifte für jeden der E / A-Ports.Natürlich hängen die Vorteile einer Daylet-Baugruppe von der Verfügbarkeit nützlicher Daylets ab, die in das System integriert werden können. Bisher sortiert die Industrie, welche Art von Dilets produziert werden sollen. Sie können nicht einfach ein Daylet für jedes Subsystem in SoC erstellen, da einige der Daylets zu klein sind. Ein vielversprechender Ansatz ist die statistische Verarbeitung vorhandener SoC-Schaltungen und Leiterplatten, um Funktionen zu finden, die dazu neigen, physikalisch näher beieinander zu liegen. Wenn diese Funktionen dieselben Produktionstechnologien und Aktualisierungszyklen haben, müssen sie in ein einziges Daylet integriert werden.Diese Liste von Problemen mag sehr lang erscheinen, aber Forscher arbeiten bereits an einigen von ihnen im Rahmen des CHIPS-Programms (Common Heterogene Integration and IP Reuse Strategies) der Agentur für fortgeschrittene Verteidigungsforschungsprojekte sowie mit Industriekonsortien. Und wenn wir diese Probleme lösen können, wird es uns ernsthaft helfen, das Erbe von Moores Gesetz auf kleinere, schnellere und kostengünstigere Weise aufrechtzuerhalten.