Vor kurzem haben wir uns mit der Wiederherstellung des Apollo-Bordsteuerungscomputers befasst, der für die Steuerung, Navigation und Überwachung an Bord von Apollo-Missionen verantwortlich war, die zum Mond fliegen. Dieser historische Computer war einer der ersten, der integrierte Schaltkreise (ICs) verwendete, und sein Prozessor war vollständig auf NOR-Ventilen aufgebaut (der zweite IC-Typ, ein Ausleseverstärker, wurde im Speicher des Computers verwendet). In diesem Artikel werde ich die Architektur und das Design der CPU beschreiben.

Apollo Control Computer Architektur

Getrennte Fächer des Apollo-Steuercomputers. Das linke Fach enthält Logik basierend auf NOR-Gattern. Rechts - Speicher- und Hilfskomponenten.Der

Getrennte Fächer des Apollo-Steuercomputers. Das linke Fach enthält Logik basierend auf NOR-Gattern. Rechts - Speicher- und Hilfskomponenten.Der Apollo Guidance Computer (AGC) wurde in den 1960er Jahren entwickelt, damit Apollo-Missionen zum Mond fliegen können. Zu einer Zeit, als die meisten Computer Platz von einem großen Kühlschrank bis zu einem ganzen Raum beanspruchten, war die AGC etwas Einzigartiges - sie war klein genug, um an Bord des Apollo-Raumfahrzeugs zu passen, wog 32 kg und nahm nicht mehr als 0,03 m ein

3 (30 Liter).

Der AGC-Computer ist 15-Bit. Es ist seltsam, eine Wortgröße zu treffen, die keine Zweierpotenz ist, aber in den 1960er Jahren, noch bevor Bytes populär wurden, verwendeten Computer eine Vielzahl von Wortgrößen. 15 Bit lieferten eine ausreichende Genauigkeit für die Landung auf dem Mond (und verwendeten Daten bei Bedarf mit doppelter und dreifacher Genauigkeit), sodass 16 Bit die Größe und das Gewicht des Computers einfach unnötig erhöhen würden.

Der AGC-Befehl befand sich in einem 15-Bit-Wort und bestand aus 3 Bits, die den Operationscode angaben, und 12 Bits, die die Adresse im Speicher angaben. Leider reichten diese Volumes immer noch nicht aus, sodass der Computer zahlreiche Tricks und Problemumgehungen verwendete und sich die Architektur als ziemlich umständlich herausstellte. Eine 12-Bit-Speicheradresse konnte nur auf 4K-Wörter zugreifen. Zur gleichen Zeit hatte AGC 2K Wörter im Hauptspeicher und 36K Wörter im Kernspeicher. Um auf den gesamten Speicher zuzugreifen, verwendete AGC ein ausgeklügeltes Speicherbank-Schaltsystem und mehrere Register. Mit anderen Worten, auf den Speicher konnte nur in Teilen von 256 Wörtern und auf den ROM zugegriffen werden - in Teilen von etwas größerer Größe.

3 Bits für den Operationscode reichten nicht aus, um 34 mögliche Befehle direkt anzuzeigen. Daher verwendete AGC Tricks mit der Erweiterung des Befehlswertes und der Tatsache, dass einige Befehle sinnvoll waren, nur mit bestimmten Speicherzellen ausgeführt zu werden. Darüber hinaus wurden Tricks wie "magische" Adressen im Speicher verwendet. Beispielsweise wurde beim Schreiben in die Zelle "Rechtsverschiebung" eine bitweise Verschiebung durchgeführt, sodass keine separate Anweisung "Rechtsverschiebung" erforderlich war. Es gab auch Anweisungen, die mehrere Aktionen gleichzeitig kombinierten.

Die AGC-Architektur war selbst für die Standards der 1960er Jahre ziemlich einfach. Obwohl es in einer Zeit komplexer und leistungsfähiger Mainframes entwickelt wurde, waren die Fähigkeiten von AGC sehr begrenzt. In Bezug auf Leistung und Architektur ist es vergleichbar mit frühen Mikroprozessoren. Seine Stärken waren seine kompakte Größe und die großartigen Möglichkeiten zur Eingabe und Ausgabe von Daten in Echtzeit.

Das folgende Architekturdiagramm zeigt die Hauptkomponenten der AGC. Ich habe die Teile, auf die ich näher eingehen möchte, farblich hervorgehoben. AGC hatte einen kleinen Satz von Registern und ein einfaches Arithmetikmodul, das sich nur mit Addition befasste. Er hatte nur 36K Wörter ROM und 2K Wörter RAM. Der „Schreibbus“ war die Hauptmethode für die Datenübertragung zwischen Komponenten. Decodierungsanweisungen und ein Sequenzgenerator erzeugten Steuerimpulse für die AGC.

AGC-Blockdiagramm

AGC-BlockdiagrammEtwa die Hälfte des Diagramms ist mit Speicher belegt, was die Tatsache widerspiegelt, dass die AGC-Architektur in vielerlei Hinsicht um ihren Speicher herum entwickelt wurde. Wie die meisten Computer in den 1960er Jahren verwendete AGC Kernspeicher und speicherte jedes Bit in einem winzigen Ferritring (Kern), der auf einem Drahtgeflecht aufgereiht war. Da jedes Bit einen separaten physikalischen Kern benötigte, war die Menge eines solchen Speichers radikal geringer als die eines modernen Halbleiters. Ein charakteristisches Merkmal des Speichers auf den Kernen war, dass das Lesen eines Wortes aus dem Speicher es löschte, sodass dieser Wert nach jedem Zugriff neu geschrieben werden musste. AGC hatte auch einen festen ROM-Speicher, die berühmten

zusammengefügten Kerne - sie wurden zum Speichern von Programmen verwendet und physisch mit Drähten zusammengefügt (siehe unten).

Nahaufnahme Speicher auf genähten Kernen

Nahaufnahme Speicher auf genähten KernenNOR-Ventile

AGC war einer der ersten Computer, die IP verwendeten. Die Möglichkeiten dieser ersten IPs waren sehr begrenzt; Auf AGC-Chips (unten) gab es nur sechs Transistoren und acht Widerstände, und zusammen implementierten sie ein NOR-Gatter mit drei Eingängen.

Doppel-NOR-Ventil mit drei Eingängen von AGC. Zehn Drähte außerhalb des Kristalls sind mit den externen Kontakten des IC verbunden.

Doppel-NOR-Ventil mit drei Eingängen von AGC. Zehn Drähte außerhalb des Kristalls sind mit den externen Kontakten des IC verbunden.Die schematische Bezeichnung des NOR-Ventils ist unten gezeigt. Dies ist das einfachste Logikgatter: Wenn alle Eingänge gleich Null sind, ist der Ausgang gleich Eins. Sie werden überrascht sein, aber ein NOR-Gatter reicht aus, um einen Computer zu erstellen. NOR ist ein Universalventil: Jedes andere logische Ventil kann auf seiner Basis hergestellt werden. Wenn wir zum Beispiel alle NOR-Eingänge kombinieren, erhalten wir einen Inverter. Nachdem wir den Wechselrichter am Ausgang des NOR platziert haben, erhalten wir ein ODER-Ventil. Durch Platzieren der Inverter an den Eingängen des NOR-Gatters erhalten wir ein UND-Gatter. Und aus diesen Toren können Sie eine komplexere Logik erstellen: Trigger, Addierer und Zähler.

Das NAND-Ventil hat die gleiche Vielseitigkeit. In modernen Schaltungen werden aus technischen Gründen NANDs häufiger verwendet als NORs. Im beliebten Kurs "

Von NAND zu Tetris " wird beschrieben, wie man einen Computer aus NAND-Ventilen bis zur Implementierung des Spiels "Tetris" erstellt. Zunächst wird ein Satz von Logikgattern aus NAND aufgebaut (NOT, AND, OR, XOR, Multiplexer, Demultiplexer). Dann werden größere Bausteine aus ihnen (Trigger, Addierer, Zähler, ALU, Register) und aus ihnen - einem Computer - erstellt.

Das NOR-Gatter gibt 1, wenn es an allen Eingängen 0 hat. Wenn mindestens einer der Eingänge 1 hat, gibt das NOR 0.

Das NOR-Gatter gibt 1, wenn es an allen Eingängen 0 hat. Wenn mindestens einer der Eingänge 1 hat, gibt das NOR 0.Sehr häufig stößt AGC auf eine Komponente wie den RS-Trigger (Set-Reset, Set / Reset). Diese Schaltung besteht aus zwei NOR-Gattern und speichert ein Datenbit. Bit 1 wird am gesetzten Eingang gespeichert, und Bit 0 wird am zurückgesetzten Eingang gespeichert. Das heißt, Impuls 1, der an den eingestellten Eingang angelegt wird, schaltet das obere Ventil aus und das untere ein, so dass Ausgang 1 ausfällt. Impuls 1, der an den zurückgesetzten Eingang angelegt wird, bewirkt das Gegenteil . Wenn an beiden Eingängen 0 angewendet wird, merkt sich der Trigger seinen vorherigen Zustand und spielt die Rolle eines Laufwerks. Im nächsten Abschnitt zeigen wir, wie Register aus einem Trigger erstellt werden.

RS-Trigger von zwei NOR-Gattern. Wenn ein Ventil eingeschaltet ist, schaltet es das andere aus. Eine Linie über einem der Ausgänge zeigt an, dass sie den anderen ergänzt.

RS-Trigger von zwei NOR-Gattern. Wenn ein Ventil eingeschaltet ist, schaltet es das andere aus. Eine Linie über einem der Ausgänge zeigt an, dass sie den anderen ergänzt.Register

AGC verfügt über einen kleinen Registersatz zur temporären Speicherung von Werten außerhalb des Hauptspeichers. Das Hauptregister ist das Laufwerk (A), das in vielen arithmetischen Operationen verwendet wird. Es hat auch ein Zählerregister Z, arithmetische Blockregister X und Y, Puffer B, Rücksprungadresse Q und einige andere (in modernen Computern wird der Stapel verwendet, um Routinen aufzurufen und von diesen zurückzukehren, aber in dieser Ära mussten Programmierer den Stapel selbst für die Rekursion schreiben ) Für den Zugriff auf den Speicher gibt es ein Speicheradressregister S und für Daten ein Speicherpufferregister G. Außerdem hat die AGC Register im Hauptspeicher - zum Beispiel Eingabe- / Ausgabezähler.

Das folgende Diagramm zeigt das für den Fall mit einem Bit und zwei Registern vereinfachte AGC-Registerschema. Jedes Registerbit hat einen Trigger unter Verwendung des zuvor beschriebenen Schemas (blau und lila). Daten werden über den Schreibbus (rot) zu und von den Registern übertragen. Um in das Register zu schreiben, wird der Trigger durch ein Löschsignal (CQG oder CZG, grün) zurückgesetzt. Dann ermöglicht das "Schreib" -Signal (WQG oder WZG, orange) den Daten, die entlang des Schreibbusses gehen, den entsprechenden Registerauslöser zu setzen. Zum Lesen des Registers leitet das Lesesignal (RQG oder RZG, Cyan) den Triggerausgang über den Aufzeichnungsverstärker an den Aufzeichnungsbus weiter und wird in anderen Teilen der AGC verwendet. Das vollständige Registerschema ist komplexer, es hat mehrere 16-Bit-Register, aber das Grundschema ist wie folgt.

Vereinfachte AGC-Registeroperation

Vereinfachte AGC-RegisteroperationDas Registerdiagramm zeigt drei wichtige Punkte. Erstens wird die Registerschaltung aus NOR-Gattern aufgebaut. Zweitens wird die Datenbewegung um den Schreibbus herum aufgebaut. Schließlich hängen die Aktionen der Register von bestimmten Steuersignalen ab, die zum richtigen Zeitpunkt eintreffen.

Rechenmodul

Die meisten Computer verfügen über ein

arithmetisches Logikgerät , das arithmetische und boolesche Operationen ausführt. Im Vergleich zu modernen Computern ist das arithmetische Modul von AGC sehr begrenzt: Es addiert nur 16-Bit-Größen, daher wird es als arithmetisches Modul und nicht als arithmetisch-logisches Modul bezeichnet (der Rest der Operationen wird durch verschiedene Tricks ausgeführt, zum Beispiel wird die Subtraktion durch Addition durchgeführt, bevor für eines der Argumente werden die Bits umgekehrt usw.).

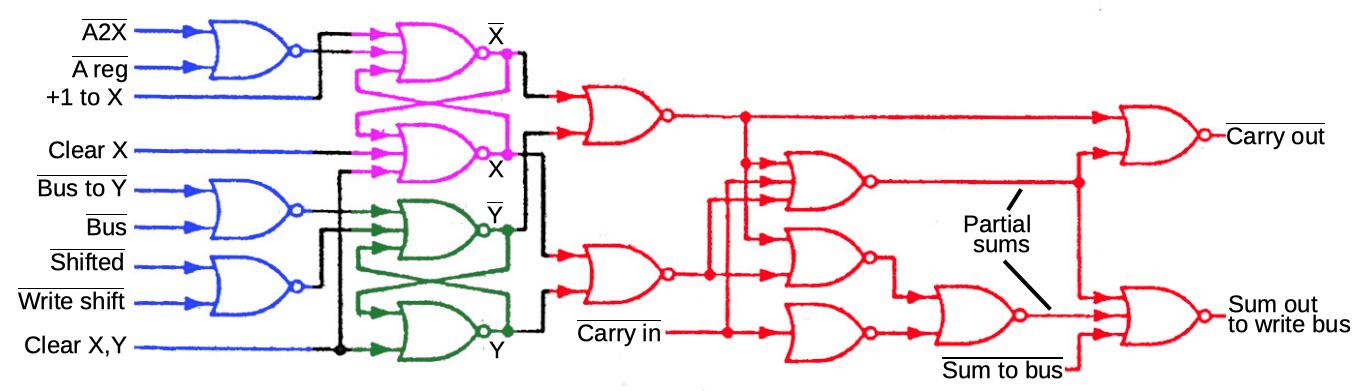

Das folgende Diagramm zeigt ein Bit des AGC-Arithmetikmoduls.

Der Volladdierer (rot) berechnet die Summe von zwei Bits und Übertrag. Die Übertragung wird an den nächsten Addierer übertragen. Auf diese Weise können sie kombiniert werden, um längere Wörter hinzuzufügen (um die Übertragung von Übertragungen in Fällen wie 111111111111111 + 1 zu beschleunigen, verwendet AGC einen Addierer mit einem

Übertragungssprung ).

Die Register X und Y (lila und grün) stellen dem Addierer zwei Eingangsbits zur Verfügung. Sie werden mit den bereits an NOR-Ventilen beschriebenen Triggern implementiert. Die blaue Schleife schreibt die Werte gemäß den Steuersignalen in die X- und Y-Register. Das Schema ist ziemlich kompliziert, da es Ihnen ermöglicht, Konstanten und Werte mit einer Verschiebung der Register zu speichern, aber ich werde nicht auf dieses Thema eingehen. Achten Sie auf das Steuersignal A2X, das den Wert von Register A an Register X überträgt; Wir werden später auf ihn zurückkommen.

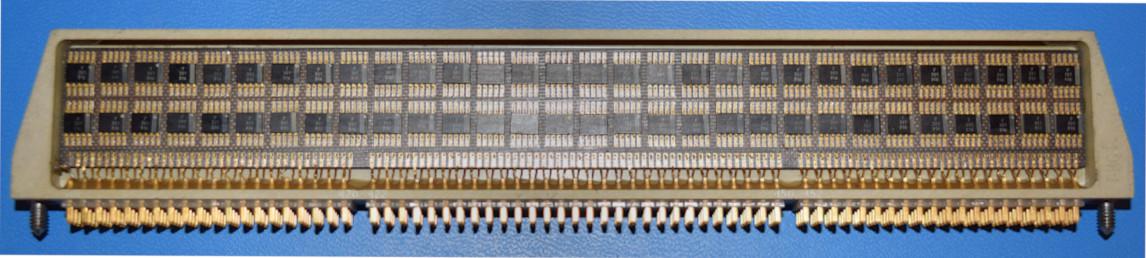

Das Foto unten zeigt die physikalische Implementierung der AGC-Schaltung. Dieses Modul implementiert vier Bits für Register und ein Arithmetikmodul. Schwarze Rechtecke sind flache IPs. Jedes Modul verfügt über zwei Karten mit jeweils 60 Chips und insgesamt 240 NOR-Gattern. Das arithmetische Modul und die Register sind aus vier identischen Modulen zusammengesetzt, von denen jedes vier Bits verarbeitet; Dies ähnelt dem

Mikroprozessorabschnitt .

Das Rechenmodul und die Register bestehen aus vier identischen Modulen. Module werden in Steckplätzen von A8 bis A11 installiert.

Das Rechenmodul und die Register bestehen aus vier identischen Modulen. Module werden in Steckplätzen von A8 bis A11 installiert.Befehlsausführung

Dieser Abschnitt beschreibt die Abfolge von Operationen, die die AGC ausführt, um die Anweisung auszuführen. Insbesondere werde ich zeigen, wie die Anweisung ADS (Add to Storage) funktioniert. Dieser Befehl liest den Wert aus dem Speicher, fügt ihn dem Laufwerk hinzu (Register A) und speichert die Summe sowohl im Addierer als auch im Speicher. Dies ist eine einzelne Anweisung, aber für ihre Ausführung unternimmt AGC mehrere Schritte und viele Werte werden hier und da verschoben.

Der Befehlszeitgeber ist aufgrund des Speichersubsystems auf Magnetkernen implementiert. Insbesondere beim Lesen eines Werts aus dem Speicher wird der gespeicherte Wert gelöscht, sodass der Wert nach jedem Lesen zurückgeschrieben werden muss. Auch beim Zugriff auf den Speicher gibt es eine Verzögerung zwischen der Angabe der Adresse und dem Empfang von Daten. Infolgedessen benötigt jeder Taktzyklus 12 Schritte zum Lesen und anschließenden Aufzeichnen. Jedes Zeitintervall (von T1 bis T12) dauert etwas weniger als Mikrosekunden, und der gesamte Zyklus dauert 11,7 μs und wird als Speicherzykluszeit (MCT) bezeichnet.

Löschbares Magnetkern-Speichermodul von AGC. Es speichert 2 Kiloblätter, jedes Bit wird unter Verwendung eines separaten winzigen Ferritrings gespeichert.

Löschbares Magnetkern-Speichermodul von AGC. Es speichert 2 Kiloblätter, jedes Bit wird unter Verwendung eines separaten winzigen Ferritrings gespeichert.MCT ist die grundlegende Speichereinheit für die Ausführung von Anweisungen. Ein typischer Befehl erfordert zwei Taktzyklen: einen zum Extrahieren des Befehls aus dem Speicher, den zweiten zum Ausführen der Operation. Daher benötigt ein typischer Befehl zwei MCTs (23,4 μs), was 43.000 Anweisungen pro Sekunde ergibt (im Vergleich zu modernen Prozessoren und ihren Milliarden von Anweisungen pro Sekunde ist dies extrem langsam).

AGC verarbeitet Anweisungen und unterteilt sie in Unterbefehle, von denen jeder einen Taktzyklus des Speichers benötigt. Ein ADS-Befehl besteht beispielsweise aus zwei Unterbefehlen: ADS0 (Addition) und STD2 (Aufruf des nächsten Befehls). Das folgende Diagramm zeigt die Bewegung von Daten innerhalb der AGC, um den ADS0-Befehl auszuführen. 12 Takte gehen von links nach rechts.

Die wichtigsten Schritte sind wie folgt:

T1: Die Operandenadresse wird aus dem Befehlsregister B in das Speicheradressregister S kopiert, um mit dem Lesen aus dem Speicher zu beginnen.

T4: Der Operand wird von Speicher zu Speicherdatenregister G gelesen.

T5: Der Operand wird von G auf Addierer Y kopiert. Der Wert von Laufwerk A wird auf Addierer X kopiert.

T6: Der Addierer berechnet die Summe U und kopiert sie in das Datenregister des Speichers G.

T8: Der Programmzähler Z wird in Vorbereitung auf den Empfang des nächsten Befehls aus dem Speicher in das Speicheradressregister S kopiert.

T10: Die Summe aus dem Datenregister des Speichers G wird in den Speicher zurückgeschrieben.

T11: Betrag U wird auf Laufwerk A kopiert.

Obwohl dies eine einfache Summierungsanweisung ist, werden hier über 12 Zeitschlitze immer wieder viele Daten übertragen. Und jeder dieser Aktionen ist ein bestimmtes Steuersignal zugeordnet; Beispielsweise kopiert das Signal A2X im Intervall T5 den Wert von Antrieb A in Register X. Um Register G in Register Y zu kopieren, sind zwei Steuerimpulse erforderlich: RG (Lesen von G) und WY (Schreiben von Y). Im nächsten Abschnitt werde ich erklären, wie das AGC-Steuermodul die erforderlichen Steuersignale für jeden Befehl erzeugt.

Steuermodul

Wie die meisten Computer decodiert das AGC-Steuermodul jeden Befehl und erzeugt Steuersignale, die dem Rest des Prozessors mitteilen, was zu tun ist. Die AGC verwendet ein vorprogrammiertes Steuermodul, das aus NOR-Ventilen besteht, um Signale zu erzeugen. AGC verwendet keinen Mikrocode. Er hat keine Mikrobefehle und kein Kontrollgedächtnis, da dies zu viel physischen Platz beanspruchen würde.

Das Herzstück des AGC-Steuermoduls wird als Crosspoint-Generator bezeichnet. Es benötigt einen Unterbefehl und einen der Zeiträume und generiert Steuersignale für diese Kombination. Man kann es sich in Form eines Gitters vorstellen, auf dem Unterbefehle in eine Richtung und Zeitsegmente in die andere Richtung verlaufen und jeder der Schnittpunkte sein eigenes Steuersignal hat.

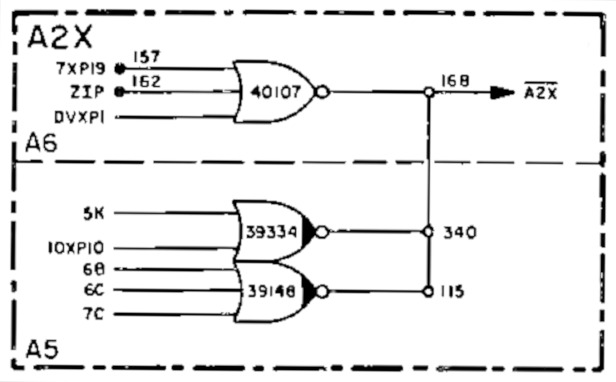

Der Kreuzungsgenerator benötigt viele Komponenten und ist in drei Module unterteilt. Dies ist das A6-Modul. Achten Sie auf die hinzugefügten Drähte, die den Stromkreis verändern. Dies ist eine frühe Version eines Moduls zum Testen vor Ort. Flugmodule hatten bereits keine Drähte.

Der Kreuzungsgenerator benötigt viele Komponenten und ist in drei Module unterteilt. Dies ist das A6-Modul. Achten Sie auf die hinzugefügten Drähte, die den Stromkreis verändern. Dies ist eine frühe Version eines Moduls zum Testen vor Ort. Flugmodule hatten bereits keine Drähte.Aus Effizienzgründen ist das Stellgliedmodul stark optimiert. Anweisungen mit ähnlichem Verhalten werden vom Kreuzungsgenerator kombiniert und verarbeitet, wodurch die Größe der erforderlichen Schaltung verringert wird. Zum Beispiel hat AGC die Anweisung "Hinzufügen zu einem Laufwerk mit doppelter Genauigkeit" (DAS). Da dies ungefähr zwei Additionen einzelner Wörter entspricht, haben die Unterbefehle DAS1 und ADS0 im Schnittstellengenerator eine gemeinsame Logik. Das folgende Diagramm zeigt die Kreuzungsgeneratorschaltung für das Zeitintervall T5, und die Logik des ADS0-Unterbefehls (unter Verwendung des Signals DAS1) ist hervorgehoben. Beispielsweise wird ein 5K-Signal aus einer Kombination von DAS1 und T5 erzeugt.

Aber was sind 5K- und 5L-Signale? Dies ist eine weitere Optimierung. Viele Steuerimpulse werden häufig zusammengeführt. Anstatt sie direkt zu erzeugen, erzeugt der Kreuzungsgenerator Zwischensignale für Kreuzungen. Beispielsweise erzeugt 5K Steuerimpulse A2X und RG und 5L erzeugt Steuerimpulse WY. Das folgende Diagramm zeigt, wie das A2X-Signal erzeugt wird: Jedes der 8 verschiedenen Signale (einschließlich 5K) erzeugt A2X. Ähnliche Schaltungen erzeugen andere Steuersignale. Diese Optimierungen ermöglichten es, die Größe des Kreuzungsgenerators zu reduzieren, aber er blieb immer noch groß und wuchs auf bis zu drei Module an.

Zusammenfassend können wir sagen, dass das Steuermodul dafür verantwortlich ist, der CPU mitzuteilen, was zu tun ist, um die Anweisung auszuführen. Zunächst werden Anweisungen in Unterbefehle unterteilt. Der Kreuzungsgenerator erzeugt die erforderlichen Steuerimpulse für jedes Zeitintervall und jeden Unterbefehl und teilt den Registern, dem Rechenmodul und dem Speicher mit, was sie tun müssen.

Normalerweise bestanden Anweisungen aus zwei Unterbefehlen, es gab jedoch Ausnahmen. Einige der Anweisungen, wie Multiplikation oder Division, erforderten die Verwendung vieler Unterbefehle, da sie aus vielen Schritten bestanden. Umgekehrt verwendete der Sprungbefehl bei TC einen Unterbefehl, da nur der nächste Befehl aufgerufen werden musste.

Andere Prozessoren verwendeten andere Ansätze zur Erzeugung von Steuersignalen.

6502 und viele andere frühe Mikroprozessoren decodierten Anweisungen unter Verwendung eines programmierbaren Logikarrays (PLA), das UND / ODER-Logik über einen Nur-Lese-Speicher implementiert. Mikroprozessor 6502.

Mikroprozessor 6502.Fazit

Es war eine aufregende Tour durch den Apollo-Bordsteuerungscomputer. Um es nicht zu stark zu dehnen, konzentrierte ich mich auf die ADS-Additionsanweisungen und einige Steuerimpulse (A2X, RG und WY). Ich hoffe, Sie haben eine Idee, wie Sie einen Computer aus so primitiven Elementen wie NOR-Ventilen zusammenbauen können.Der sichtbarste Teil der Architektur ist der Datenpfad: ein Rechenmodul, Register und ein Datenbus. AGC-Register basieren auf einfachen Triggern von NOR-Gattern. Und obwohl das AGC-Arithmetikmodul nur Additionen ausführen kann, kann der Computer dennoch den gesamten Satz von Operationen verarbeiten, einschließlich Multiplikations-, Divisions- und Boolescher Operationen.Der Datenpfad ist jedoch nur ein Teil des Computers. Neben anderen kritischen Komponenten gibt es ein Steuermodul, das den Komponenten mitteilt, was sie tun müssen. Der in AGC verwendete Ansatz basiert auf einem Kreuzungsgenerator, der eine hochoptimierte und fest codierte Logik verwendet, um die richtigen Steuerimpulse für bestimmte Unterbefehle und Zeitintervalle zu erzeugen.Mit diesen Fähigkeiten lieferte die AGC Führung, Navigation und Kontrolle an Bord von Apollo-Missionen und ermöglichte die Landung auf dem Mond. Er spornte auch die frühe Industrie für integrierte Schaltkreise an, die 1963 60% der in den USA hergestellten ICs verwendeten. Daher haben moderne Computer AGC und seinen einfachen NOR-Komponenten viel zu verdanken. AGC arbeitet in einem Labor, das an ein altes Tektronix-Oszilloskop angeschlossen ist

AGC arbeitet in einem Labor, das an ein altes Tektronix-Oszilloskop angeschlossen ist