Boris Tsirlin und Alexander Kushnerov

30.10.2013

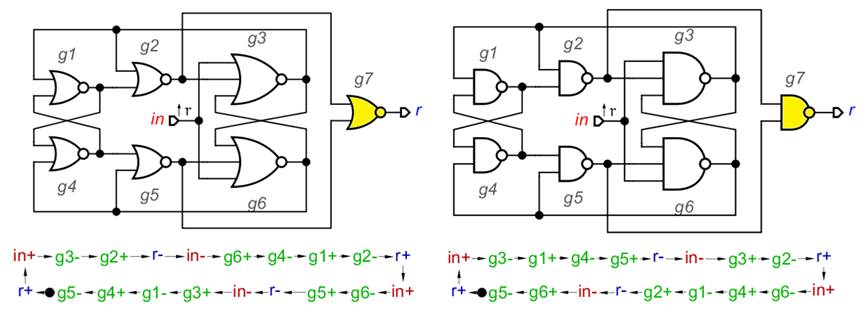

Für einen erfahrenen Schaltungsentwickler ist es nicht schwierig, eine vertraute Schaltung herauszufinden, egal in welcher Form sie gezeichnet wird. In diesem Artikel zeigen wir, dass die beiden Transistorschaltungen aus den Patenten eine Variante des Asynchronous Counting Trigger (AST) sind. Im Vergleich zur Standardschaltung fehlen in den Patenten einige Transistoren. Dies kann als Fehlfunktion angesehen werden. Wir werden zeigen, dass derselbe Fehler, der in der Standardschaltung auftritt, weiterhin ordnungsgemäß funktioniert. Ein AST, der nur für OR-NOT-Elemente [1] oder nur für AND-NOT-Elemente implementiert ist, wird als Harvard-Trigger bezeichnet. Beide Varianten der Schemata sind in Abb. 1 dargestellt. 1, wobei g7 ein Indikator für die vorübergehende Vervollständigung ist. In Zukunft werden wir es nicht berücksichtigen. In Abb. Abbildung 1 zeigt auch die in Workcraft [3] erstellten Signalübergangsgraphen (STGs) [2].

Abb. 1. Asynchroner Zählauslöser (AST) und sein STG.

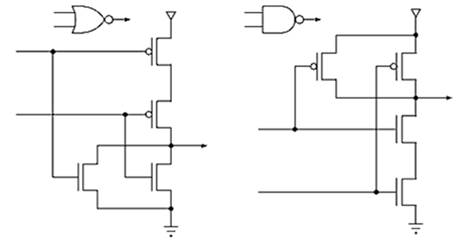

Beachten Sie, dass es in beiden Versionen des AST drei Elementpaare (g1, g2), (g4, g5) und (g3, g6) gibt, die einen gemeinsamen Eingang haben. Transistorschaltungen der Elemente 2I-NOT und 2OR-NOT, die in Fig. 1 gezeigt sind. 2. Elemente mit drei Eingängen sind ähnlich angeordnet und enthalten 6 Transistoren.

Abb. 2. Transistorschaltungen der Elemente 2I-NOT und 2OR-NOT.

Wir nehmen zwei Elemente 2OR-NOT und wählen an jedem Eingang aus, wo der p-MOS-Transistor mit Upit verbunden ist. Verbinden Sie diese Eingänge miteinander und verbinden Sie sie mit Masse (log. 0). Beide Transistoren öffnen und die Spannung an ihren Drains ist gleich Upit. Reicht dies aus, um die Abflüsse sicher anzuschließen und die beiden Transistoren durch einen zu ersetzen, wie in Abb. 3? Nein. Sie müssen überprüfen, was passiert, wenn Sie sich bei der freigegebenen Eingabe anmelden. 1. Die Ausgänge beider Elemente werden mit Masse verbunden, und wir haben eine Brückenschaltung mit vier p-MOS-Transistoren. Für die verbleibenden zwei Eingänge haben wir vier Kombinationen 0 und 1. Es ist leicht zu zeigen, dass in keinem von ihnen ein Kurzschluss zwischen Upit und Masse besteht.

Abb. 3. Zwei 2OR-NOT-Elemente, die sich eine gemeinsame Eingabe teilen.

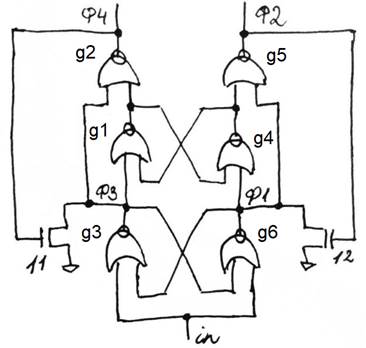

Wir betrachten nun die Impulsverteilerschaltung [4] in Abb. 4. Mit Abb. In 3 können wir dieses Diagramm neu zeichnen, wie in Abb. Es ist bereits möglich, AST in Fig. 5 zu erkennen. In 1 haben dort jedoch die Elemente g3 und g6 3 Eingänge.

Abb. 4. Das Schema des Impulsverteilers aus [4].

Abb. 5. Eine Variante der Schaltung in Abb. 4.

Die Gates der Transistoren 11 und 12 können als Eingänge von 3OR-NOT-Elementen betrachtet werden, bei denen der dritte p-MOS-Transistor kurzgeschlossen ist. Beeinträchtigt dies den korrekten Betrieb der Schaltung? Betrachten Sie die Reihenfolge des Auftretens der Signale in, g2 und g6 am Eingang des Elements g3. Löschen Sie dazu alle anderen Signale in der entsprechenden STG in Abb. 1 wie in Abb. 6.

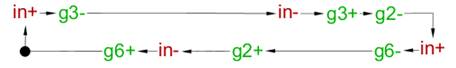

Abb. 6. STG für ODER NICHT. Signale in, g2, g6 und g3.

Da der dritte p-MOS-Transistor kurzgeschlossen ist, kann das Umschalten von g3 + nach dem Umschalten von in und g6- (in beliebiger Reihenfolge) erfolgen, ohne das Umschalten von g2- zuzulassen. Wie jedoch aus Fig. 1 ersichtlich ist. In 6 gibt es im Abschnitt von g2 + nach g2- nur in und g6 +, daher tritt das verbotene Schalten von g3 + nicht auf. Vor dem Schalten von g2 + ist das Element g3 bereits bei 0 und an seinem Eingang ist g6 immer noch 0, d.h. Der erste p-mos-Transistor ist offen. Das Schalten von g2 + öffnet den Transistor 11 und sollte den kurzgeschlossenen p-MOS-Transistor ausschalten. Dies geschieht nicht, außerdem schaltet das Schalten den zweiten p-MOS-Transistor ein. Somit beginnt durch zwei offene p-MOS-Transistoren und einen offenen Transistor 11 Strom von Upit nach Masse zu fließen. Dies dauert kurze Zeit, bis der nächste g6 + -Schalter den ersten p-MOS-Transistor schließt. Während dieser Zeit liefert der Transistor 11 0 am Ausgang von g3. Wie genau? Angenommen, die Widerstände offener p-MOS- und n-MOS-Transistoren sind gleich und gleich R, dann springt die Spannung an g3 nach dem Einschalten von 0 auf (1/3) Upit, dies ist jedoch im Idealfall der Fall. In der Praxis gibt es eine gewisse parasitäre Kapazität zwischen g3 und Masse, deren Spannung gleichmäßig ansteigt und möglicherweise nicht (1/3) Upit erreicht. Auf die eine oder andere Weise ist diese Spannung kleiner als (1/2) Upit und bedeutet ein Protokoll. 0. Für den Transistor 12 ist alles ähnlich, er liefert eine kurze Zeit 0 am Ausgang von g6. Somit bestimmen die Verzögerungen der Elemente g6 und g3 zwei Zeiträume, in denen der Trigger einen großen Strom von ungefähr gleich Upit / (3R) verbraucht.

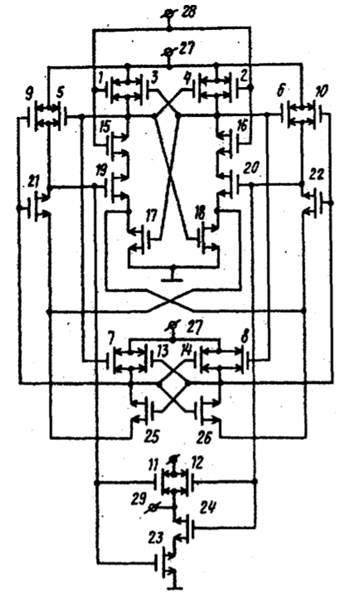

Betrachten wir nun die Zähltriggerschaltung [5] in Abb. Hier bilden die Transistoren 11, 12, 24, 23 das 2I-NOT-Element, das anscheinend ein Indikator für AST in Fig. 1 ist. Ein weiteres Element 2I-NOT wird durch die Transistoren 7, 13, 25 und 18 gebildet. Beachten wir die Tatsache, dass der Transistor 18 mit Masse verbunden ist und ähnlich dem Beispiel in Fig. 1. 3, ist den drei Elementen gemeinsam UND NICHT. Das zweite Element 2I-NOT, das den Transistor 18 enthält, wird durch die Transistoren 5, 9, 21 gebildet, und das dritte Element ist 3I-NOT an den Transistoren 2, 4, 16, 20. Parallel zu den Transistoren 2 und 4 sollte ein dritter p-MOS-Transistor vorhanden sein aber er ist abwesend. Die Schaltung in Abb. 7 ist symmetrisch, zum besseren Verständnis zeichnen wir es neu, wie in Abb. 8.

Abb. 7. Schema des zählbaren Triggers aus [5].

Abb. Eine Variante der Schaltung in Abb. 7.

Wird es in Abb. 1 g3- und g6-Ausgänge geben? 8 richtig schalten, wenn der dritte parallele p-mos-Transistor fehlt? Dies wird nach Analyse der STG in Fig. 1 verstanden. 9, die wie im vorherigen Fall aus dem entsprechenden STG in Fig. 1 erhalten wird. 1 durch Entfernen aller Signale außer in, g2, g6 und g3.

Abb. 9. STG für NAND. Signale in, g2, g6 und g3.

Das g3-Element ist 3I-NOT. Nach dem Einschalten von +, g6 + und g2 + (in beliebiger Reihenfolge) schaltet g3- um. Jede der Rückwärts-, g6- oder g2- Rückwärtsschaltungen sollte die g3 + -Schaltung bewirken. G2- kann den fehlenden p-MOS-Transistor jedoch nicht öffnen, sodass g3 bei 0 bleibt und auf das Umschalten des In- oder G6- wartet. Wie aus Fig. In 9 gibt es auf dem Abschnitt von g3- nach g3 + kein Schalten von g2- und der p-MOS-Transistor wird hier nicht benötigt. Andererseits sollte dieser Transistor ein Protokoll liefern. 1 bis g3, wenn in und g6 willkürlich umschalten. Betrachten Sie in Abb. 9. Abschnitt von g3 + bis g2 +. Das Schalten von g2- schließt den Transistor 19. Als nächstes schließt das Einschalten von + den Transistor 1 und öffnet den Transistor 15. Das Element g6 bleibt bei 1, d.h. Der Transistor 17 ist offen und der Transistor 3 ist geschlossen. Somit trennt in + g3 sowohl von der Erde als auch von Upit. Das Protokoll wird jedoch auf g3 gehalten. 1, da in der Praxis eine parasitäre Kapazität zwischen g3 und Masse besteht, die bis zu Upit aufgeladen wird. Das Schalten von g6- öffnet den Transistor 3 und verbindet diese Kapazität mit Upit. In der zweiten Hälfte des Programms ist alles ähnlich. Somit bestimmen die Verzögerungen der Elemente g6 und g3 die Zeit, während der der Zustand im Tank gespeichert ist. In der Praxis ist es wichtig, dass der Leckstrom der Transistoren 19 und 20 klein ist, da sich sonst die Kapazität in der zugewiesenen Zeit unter (1/2) Upit entladen kann.

Im Vergleich zum Standard-AST in Abb. 1, in den Diagrammen in Fig. 5 und in Fig. 8, die Funktion der Einstellung auf 1 Element 3 ODER NICHT und die Rücksetzfunktion auf 0 von Element 3 ODER NICHT beschädigt. Dies bedeutet, dass der Standard-AST auch dann ordnungsgemäß funktioniert, wenn in den Elementen g6 und g3 eine entsprechende Fehlfunktion auftritt. Für eine Standardschaltung (ohne g7) werden 28 Transistoren benötigt. Für die Schaltungen in Abb. 4 und in Fig. 7 (ohne Transistoren 11, 12, 24, 23) benötigen Sie 23 bzw. 22 Transistoren. Wenn Sie die fehlenden p-MOS-Transistoren zurückgeben, arbeiten diese Schaltungen zuverlässiger. Die minimale Anzahl von Transistoren in der Schaltung in Fig. 7 bedeutet nicht notwendigerweise, dass es besser als die Schaltung in Fig. 1 ist. 4 und bessere Schaltung in Abb. 1. Neben der Anzahl der Transistoren und der Stromaufnahme gibt es weitere wichtige Parameter, zum Beispiel

- Komplexität einer zusätzlichen Schaltung zum Einstellen von Anfangszuständen

- Ladekapazität (Nachladerate der Ladekapazität)

- Austrittsrate aus dem metastabilen Zustand

- Anzahl und Werte der parasitären Kapazitäten

- Anzahl und Werte der Leckströme

Eine vergleichende Analyse dieser Parameter sowie eine Diskussion von AST-Schemata, die für andere Elemente implementiert sind, gehen über den Rahmen dieses Artikels hinaus.

Literatur

[1] GT Osborne, "Asynchrone binäre Zählerregisterstufe mit Flip-Flop und Gate unter Verwendung mehrerer miteinander verbundener NOR-Schaltungen." Patent US3139540, 30. Juni. 1964.

[2] L. Ya. Rosenblum und A. V. Yakovlev, "Über eine neue grafische Form zur Veranschaulichung des Wesens der Erfindung", Issues of Invention, Nr. 11, pp. 36-40, 1988.

[3] https://workcraft.org

[4] V. I. Goryachev, B. M. Mansurov, Ya. D. Martynenko und R. G. Talibov, "Vierphasen-Impulsverteiler". Copyright-Zertifikat SU342299 vom 14.06.1972.

[5] V. I. Varshavsky, N. M. Kravchenko, V. B. Marakhovsky und B. S. Tsirlin, "Counting Trigger on CMOS Transistors". Copyright-Zertifikat SU1398069, 23.05.1988.