Diese Woche teilte Intel seine langfristigen Pläne für die Einführung neuer Herstellungsverfahren. Um 2029

will Intel eine Prozesstechnologie mit 1,4-nm-Standards einführen. Nach 10 Jahren wird das Management-Team des Unternehmens wahrscheinlich nicht mehr das gleiche sein wie heute. Diese Pläne erinnern also auf subtile Weise an das Gleichnis von Khoja Nasreddin über den gut gelesenen Esel, Khan und Lehrer des Tieres in der Person von Khoja. Gegen Mittag ist der Angeklagte möglicherweise nicht da. Darum geht es aber nicht. Geplant akzeptieren wir dann als Leitfaden zum Handeln.

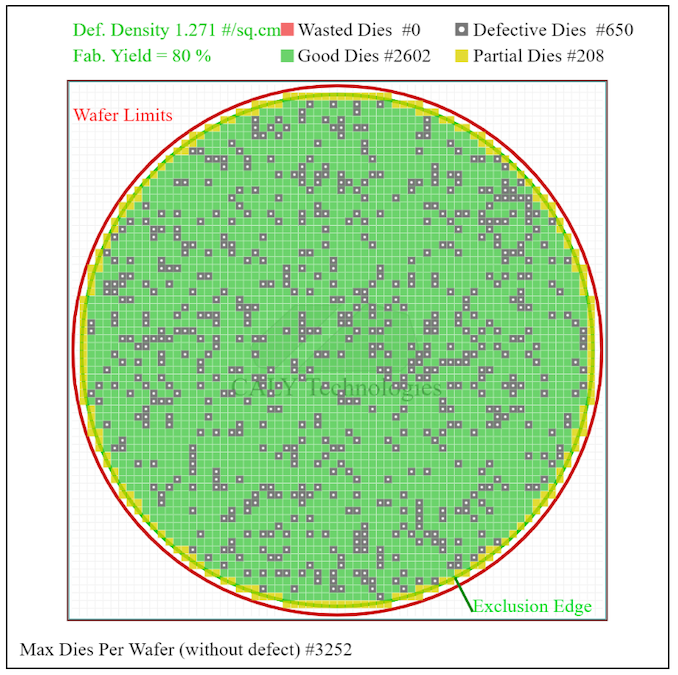

In den Lagern der führenden Halbleiterhersteller gibt es etwas mehr Klarheit, was durch die riskante Herstellung von TSMC-Chips mit 5-nm-Standards bestätigt wird (

heute liegt die Defektrate bei Kristallen mit einer Fläche von 17,92 mm

2 bei 3-8%) AMD Zen 2 Größe, die Heiratsquote wird höher sein - bis zu 60%) Vor der Veröffentlichung von AMD-Prozessoren mit 5-nm-Standards werden jedoch noch mindestens anderthalb Jahre vergehen.

/ Bild von der AnandTech-Website

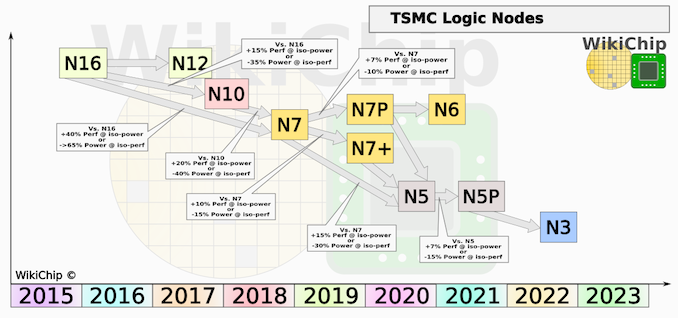

/ Bild von der AnandTech-WebsiteAb dem zweiten Quartal wird die TSMC-Prozesstechnologie mit 5-nm-Standards für die Serienproduktion von SoC auf ARM-Kernen verwendet. Im Jahr 2022 wird TSMC offensichtlich mit der riskanten Produktion von 3-nm-Chips (was auch immer diese Nanometer bedeuten) beginnen, und in ein paar Jahren verspricht das Unternehmen, mit der Produktion von 2-nm-Lösungen zu beginnen. Es wird 2024-2025 sein oder zwei bis drei Jahre früher, als Intel die gleiche Prozesstechnologie einführen wird.

Prozesse mit 5-nm- und 4-nm-Standards sind für Samsung die

Weiterentwicklung der 7-nm-Prozesstechnologie, die sich in einer geringen schrittweisen Reduzierung der Metallisierungsschritte unter FinFET-Elementen wie Kanälen und Gates äußern wird. Im Allgemeinen bleibt die Struktur der Transistoren (die Anzahl der Flanken) gleich, da sich die Struktur der SRAM-Zelle nicht ändert. Samsung wird im Jahr 2021 mit der Produktion von Chips im 4-nm-Verfahren beginnen. Im selben Jahr verspricht das Unternehmen den Start einer riskanten Produktion mit einer 3-nm-Prozesstechnologie. Und einige südkoreanische Quellen

behaupten, dass dies bereits 2020 geschehen könnte, was unwahrscheinlich erscheint.

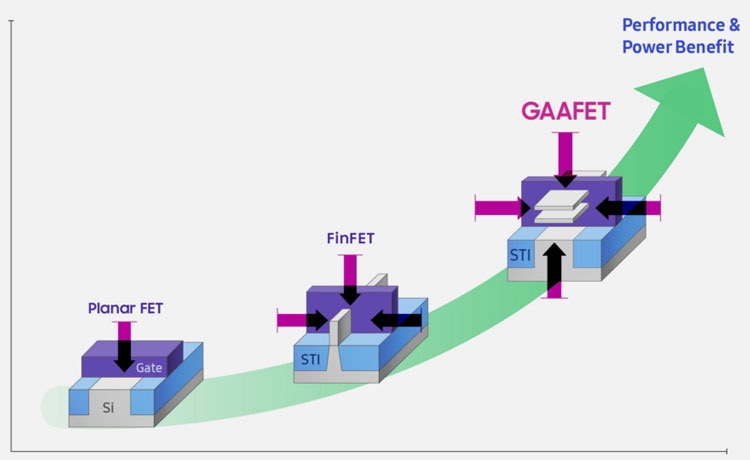

In diesem Artikel interessieren wir uns für die Tatsache, dass Samsung und natürlich Intel und TSMC bis zur 4-nm-Prozesstechnologie FinFET-Transistoren verwenden - Finnen mit hohen Gates, in die vertikale Kanalkämme geschnitten und durchstoßen werden. In solchen Transistoren durchdringt das elektromagnetische Feld des Gates die Kanäle von drei Seiten, und insgesamt liefern zwei oder drei Kanäle in jedem Transistor den Strom, der für den Betrieb des Ventils erforderlich ist.

/ Samsung Bild

/ Samsung BildBeginnend mit der 3nm-Prozesstechnologie wird Samsung diese Praxis brechen. Das FinFET-Konzept funktioniert nach wie vor nicht mehr. FinFET-Transistorgates sind zu klein und können keine Transistoren schalten. Die Notwendigkeit, die Versorgungsspannung der Transistoren weiter zu reduzieren, wird diese Situation nur verschlimmern. Daher wird für die 3-nm-Prozesstechnologie ein Transistor mit einem GAA-Ring (umlaufendes Gate)

eingeführt .

/ Samsung Bild

/ Samsung BildSamsung gab dem neuen Transistor den Handelsnamen MBCFET (Multi Bridge Channel FET). In der Praxis ist dies die Entwicklung der Idee eines Transistors,

die gemeinsam von Forschern von IBM, Samsung und GlobalFoundries entwickelt wurde. Es wurde angenommen, dass ein Transistor mit ähnlicher Struktur am Übergang zu einer Prozesstechnologie mit 5-nm-Standards beteiligt sein würde. In der Realität wird diese Ventilstruktur jedoch erst mit Beginn der 3-nm-Produktion von Samsung in den Chips erscheinen. Der MBCFET-Transistor besteht aus horizontal übereinander angeordneten Kanälen in Form von Nanoseiten und nicht aus vertikalen Stegen wie beim FinFET. Die Eigenschaften von MBCFET-Transistoren werden bequem gesteuert, indem sowohl die Anzahl der übereinander angeordneten Seiten als auch die Seitenbreite geändert werden. Jede Seite ist ein Kanal. Die Summe dieser Variablen bestimmt, welchen Transistor wir haben: leistungsstark und schnell oder schwach, aber mit geringer Leistung. Es wird mehr als zwei Abstufungen geben - von fünf bis sieben.

/ Samsung Bild

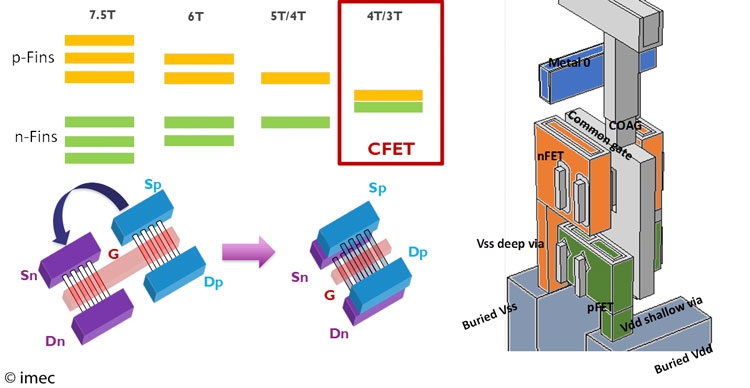

/ Samsung BildDas Interessanteste, um dessen willen dieser Hinweis gestartet wurde, ist, dass der MBCFET-Transistor nur im Rahmen der 3-nm-Prozesstechnologie auftreten kann und ein Prozessprozess mit 2-nm-Standards wiederum Änderungen in der Struktur des Transistors erfordert. Ein solcher neuer Transistor unter dem Namen Forksheet wurde vom belgischen Forschungszentrum Imec vorgeschlagen. Zum ersten Mal

sprachen die Vertreter von Imec in diesem Frühjahr auf einer jährlichen Veranstaltung ausführlich über den Aufbau eines Transistors mit separaten (Nano-) Seiten. Aber du kannst die Nachtigall nicht mit Fabeln füttern. Wir würden es fühlen. Sie können es noch nicht fühlen, aber die Belgier haben eine Simulation des Forksheet-Transistors auf TCAD durchgeführt, die vor drei Tagen

gemeldet wurde.

Bevor wir die Daten betrachten, erklären wir, dass der Forksheet-Transistor eine Modifikation des Transistors mit Nanoseiten ist - derselbe MBCFET oder Gate-All-Around, wenn wir die Begriffe Samsung ignorieren. Die vertikale Shutter-Finne im Forksheet-Transistor ist etwas breiter als die des MBCFET, aber die Nanoseiten der Transistorkanäle sind zweigeteilt und durch eine dielektrische Schicht getrennt. Tatsächlich verwandelt sich ein MBCFET-Transistor mit einem Handgriff in ein komplementäres Transistorpaar aus p- und n-Typ-Transistoren.

Die vorgeschlagene Struktur zerstört eine schwerwiegende Barriere bei der Versiegelung von Transistoren in Form von Komplexität, um p- und n-Transistoren so nahe wie möglich zu bringen und gleichzeitig die gegenseitige negative Beeinflussung der Gates zu vermeiden.

Offensichtlich wird der vorgeschlagene Ansatz die Dichte der Transistoren auf dem Chip erhöhen, aber die Modellierung hat gezeigt, dass sich auch die Leistung und der Energieverbrauch verbessern werden. Durch den Wechsel zu einem Transistor mit separaten Seiten wird die Kristallfläche um bis zu 20% verringert, und durch die Verringerung von Fehlkapazitäten und Leckagen wird die Leistung elektronischer Geräte um bis zu 10% erhöht. Wenn Sie die Frequenz nicht erhöhen, können Sie den Stromverbrauch um bis zu 24% senken.

Auf Lager hat Imec eine weitere

Technologie , die die Dichte von Transistoren weiter erhöhen kann. Es kann sowohl bei der Produktion von 3-nm-Chips als auch bei niedrigeren Produktionsstandards angewendet werden. Die Idee ist, ein komplementäres Transistorpaar übereinander zu bilden. Diese scheinbar einfache Operation verspricht, die Größe sowohl der logischen Standardzelle als auch der SRAM-Zelle um 50% zu reduzieren. Gut entwickelte und teilweise an Modellen getestete Ideen enden hier.

Der Wechsel zu einer 1-nm-Prozesstechnologie erfordert möglicherweise auch eine neue Transistorstruktur. Gleichzeitig muss man bedenken, dass es Ingenieuren oft möglich ist, ihr Vergnügen auszudehnen - sich so etwas auszudenken, um auf alten Krücken einen weiteren Schritt nach vorn zu machen.