Ein Artikel von der Seite des verrückten hausgemachten Ingenieurs Chris Fenton

Lernen Sie den ZedRipper kennen, eine 16-Core-Bestie mit 83 MHz und Z80-Prozessoren, die so portabel wie unpraktisch ist. Dies ist mein letzter Versuch, einen Computer zum Spaß zusammenzubauen und gleichzeitig mehrere Wünsche zu erfüllen:

- Zum Schluss benutze den Riesen-FPGA, der bei mir untätig rumlag.

- Spielen Sie eine alternative Geschichte der Computererstellung und nähern Sie sich dem Thema Multitasking aus der Perspektive des Eisens.

- Stellen Sie einen Computer zusammen, auf dem ich auf dem Weg zur Arbeit im Zug lustige Kurzprogramme schreiben konnte.

- Bauen Sie eine Plattform auf, auf der relativ einfache Experimente mit der Computerarchitektur durchgeführt werden können.

Glamouröse Fotos

Wenn Sie keine Zeit haben, ein Textblatt über unpraktische Computerarchitektur zu lesen ...

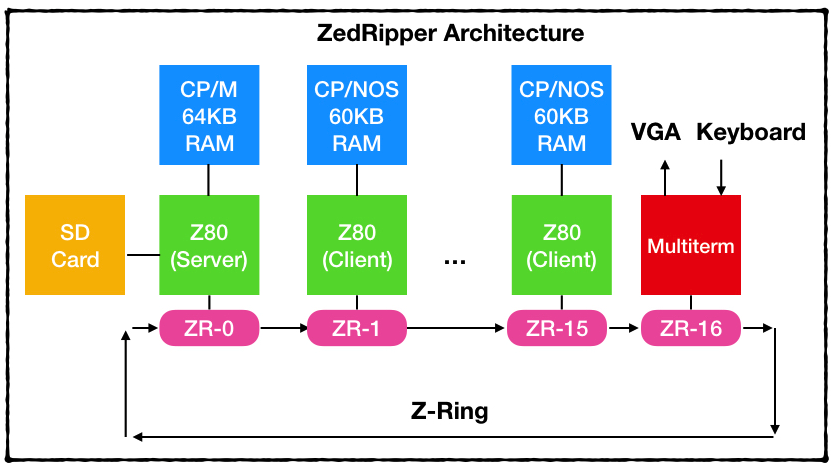

Also, was ist dieses Biest?

ZedRipper ist das Ergebnis eines Versuchs, den coolsten Computer mit CP / M 2.2 zu bauen:

- 16 Z80-Prozessoren arbeiten mit einer Frequenz von 83,33 MHz.

- 64 KB dedizierter Speicher für jeden Z80.

- ANSI-kompatibler Terminalbeschleuniger mit 16 Ausgängen.

- Alle Prozessoren und Geräte sind über ein vollsynchrones unidirektionales Ringnetzwerk mit 83 MHz verbunden.

- 128 MB-Laufwerk auf einer SD-Karte (16 x 8 MB-Laufwerke in CP / M).

- Ein „Server“ -Kern, der in CP / M 2.2 startet und den CP / NET-Dateiserver ausführt (in Turbo Pascal 3 auf dem Computer selbst geschrieben!), Der den gemeinsamen Zugriff auf die SD-Karte ermöglicht.

- 15 "Client" -Kerne, die CP / NOS aus dem ROM starten. Jeder Client hat Zugriff auf ein gemeinsames Repository, und jeder kann beliebige CP / M 2.2-Programme ausführen, ohne mit anderen Kerneln um Ressourcen zu konkurrieren.

Eine andere Straße

Lenken mich Schach und Planetfall von meinem Turbo Pascal-Editor ab?

Lenken mich Schach und Planetfall von meinem Turbo Pascal-Editor ab?Nach meinen Abenteuern mit dem

Portieren von Spielen nach Kaypro hatte ich vor 40 Jahren einen überraschend warmen Eindruck von diesem primitiven Betriebssystem, und ich hatte eine Idee, die ich zu entwickeln entschied: Was wäre, wenn sich die Geschichte in die entgegengesetzte Richtung drehen würde und der PC weiter machen würde Entwicklungspfade mit mehreren CPUs sofort? Sogar in den 1980er Jahren waren die Prozessoren selbst (und bald auch der Arbeitsspeicher) relativ kostengünstig, aber PC-Multitasking basierte ausschließlich auf kürzeren Zeiten, wenn eine große Ressource (Arbeitsspeicher oder CPU) zwischen konkurrierenden Programmen aufgeteilt wurde. Iron konnte dies nicht bewältigen (und es war sehr schwierig, Programme auf Betriebssystemen wie DOS zum richtigen Verhalten zu bringen), bis wir in die Ära der 386er und Computer mit mehr als 4 MB Arbeitsspeicher eintraten.

Während meiner historischen Hobbys mit Computern stieß ich auf etwas für mich sehr Interessantes: In den frühen Entwicklungsstadien unterstützte das

CP / M- Betriebssystem eine "Netzwerk" -Version namens CP / NET. Die meisten Menschen kennen ihre Idee noch heute - ein oder zwei „echte“ Maschinen mit großen Laufwerken und Druckern ins Büro zu stellen, deren Ressourcen zwischen Thin Clients, Terminals mit CPU und RAM geteilt würden. Jeder Benutzer würde so arbeiten, als hätte er einen eigenen Computer mit CP / M und Zugriff auf große Festplatten und Drucker.

Wie bereits erwähnt, waren CPU und RAM (normalerweise hatte der Z80 64 KB DRAM) nicht besonders teuer, aber alle externen Pribluds, die zum Erstellen eines nützlichen Computers (Laufwerke, Drucker, Monitore usw.) erforderlich waren, summierten sich zu den Gesamtkosten. Zu dieser Zeit schien das Hinzufügen mehrerer CPUs / RAMs zu einem Computer ein ziemlich dekadenter Ansatz zu sein, um einem Benutzer mehrere CPUs und RAMs zur Verfügung zu stellen. Sogar CP / M hat es geschafft, die Zeitspannen für MP / M OS zu teilen.

Ich stellte fest, dass Exidy dem am nächsten kam - 1981 veröffentlichten sie ihre Multi-NET 80-Maschine, die das Hinzufügen von bis zu 16 Karten mit jeweils einem Z80 und RAM ermöglichte. Es wurde jedoch für bis zu 16 einzelne Benutzer entwickelt und nicht für die Arbeit eines einzelnen Benutzers, der gleichzeitig 16 Programme gestartet hat.

So nah ...

So nah ...40 Jahre schneller Vorlauf - Transistoren sind tatsächlich im Preis gefallen. Nach der Schließung des Labors habe ich mehrere monströse FPGAs (Stratix IV 530GX) geerbt, und ich dachte, es wäre so interessant, mit einem davon zu arbeiten. Irgendwann stieß ich auf ein sehr interessantes Projekt von Grant Searle

Multi-Comp , und es war ziemlich einfach, eine Arbeitsmaschine mit CP / M und einer CPU zusammenzubauen. Aber ich brauchte mehr. Ich beschloss zu prüfen, ob ich auf CP / M eine Multi-Core-Maschine mit echtem Multitasking erstellen kann - nichts Kniffliges, nur Brute Force.

Wir konfigurieren und starten Software

In diesem Projekt habe ich mich hauptsächlich auf Hardware konzentriert und keine einzige Codezeile in Assembler geschrieben. CPU 0 wird direkt aus dem ROM geladen, das ich Grant entnommen habe, und die verbleibenden Knoten werden aus dem 4-KB-CP / NOS-ROM geladen, das ich aus dem Atari-Simulator entnommen habe.

Beide ROMs warten auf eine Verbindung zu einem seriellen Terminal über eine Standardschnittstelle, während CP / NOS-Clients einen weiteren seriellen Port erwarten, der mit einem Server verbunden ist. Auf so großen FPGAs können Sie ganz einfach Ihre eigene Logik entwerfen. Ich habe meine Adressdecodierungslogik entwickelt, dank derer der Z-Ring für jede CPU bei Bedarf im Adresszuordnungsschema angezeigt wird.

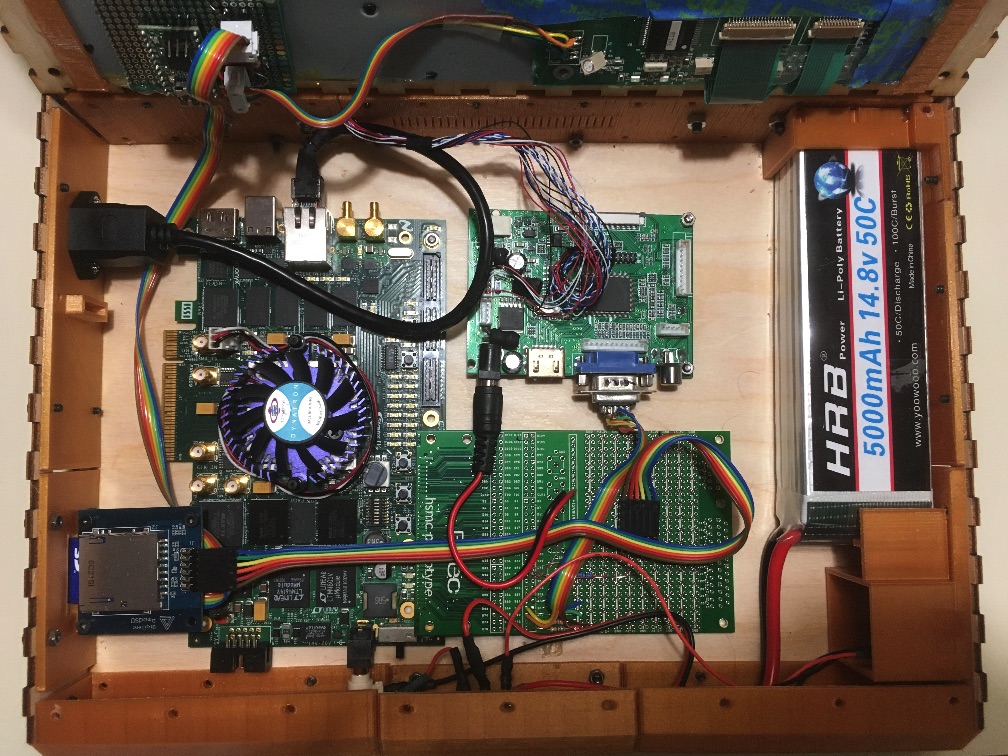

Insides

Das Herzstück des ZedRipper ist eines dieser riesigen Stratix IV 530GX-FPGAs. Die HSMC-Karte wird zum Anzeigen, Empfangen von Daten vom Tastatur-Controller und zum Anschließen an die SD-Karte verwendet. Da die Firmware über Ethernet heruntergeladen wird, befindet sich an der Seite des Gehäuses ein solcher Anschluss sowie ein SD-Kartenadapter und ein Steckplatz für einen externen seriellen Anschluss (noch nicht verwendet).

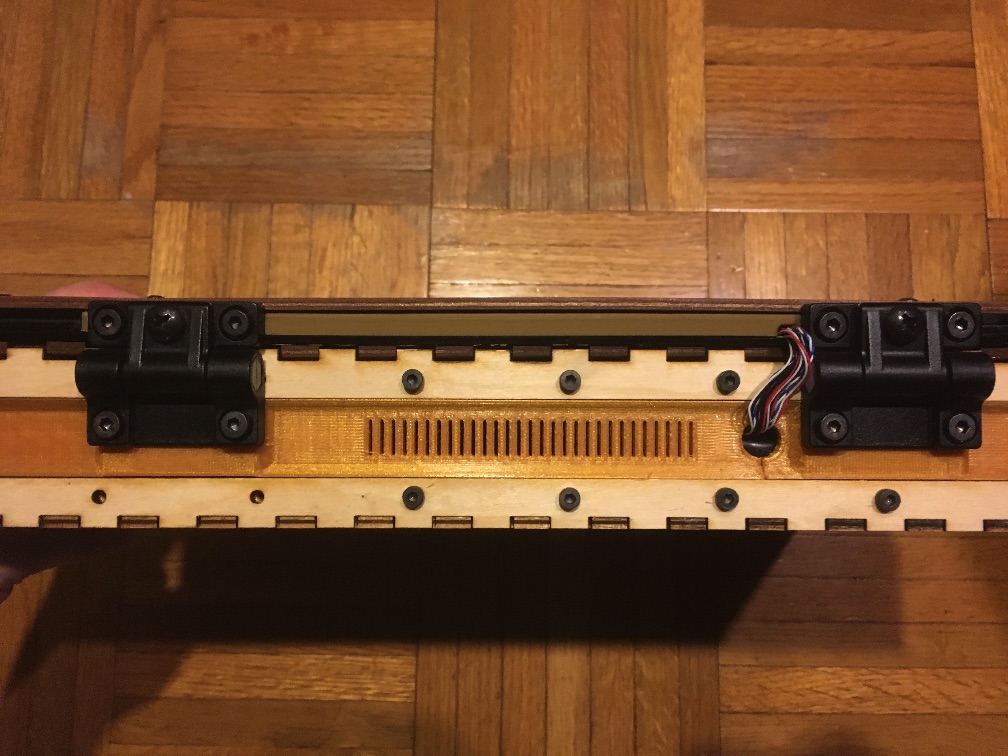

Tastatur und Controller

Tastatur und Loch im Vordergrund, wo später ein Positionierungsgerät installiert wird

Tastatur und Loch im Vordergrund, wo später ein Positionierungsgerät installiert wirdIch hatte eine kompakte PS / 2-Tastatur herumliegen (von einem meiner alten Projekte mit einem Laptop), und ich wollte es an die 2,5-V-E / A meines FPGA anschließen. Ich entschied mich für den einfachen Weg und fügte dem Bundle einen Teensy 2.0-Mikrocontroller hinzu.

Heißkleberregler am unteren Rand der Tastatur

Heißkleberregler am unteren Rand der TastaturDies ermöglichte die Übersetzung von PS / 2 in ASCII sowie die einfache Kennzeichnung einiger zusätzlicher Tasten (F1-F12) in „magische“ Sequenzen von Terminalbefehlen, um den Vorgang zu vereinfachen. Der Controller stellt dann Z80 Byte für UART mit 9600 Baud bereit (unter Verwendung eines einfachen Spannungsteilers, der 5 V auf 2,5 V für FPGA ändert). Angesichts der Tatsache, dass dieses Projekt aus verschiedenen Abfällen zusammengesetzt wurde, die in meiner Werkstatt lagen, war es eine praktische Lösung, die sich in der Arbeit gut bewährt hat.

Anzeige

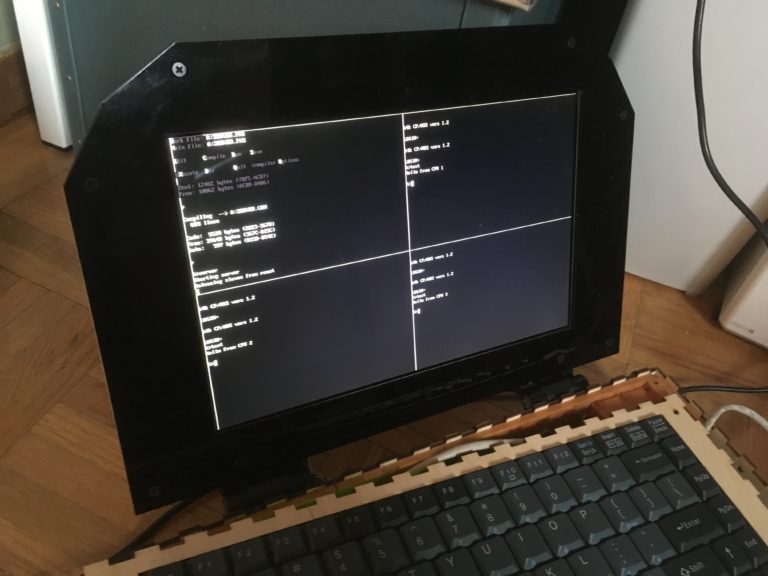

Der Ladebildschirm, der Server wird in der oberen linken Ecke ausgeführt, und drei verschiedene Benutzerprogramme arbeiten auf separaten Kerneln

Der Ladebildschirm, der Server wird in der oberen linken Ecke ausgeführt, und drei verschiedene Benutzerprogramme arbeiten auf separaten KernelnDisplay-Funktionen: 1280 × 800 10,1 ", und es versteht VGA. FPGA verwendet ein einfaches Netzwerk von Widerständen, um bis zu 64 Farben (R2G2B2) zu liefern. Das Display benötigt einen Zeitgeber von 83,33 MHz (1280 × 800 @ 60 Hz), sodass der Einfachheit halber die gesamte Schaltung bei dieser Frequenz arbeitet.

Grants Projekt Multicomp enthielt VHDL-Code für ein einfaches ANSI-kompatibles Terminal. Ich habe seine Logik auf Verilog umgeschrieben und dann einen Videocontroller mit Unterstützung für 16 unabhängige Terminals entwickelt, die über einen Z-Ring-Knoten verbunden sind. Die 1280 × 800-Anzeige wird als Anzeige mit 160 x 50 Zeichen (mit 8 x 16 Zeichen) betrachtet. Jedes Terminal fungiert als 80 x 25-Sprite, das an eine beliebige Stelle auf dem Bildschirm verschoben werden kann (mit einer Prioritätsliste, mit der die Renderreihenfolge des Terminals angepasst wird). Da jedes Terminal unabhängig von den anderen arbeitet, verfügt es über eine eigene Zustandsmaschine mit 2 KB RAM für Zeichen und 2 KB Attributen (zum Speichern von Farbinformationen). Jedes Zeichen unterstützt 4-Bit-Hintergrund- und Zeichenfarben. Da alle Terminals dieselben Einrückungszeichen haben müssen und eine 8x16-Zelle nur ein Zeichen enthalten kann, können alle Terminals dasselbe 2-KB-ROM mit einer Schriftart verwenden. Im Allgemeinen verwendet die Anzeigelogik etwa 66 KB Block-RAM.

Generell bekomme ich für meine CP / M-Terminals einen sehr einfachen Fenstermanager, der hardwaremäßig nahezu vollständig funktioniert. Dies ist einer der reichhaltigsten Bereiche für die Forschung - bisher kann nur die Server-CPU die Terminals neu anordnen, aber ich habe weitreichende Pläne, ein Positionierungsgerät wie eine Maus hinzuzufügen, mit dem Windows-Hardware nur zum Ziehen von Fenstern und Ändern der Priorität von Anzeigen verwendet werden kann.

Da der Terminal-Controller nur einer der Z-Ring-Knoten ist (und die Umleitung dieser Schnittstelle auf einen der Z80-Knoten sehr einfach ist), ist es künftig möglich, ein Vollbild-Terminal 160 x 50 (möglicherweise als Hintergrund) und eine echte Anzeige 1280 x 800 x 64 hinzuzufügen Farben mit schnellem externen SRAM auf der Platine.

Z-Ring

Wie stellt man ein paar Z80 zusammen? Bei meiner Arbeit habe ich fest gelernt, dass es schwierig ist, Netzwerke aufzubauen. Die übergeordneten Ziele dieses Netzwerks waren:

- Einfache Implementierung.

- Einfaches Interface

- Beliebige Erweiterbarkeit.

- Angemessene Leistung.

Wie ich bereits erwähnte, erwarten meine Z80s eine Verbindung zu seriellen Anschlüssen, so dass die Schnittstelle recht einfach zu handhaben war - sie musste als serieller Anschluss getarnt werden! Z-Ring ist im Wesentlichen ein synchrones, unidirektionales Ringnetzwerk, das „Credits“ zur Steuerung des Flusses verwendet. Jeder Knoten verfügt über einen 1-Byte-Eingangspuffer für jeden anderen Knoten im Netzwerk. Nach einem Reset hat jeder Knoten 1 "Guthaben" für jeden verbleibenden Netzwerkknoten. Das Schema ist parametrisiert, daher kann es leicht auf Hunderte von Knoten mit einem sehr geringen Logikaufwand skaliert werden. Heutzutage unterstützt Z-Ring jedoch bis zu 32 Knoten (daher benötigt jeder Knoten einen 32-Byte-Puffer).

Der "Bus" selbst besteht aus einem Gültigkeitsbit, einer "Quell" -ID, einer "Ziel" -ID und einer 1-Byte-Nutzlast (19 Bits). Ich denke, es wäre ziemlich einfach, es mit der TTL-Logik zu implementieren (wenn eine Person 1981 gescheitert wäre und kein FPGA gefunden hätte). Jeder "Knoten" hat 2 Pipelines für Bus-Trigger - 0 und 1 Stufen - und wenn Sie eine Nachricht eingeben, wartet er, bis die 0. Stufe leer ist, und geht dann in die 1. über. Nachrichten werden auf dem Quellknoten eingegeben und durchlaufen den Ring, bis sie das Ziel erreichen. Danach befinden sie sich im entsprechenden Puffer und aktualisieren das Datenbereitschaftsflag. Wenn der empfangende Knoten den Puffer liest, gibt er die ursprüngliche Nachricht erneut ein, die sich weiter um den Ring bewegt, bis sie wieder die Quelle erreicht, und gibt das "Guthaben" zurück. Wenn Sie das Paket an eine nicht vorhandene Adresse senden, wird das Darlehen nach einem vollständigen Umlauf automatisch zurückerstattet.

Da jeder Stopp auf dem Ring aus zwei Förderstufen besteht und kein Gegendruck vorliegt, dauert jede Nachricht nicht mehr als 2 * Zustellzyklen (Anzahl der Knoten). Die aktuelle Implementierung verfügt über 17 Knoten (16 CPU + Display / Tastatur-Controller) und arbeitet mit einem Zeitgeber von 12 ns, sodass die Zustellung einer Nachricht und die Rückgabe eines Darlehens ca. 400 ns dauert. Der Display-Controller kann Datenverkehr mit einer Ankunftsrate senden, sodass jede CPU eine Bandbreite von 2 bis 2,5 MBit / s zu ihrem Terminal hat (der Bus reicht aus, um alle 16 CPUs zu versorgen), was für Terminals ziemlich viel ist.

In der aktuellen Konfiguration funktioniert alles einwandfrei, aber Sie können einige offensichtliche Verbesserungen vornehmen:

- Um die Empfangspuffer zu vertiefen, die den Durchsatz der Knoten erhöhen, gibt es auf dem FPGA viele freie Blöcke von 1 KB RAM, die 32 Knoten mit 32 Credits unterstützen, so dass theoretisch jede CPU den Bus überlasten kann.

- Unterstützung für den Adressmodus hinzufügen. Das Hinzufügen von 16-Bit-Adressen (oder mehr) ermöglicht den direkten Zugriff auf den Speicher (DMA) (und das Hinzufügen von DMA zu jedem Knoten ist einfach). FPGA verfügt über eine enorme Menge zusätzlicher Hardware (einige Megabyte statischer RAM und etwa ein Gigabyte DDR3).

- Fügen Sie Flusskontrolle (und Pufferung) zwischen Knoten hinzu.

Aber das alles kann bis zu besseren Zeiten warten.

Ernährung!

Ein Debug-Board mit FPGA benötigt eine Eingangsspannung von 12 bis 20 V, ein Display 12 V und eine Tastatur und ein Controller 5 V. Es ist praktisch, dass das FPGA über 3,3-, 5- und 12-V-Controller verfügt, an die es sich ganz einfach anschließen lässt FPGA wird direkt von einem Lithium-Polymer-Akku mit 5000 mAh und einer Spannung von 14,4 V mit Strom versorgt und anschließend an alle anderen Geräte verteilt. Eine der Schwierigkeiten bestand darin, dass ich den Laptop nicht jedes Mal zum Aufladen zerlegen wollte, sondern dass der Akku einen normalen +/- Stromanschluss sowie einen „Balancing“ -Anschluss hatte, der mit jeder einzelnen Zelle verbunden war. Meine unvollkommene Lösung ist, dass der Netzschalter die Batterieverbindung zwischen der FPGA-Stromversorgung und dem Ladeanschluss in der Aussparung, die durch eine Schiebeabdeckung verschlossen ist, umschaltet. Es ist nicht sehr praktisch, aber Sie können einfach den Deckel schieben und die Stecker von dort abziehen, um sie ohne Verwendung der Sechskantschlüssel mit dem Ladegerät zu verbinden.

Laden sieht komisch aus

Laden sieht komisch ausIch habe die Batterie nicht gründlich getestet, aber es dauert mindestens 3 Stunden (das ist mehr als genug, um meine Zugfahrten abzudecken). Höchstwahrscheinlich dauert es ungefähr 6 Stunden, ohne den Verbrauch zu optimieren. Die gleichzeitige Verwendung mit dem Aufladen wird nicht unterstützt. Der Laptop wird jedoch so lange mit Akkustrom betrieben, dass dies kein Problem darstellt.

Wohnen

Der Fall des Standard-"Hacker" -Designs ist eine Kombination aus 3-mm-Laserschnittsperrholz und Kunststoff, die auf einem 3D-Drucker gedruckt wurde. Ich habe die Bildschirmscharniere federbelastet, so dass es sich tatsächlich wie ein gewöhnlicher, wenn auch etwas langsamer Laptop anfühlt. Ich wollte es so aussehen lassen wie in den 1980er Jahren, daher ähneln die oberen Ecken des Bildschirms Cray, und der Kunstlederständer ist unter den Handgelenken angebracht. Die Kante des lasergeschnittenen Sperrholzes ist für die Hände sehr unangenehm, so dass dieser Ständer überraschend funktionell war.

Geschwindigkeit

Ich habe keinen einzigen Benchmark speziell für CP / M ausprobiert (ich gehe davon aus, aber ich habe nicht speziell danach gesucht). Da diese Maschine zum Schreiben von Programmen in Turbo Pascal gemacht wurde, habe ich mehrere Mikrotests für die Geschwindigkeit durchgeführt. Es ergaben sich 15-35 K Gleitkommaoperationen pro Sekunde (unter Verwendung des 48-Bit-Real-Typs in TP) und ungefähr 1 Million Ganzzahloperationen pro Sekunde (mit dem 16-Bit-Ganzzahltyp). Nicht schlecht für eine 8-Bit-CPU und eine ausreichend komfortable Programmierumgebung.

Ein interessantes Projekt für die Zukunft könnte die Entwicklung eines Beschleunigers für Gleitkommaoperationen sein.

FPGA-Entsorgung

Die gesamte Logik ist, wie ich bereits sagte, ziemlich leicht und verbraucht nur etwa 7% der Chipressourcen (obwohl 40% des gesamten Block-RAM und 100% des M144k-RAM).

- Kombinierte ALUTs 31.808 / 424.960 (7%)

- Speicher-ALUTs 0 / 212.480 (0%)

- Dedizierte Logikregister 10.231 / 424.960 (2%)

- Logikauslastung 10%

- Gesamtzahl der Register 10231

- Gesamtblockspeicherbits 9.005.056 / 21.233.664 (42%)

- DSP-Block 18-Bit-Elemente 0 / 1.024 (0%)

Zukunftspläne

In meinen unmittelbaren Plänen (dh das Eisen ist bereits in der Werkstatt, Sie müssen nur die Zeit zum Löten finden):

- Alles ausmalen. Der Laptop besteht aus Sperrholz, und ich möchte ihn unbedingt mit etwas bedecken.

- Joystick-Positionierungsgerät Schließen Sie es an den Tastaturcontroller an.

- Batterie-Tracking. Mit ADC auf dem Tastaturcontroller ist es einfach genug, den Akku zu verfolgen, damit ich nachvollziehen kann, auf welcher Höhe der Ladezustand liegt.

- WiFi - Ich habe ESP32 herumliegen, um Zimodem zu starten! Zusammen mit dem Telefon im Zugangspunktmodus sollte dies mir ermöglichen, unterwegs online zu gehen. Es gibt gute Terminalanwendungen für CP / M, aber es wäre schön, etwas wie einen IRC-Client oder einen einfachen Webbrowser zu schreiben. Es ist auch praktisch, das Kermit- Dateiübertragungsprotokoll auf einem modernen Linux-Computer zu verwenden.

- Die von außen zugängliche serielle Schnittstelle für den Anschluss an ein anderes Gerät (ein Stecker wurde bereits dafür aufgedruckt, er muss nur noch angelötet werden).

- LED zeigt den aktuellen Status an. Für ihn gibt es schon ein Loch in der Front - jetzt habe ich vor, es mit dem Zugriffssignal auf die SD-Karte zu verbinden.

Langfristig freue ich mich auf verschiedene Eisenideen, mit denen es Spaß machen wird, zu experimentieren:

- Wie viel können Sie das Z80 übertakten? Der erste Schritt besteht darin, die Prozessorgeschwindigkeit vom Pixel-Timer zu lösen. Es wird jedoch auch interessant sein, moderne Computertechniken auf den Z80 anzuwenden (Pipelines, Registerumbenennung, Verzweigungsvorhersage usw.).

- Es kann interessant sein, spezielle Beschleuniger für Dinge wie Gleitkommaoperationen hinzuzufügen. Es gibt 1024 unbenutzte DSP-Blöcke auf dem Chip, und ich denke, dass niemand versucht hat, einen Beschleuniger für das 48-Bit-Real-Format in TP zu erstellen.

- Vorhandenes Eisen verwenden! Ich habe immer noch eine Menge ungenutzten Speichers, nämlich:

- 512 MB DDR3-SDRAM mit einem 64-Bit-Datenbus

- 128 MB DDR3-SDRAM mit einem 16-Bit-Datenbus

- Zwei 4 MB QDR II + SRAMs mit 18-Bit-Datenbussen

- 64 MB Flash

- 2 MB SSRAM

- Verbessere das Video! Der erste Schritt besteht darin, die Unterstützung für das "Vollbild" -Terminal 160x50 und die Möglichkeit der zweifachen Skalierung auf ein reguläres Terminal 80x25 hinzuzufügen. Bei Verwendung eines externen SSRAM wird einfach der 1280 × 800 @ 6-Bit-Modus hinzugefügt.

- Erweitern Sie die Funktionen des aktuellen Terminals. Ich denke, ich kann die Kompatibilität mit einem Terminal wie ADM-3A (und die Grafikunterstützung), das in Kaypro / 84 verwendet wird, verbessern. Dann habe ich Zugriff auf eine größere Auswahl an Software (und ich muss nicht DD9 portieren).

Zusammenfassung

Bisher hat das Auto nur ein paar Tage funktioniert, aber ich kann sagen, dass ich wirklich alles mag. Der Bildschirm ist schön und klar, die Tastatur ist groß und komfortabel, der Körper ist sperrig, aber er wiegt wenig (und passt in einen Rucksack).

Der Laptop war sogar überraschend ergonomisch für die Arbeit in einem Zug.Ich glaube, ich bin auf dem richtigen Weg. Die Möglichkeit, einen Texteditor in einem Fenster zu öffnen, um Notizen während des Debuggens von TP-Code in einem anderen Fenster zu machen, ist äußerst praktisch (oder die Möglichkeit, Notizen während des Spielens von Zork zu machen!). Es wird angenommen, dass ein solcher Ansatz für die Schaffung kostengünstiger Multitask-Computer auf der Basis von CP / M existieren könnte.Willst du das selbe bauen?

Bisher habe ich keine einfache Möglichkeit, Dateien vom Computer abzurufen, damit der nützlichste Teil der Software (in Turbo Pascal geschriebener CP / Net-Dateiserver) enthalten ist. Bleiben Sie bei uns und bleiben Sie dran (oder schreiben Sie mir eine E-Mail, wenn Sie nicht warten können). Irgendwann werde ich wahrscheinlich dem 21. Jahrhundert beitreten und einen Account bei Github eröffnen. Leider alles auf dieser sehr "Freizeit".