Alexander Kushnerov

18.12.2013

Selbst ein erfahrener Ingenieur kann es manchmal schwierig finden, den Stromkreis so zu verlegen, dass die Leiterbahnen (oder Drähte) den ordnungsgemäßen Betrieb nicht beeinträchtigen. In erster Näherung beeinflussen das Layout und die Anzahl der Knoten, welche Drähte mit jedem Knoten verbunden sind, und die Länge der Drähte nach dem Verzweigen die Qualität der Verdrahtung. Wenn wir die Länge des Kabels als Verzögerung betrachten, hängt der korrekte Betrieb von asynchronen Digitalschaltungen möglicherweise nicht von den Verzögerungen in einigen Kabeln ab. In Zukunft werden wir solche Drähte als sicher und die Verzweigung solcher Drähte als absolut sicher (FGP) bezeichnen. In diesem Artikel werden wir zeigen, wie eine Universalschaltung aus zwölf Transistoren einige Zweige völlig sicher machen kann.

Betrachten Sie das sogenannte Schmetterlingsschema [1], [2] in Abb. Diese Schaltung erzeugt disjunkte Impulse p und q, mit denen Leistungstransistoren gesteuert werden können. Puffer in Abb. 1 zeigt sichere Drähte an. Die Verzögerung aller anderen Drähte wird mit Null angenommen. Die Pause zwischen den Impulsen wird durch die Verzögerungen der Puffer wy und wz eingestellt. In Zukunft werden wir den Puffer nicht mehr verwenden, um die Verzögerung eines Elements anzuzeigen. Drähte und Abzweige in allen Schaltkreisen dieses Artikels wurden in Workcraft auf Sicherheit (Ausgangsbeständigkeit) getestet [3]. Signalübergangsgraphen (STGs) wurden von Schaltkreisen durch Auflösen von CSC-Konflikten erhalten. Die Abbildungen zeigen vereinfachte STGs, bei denen Puffersignale entfernt werden. Zeitdiagramm (TD) in Abb. 1 ist nach dem entsprechenden STG aufgebaut.

Abb. 1. Die "Butterfly" -Schaltung, ihre STG und TD unter der Annahme, dass die Verzögerungen in den Drähten Null sind.

Abb. 1. Die "Butterfly" -Schaltung, ihre STG und TD unter der Annahme, dass die Verzögerungen in den Drähten Null sind.Aus der Theorie [1], [2] ist bekannt, dass die Schaltung des RS-Triggers empfindlich auf Verzögerungen in den Drähten bei der Querkopplung reagiert. Aus diesem Grund sind die Puffer in den Querverbindungen in Abb. 1 fehlt. Somit müssen die beiden Auslöseelemente einen Mindestabstand voneinander haben. Wenn dies schwierig ist, können zwei Elemente durch ein komplexes Element mit Rückmeldung ersetzt werden. Zum Beispiel können die Elemente x und xb in der Schmetterlingsschaltung ersetzt werden, wie in Fig. 4 gezeigt. 2. Außerdem erhalten wir FGP am Ausgang eines komplexen Elements.

Abb. 2. Eine Variante der Schaltung in Abb. 1 und seine STG unter der Annahme, dass die Verzögerungen in den Drähten Null sind.

Abb. 2. Eine Variante der Schaltung in Abb. 1 und seine STG unter der Annahme, dass die Verzögerungen in den Drähten Null sind.Die Implementierung der Schemata in Abb. 1 und Fig. 2 erfordert 16 bzw. 20 Transistoren. Zusätzlich zeigt das Diagramm in Abb. 2 ist langsamer, da die Inverter wb1, wb2 und der Inverter innerhalb des Elements 2 zweimal pro Zyklus ODER-UND schalten müssen. Langsame Leistung ist normalerweise der Preis von FGP. Es gibt jedoch Ausnahmen von dieser Regel. Zum Beispiel in Abb. 3 zeigt ein Schema eines asynchronen Zähltriggers (AST) [4], der zwei FGPs aufweist.

Abb. 3. AST und sein STG unter der Annahme, dass die Verzögerungen in den Drähten Null sind.

Abb. 3. AST und sein STG unter der Annahme, dass die Verzögerungen in den Drähten Null sind.Die Nachteile der Schaltung in Abb. 3 sind eine große Anzahl von Drähten und die Tatsache, dass sich die meisten von ihnen kreuzen. Dies kann das Layout erschweren, insbesondere wenn die Anzahl der Ebenen mit Spuren begrenzt ist oder sie von anderen Verbindungen belegt werden. Daher müssen Sie nach einem Kompromiss zwischen der Anzahl der Drähte, der Anzahl der Transistoren und der Anzahl der FGP suchen. Ein Beispiel für ein solches Kompromissschema mit einem FGP ist der in Abb. 4. Dies ist eine kleine Modifikation der Schaltung aus [5]. Beachten Sie, dass hier, wie im Diagramm in Abb. 2 wird eine gemischte Basis verwendet. Um diesen AST ohne Indikator (XOR auf wi2, wi4 und g5) zu implementieren, werden 26 Transistoren benötigt. Dies sind nur zwei Transistoren mehr als der AST in Abb. 3.

Abb. 4. Kompromittieren Sie AST und seinen STG, wenn die Verzögerungen in den Drähten Null sind.

Abb. 4. Kompromittieren Sie AST und seinen STG, wenn die Verzögerungen in den Drähten Null sind.Beachten Sie, dass alle Elemente mit Rückmeldung in Abb. 2 und Abb. 4 sind Spezialfälle eines generalisierten C-Elements (gC). Es ist gegeben als:

wo

und

Erfüllen Installations- und Rücksetzfunktionen die Bedingung?

. Sonderfälle des gC-Elements sind auch NCL-Elemente, die in Schemata zur Datenverarbeitung verwendet werden. Beachten Sie, dass das größte NCL-Element vier Eingänge hat und auf 28 Transistoren implementiert ist [7]. Dies kann durch die Tatsache erklärt werden, dass bei einer größeren Anzahl von Transistoren die Drähte relativ lang werden und die Verzögerung in ihnen den Betrieb des Elements zu beeinflussen beginnt.

Betrachten Sie die in Abb. 5. Es implementiert die Funktion von fünf Variablen [8], [9]

. Tabelle 1 zeigt die Funktionen SDNF und SKNF

und seine Doppelfunktion

. Aus dieser Tabelle ist ersichtlich, dass durch Vertauschen

und

in

wir bekommen

umgekehrt. Für den Fall

erhalten wir eine Self-Dual-Funktion

.

Abb. 5. Ein Schema, das die Funktion von fünf Variablen implementiert.

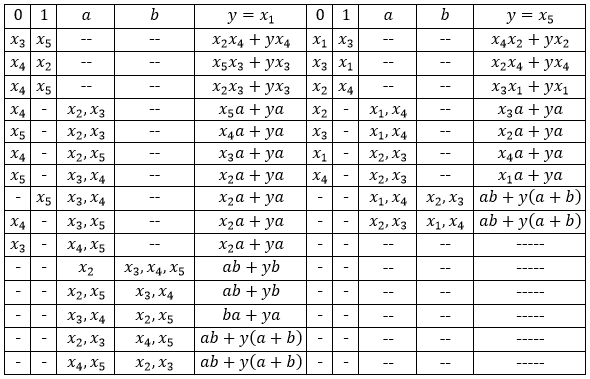

Abb. 5. Ein Schema, das die Funktion von fünf Variablen implementiert.Tabelle 1. Formen logischer Funktionen für die Schaltung in Abb. 5.

Beachten Sie das

bedeutet, dass die entsprechenden vier Transistoren gleichzeitig geschaltet werden müssen. Selbst wenn die Drähte nach dem Verzweigen y die gleiche Verzögerung haben, reicht dies nicht aus, da das Schaltmoment des Transistors durch die Spannung an seinem Gate bestimmt wird. Unter diesem Gesichtspunkt ist die Analyse der Schaltung in Fig. 5 wurde in [10] gemacht. Diese Analyse ist jedoch nicht vollständig, da nur die Implementierung eines C-Elements mit zwei Eingängen in Betracht gezogen wurde. Um eine vollständige Analyse durchführen zu können, müssen Sie zunächst alle Optionen zum Kombinieren von Eingaben oder formal alle Funktionen einer kleineren Anzahl von Variablen finden, die abgerufen werden können

. Eine solche Suche wurde in etwas vereinfachter Form durchgeführt und die Ergebnisse sind im Anhang aufgeführt. Die meisten Funktionen gibt es in verschiedenen Varianten. Aus ihnen müssen diejenigen ausgewählt werden, die wettbewerbsfreie Regelungen vorsehen [11]. Alle erhaltenen Funktionen, die Anzahl ihrer Varianten und die Nummer der entsprechenden Tabelle im Anhang sind in Tabelle 2 angegeben. Die mit einem Sternchen versehenen Nummern bezeichnen Doppelfunktionen.

Tabelle 2. Die von der Schaltung in Abb. 5.

Die Funktionen 2 und 2 *, 5 und 5 *, 7 und 7 * sind selbstverdoppelt, und die Funktion 4 kann durch Vertauschen von a und c aus der Funktion 4 * erhalten werden. Beachten Sie, dass zusätzlich zu Funktion 6 * alle anderen Funktionen Schwellenwerte sind. Dies kann durch die Tatsache erklärt werden, dass

ist isotonisch (positive Einheit) und die Tatsache, dass für vier oder weniger Variablen die isotonischen Funktionen mit der Pseudoschwelle übereinstimmen [12]. Die Frage, welche Optionen für die Funktionen 1 *, 3 * und 6 * in diesem Artikel zur Verfügung stehen, bleibt offen.

Betrachten Sie als Beispiel den Fall der Funktionen 2 und 2 *. Gemäß einer der Optionen (Tabelle P3 im Anhang)

und

. Lass den Weg raus

vom eingang getrennt

und das Signal vom Wechselrichtereingang entfernen lassen. Auf diese Weise können Sie einen in Abb. 6. Die Elemente in dieser Zelle sind unterschiedlich, aber aufgrund der Tatsache, dass die Eingaben kombiniert sind, implementieren beide dieselbe Self-Dual-Funktion. Es ist zu beachten, dass die vernetzten Elemente in den Schaltkreisen in Abb. 1, in Abb. 3 und in Abb. 6 sind Spezialfälle der Grundkonstruktion für die perfekte Umsetzung [2]. Es muss also Regeln geben, um grundlegende Entwurfsschaltungen in gC-Elementschaltungen umzuwandeln und umgekehrt.

Abb. 6. Verteiler für Zellförderer.

Abb. 6. Verteiler für Zellförderer.Aus technologischer Sicht sollten Transistoren auf Polysiliciumbussen "aufgereiht" werden. Eine solche Implementierung der Schaltung in Fig. 5 ist in [14] angegeben. Zur Einstellung der Ausgangszustände können p-MOS- und n-MOS-Transistoren verwendet werden, die im Wechselrichter einen Spannungsteiler mit Transistoren erzeugen. Die Störfestigkeit von Stromkreisen kann mit Hilfe bestimmter STG-Transformationen erhöht werden [15].

Danksagung

Die Autorin dankt Svetlana Frolova (OmSU) für das Scannen des Artikels [1] und Sergey Bystrov für die Inspiration.

App

MuPAD wurde verwendet, um die in diesem Abschnitt dargestellten Ergebnisse zu erhalten. Lassen Sie den Ausgang y nur mit einem der Eingänge verbunden sein. Tabelle A1 zeigt dies in diesem Fall

. Um Funktionen für welche zu bekommen

können Sie entweder einige Variablen kombinieren oder ihnen Konstanten zuweisen. Die Funktionen für den Fall der Kombination zweier Variablen sind in Tabelle A2 angegeben. Andere Möglichkeiten gibt es nicht

. Da die ersten vier Funktionen in Tabelle A1 bis zu einer Permutation der Variablen zusammenfallen, betrachten wir nur die erste und die fünfte. Fälle

und

nicht interessant, da wir im ersten Fall nur das gC-Element zurücksetzen können, aber es nicht installieren können, und im zweiten Fall - umgekehrt. Die Manipulationen mit den Variablen ermöglichten es, die Funktionen von vier und drei Variablen, die in Tabelle P3 bzw. Tabelle P4 angegeben sind, aus der Tabelle P1 zu erhalten.

Tabelle A1. Funktionen von fünf Variablen.

Tabelle A2. Funktionen von vier Variablen.

Tabelle P3. Funktionen von vier Variablen aus Tabelle A1.

Tisch A4. Die Funktionen der drei Variablen ergeben sich aus Tabelle A1.

Literatur

[1] V. I. Varshavsky, M. A. Kishinev, A. R. Taubin und B. S. Zirlin, „Analysis of asynchronous logic circuit. II. Erreichbarkeit von Betriebszuständen und die Auswirkung von Verzögerungen bei Drähten “, so Izv. Akademie der Wissenschaften der UdSSR. Technische Kybernetik, nein. 4, pp. 84-97, 1982.

[2] Varshavsky, V. I. (Hrsg.), Automatic Control of Asynchronous Processes in Computern und diskreten Systemen, Nauka, 1986.

[3]

workcraft.org .

[4] RC Todd, "Logiksystem". Patent US3609569, 28. September 1971.

[5] EA Vittoz, „Frequenzteilungslogikstruktur“. Patent US3829714, 13. August 1974.

[6] J. Cortadella, M. Kishinevsky, A. Kondratyev, L. Lavagno und A. Yakovlev, Logiksynthese für asynchrone Steuerungen und Schnittstellen, Springer, 2002.

[7] A. Kondratyev, „Asynchroner Fluss mit mehreren Schienen und Abschlusserkennung sowie System und Verfahren zu dessen Entwurf“. Patent US6526542, 25. Februar 2003.

[8] JJ Gibson, "Logikschaltungen, die Feldeffekttransistoren verwenden." Patent US3439185, 15. April 1969.

[9] R. Miller, Theorie der Schaltkreise. Band I. Kombinationsschemata, Wissenschaft, 1970.

[10] K. van Berkel, "Vorsicht vor der isochronen Gabel", Integration, vol. 13, nein. 2, pp. 103-128, 1992.

[11] P. Kudva, G. Gopalakrishnan, H. Jacobson und SM Nowick, "Synthese von gefahrlosen kundenspezifischen CMOS-Komplex-Gate-Netzwerken unter Mehrfacheingangsänderungen", in Design Automation Conf., 1996.

[12] GW Fagerlin, Aufzählung von pseudotrennbaren Funktionen von fünf Variablen. M.Sc. Diplomarbeit, Universität von Illinois, 1968.

[13] V. I. Varshavsky, A. Yu. Kondratiev, N. M. Kravchenko und B. S. Tsirlin, „Asynchroner Verteiler“. Patent SU1598142, 07/10 1990.

[14] SW Cheng, "H-Tree CMOS Logic Circuit" in IEEE Conf. über Elektronik, Schaltungen und Systeme, 2008.

[15] A. Taubin, A. Kondratyev, J. Cortadella und L. Lavagno, "Verhaltenstransformationen zur Erhöhung der Störfestigkeit in asynchronen Spezifikationen", in IEEE Symp. auf Async. Schaltungen und Systeme, 1999.