Dies ist der zweite Teil des Artikels über die Geschichte der Mikroprozessoren für Weltraumanwendungen. Der erste Teil ist

da . Darin untersuchten wir am Beispiel amerikanischer und europäischer Mikroschaltungen die Entwicklung strahlungsresistenter Chips von den ersten Einkristallprozessoren bis zum Ende des zweitausendsten, als die Entwurfsstandards für Weltraumentwicklungen nahe bei 100 nm lagen.

Der nächste große Schritt zur Sicherstellung der Strahlungsbeständigkeit erfolgte mit dem Übergang auf unter 100 nm, bei dem fast jede neue Generation von Technologien neue Fragen aufwirft: Änderung der Materialien, Änderung der Topologieanforderungen, Erhöhung der statischen Leistung (Undichtigkeiten ohne Strahlung, die unter einer Dosis noch schlimmer werden) Die Bedeutung von Einzeleffekten, die sich in mehrere verwandeln, nimmt weiter zu. Diese Aufgaben erforderten die Entwicklung neuer Ansätze und überraschenderweise eine teilweise Rückkehr zu den alten, da einige der Dinge, die sich bei den Standards von 1–0,18 μm als ausgezeichnet erwiesen haben, nicht bei feineren Standards funktionieren. Beispielsweise ist es in solchen Technologien verboten, Ringtransistoren herzustellen, die von Designern strahlungsresistenter Chips geliebt werden, um die Ausbeute zu erhöhen. Ich werde erzählen, wie Designer mit dem Beispiel Russland mit neuen Herausforderungen umgehen - und gleichzeitig die Leistungen unserer Landsleute mit dem Erfolg ausländischer Kollegen vergleichen und aufzeigen, was auf absehbare Zeit zu erwarten ist.

Moderne - das Beispiel Russlands

Ich habe Russland gewählt, um die aktuelle Phase zu veranschaulichen, nicht weil die russischen Entwicklungen auf globaler Ebene auffallen, sondern weil es keinen Sinn macht, über etwas Älteres zu schreiben. Es gab viele coole Mikroschaltungen in der UdSSR, aber alle Informationen zu Produkten mit doppeltem Verwendungszweck wurden klassifiziert, und jetzt gibt es nur noch Fahrräder der Form ohne Zulassungsformular: „Nach dem Unfall von Tschernobyl kam Gorbatschow persönlich zu den Roboterentwicklern, um sich mit den Trümmern zu befassen, und brachte einen strahlenden BM6-Mikroprozessor mit.“ (Tatsächlich enthält die Beschreibung nicht "xxxxxBM6", sondern "1806BM2" die Schlüsselwörter "Aufrechterhaltung der Funktionsfähigkeit in einem breiten Bereich mechanischer, klimatischer und

anderer Faktoren".) Es gibt zufällige Kleinigkeiten: In der Serie von 1839 gibt es nach verfügbaren Interviews mit Entwicklern, die für industrielle Zwecke erstellt wurden, einen Chip N1839VZh2 - ein Abstimmungselement. Bei herkömmlichen Computern wird das Mehrheitselement für nichts benötigt, aber wenn Sie ein wenig googeln, können Sie feststellen, dass die 1839-Serie Bordcomputer der GLONASS-M-Satelliten sind. Schade, dass eine solche Datenmenge kein Schreiben zulässt. Darüber hinaus war die UdSSR zum Zeitpunkt des Aufkommens strahlender Mikroprozessoren bereits fest auf dem Weg, die Entwicklungen des Westens nachzubilden. Besondere Innovationen sind daher nach wie vor nicht zu erwarten.

Die neunziger Jahre in der Mikroelektronik waren geprägt vom Überleben und Auspressen der letzten Säfte aus dem sowjetischen Erbe. Eine bedingte Wende fand 2003 statt, die sich als ereignisreich herausstellte: Am NIISI RAS wurde eine eigene Fabrik mit Designstandards von 500 nm in Betrieb genommen, die ersten Prozessoren der Multicor-Familie gingen in die Angstrem-Serie über, in der das Unternehmen Digital Solutions gegründet wurde Zuvor eröffnete ein Distributor von Milandre ein Designzentrum. Dann folgte das Bundeszielprogramm „Entwicklung der elektronischen Komponentenbasis und der Funkelektronik“ für den Zeitraum 2008-2015, mit dem die festgelegten Ziele (45 nm bis 2015, Umsatz von 300 Milliarden Rubel usw. usw.) jedoch noch nicht erreicht wurden es geschafft, die russische Mikroelektronik ernsthaft zu unterstützen. Derzeit sind in Russland etwa 150 bis 200 Designzentren an der Entwicklung integrierter Schaltkreise beteiligt, von Giganten wie Micron bis hin zu Teams von fünf bis sechs Personen, die sich mit Nischensachen befassen. Die überwiegende Mehrheit dieser Teams arbeitet irgendwie mit Regierungsaufträgen und stellt Produkte mit doppeltem Verwendungszweck her. Darüber hinaus war das Jahrzehnt zwischen 2003 und 2014 nicht nur von der Entwicklung neuer russischer Mikroschaltungen und dem Versuch geprägt, die bereits katastrophale Lücke zu ausländischen Herstellern zu schließen. Eine schwierigere Aufgabe als die Entwicklung neuer Mikroschaltungen war es, die Systemhersteller davon zu überzeugen, mit ihrer Anwendung zu beginnen. Nachdem der sowjetische Rückstand aufgebraucht war, setzten die meisten Systemtechniker verstärkt auf importierte Komponenten, die besser hergestellt, besser dokumentiert, zuverlässiger und zugänglicher waren - im Allgemeinen gab es wirklich keinen Grund, etwas anderes zu tun. Weiter - ein Teufelskreis aus Abwärtskompatibilität und Wiederverwendung des vorhandenen Rückstands, dank dem die verschärften inländischen Entwicklungen weiterhin über Bord blieben. Fairerweise gab und gibt es Unternehmen unter den Herstellern von Bordfunkgeräten, die grundsätzlich und konsequent mit einheimischen Entwicklern von elektronischen Bauteilen zusammenarbeiten. Im Allgemeinen sah die Situation in der Branche jedoch so aus:

Ein Zitat aus einem Interview mit Nikolay Testoedov, Direktor des nach Reshetnev benannten größten russischen Raumfahrzeugherstellers ISS:

- Verfügt der militärische Kommunikationssatellit Blagovest über einen großen Anteil ausländischer Komponenten?

- Dort war das Verhältnis auch nicht sehr gut, da wir bis 2014, als es keine Risiken oder Einschränkungen gab , eine große Anzahl ausländischer Komponenten gekauft haben. Wichtiger war der Zeitpunkt der Satellitenerstellung für das Verteidigungsministerium.

Es scheint, dass ich etwas in der Definition des Wortes "Risiko" nicht verstehe. Sobald Sie in Militärfahrzeugen importierte Komponenten verwenden können, können wir davon ausgehen, dass die „Lesezeichen“ in den Mikrokreisen entweder nicht vorhanden sind oder während des Startvorgangs aufgrund von Überlastung abfallen.

Eine scharfe Veränderung war 2014 zu verzeichnen, als aufgrund von Sanktionen gute importierte Mikrochips mit doppeltem Verwendungszweck unerwartet nicht mehr erhältlich waren. Anscheinend war hier ein großartiger Moment, um sich zusammenzutun und die heimischen Entwicklungen voranzutreiben. Stattdessen fiel die russische Mikroelektronik wieder auf die rutschigen Schienen des Kopierens oder, wie sie jetzt sagen, der Importsubstitution. Ich war jedoch zu hinreißend von den Texten, also lassen Sie es uns noch hinzufügen, bevor wir uns die Konstruktionsstandards für Sub-100-Nanometer ansehen, und kurz den Stand der Dinge in russischen Weltraummikroprozessoren und Mikrocontrollern auf der Grundlage der Ergebnisse von zehn Jahren Entwicklung und fünf Jahren Importsubstitution.

Der Zoo

Während in den USA de facto ein Machtmonopol besteht und in Europa - SPARC - in Russland alle Blumen auf allen Architekturen blühten.

- ARM : Drei Modelle von strahlungsresistenten Mikrocontrollern auf Basis von Cortex-M0- und Cortex-M4F-Kernen werden von Milander hergestellt, ein weiteres Cortex-M0 ist die Allianz von Angstrem und Digital Solutions und drei weitere Cortex-M4F sind NIIIS.

- MIPS : „MIPS-kompatible“ RISCore32-Kerne steuern vier heterogene, strahlungsresistente Multi-Board-Prozessoren, die von Elvis SPC entwickelt wurden. "MIPS-ähnliche" KOMDIV-Kernel befinden sich in der Entwicklung von NIIISI, NIIIS und NIIMA "Progress".

- SPARC : der Hauptauftragnehmer für die Entwicklung des russischen LEON4 (1906MB016) - Voronezh NIIET. Interessanterweise hat das Moskauer Zentrum für SPARC-Technologien (ICST) nichts damit zu tun. Anscheinend hat sich Voronezhs Erfahrung in der Entwicklung von strahlungsresistenten Chips als wichtiger erwiesen.

- AMCS-96 : Im Allgemeinen ist der MCS-96 eine 16-Bit-Architektur, aber die düsteren Voronezh-Genies von NIIET haben eine 32-Bit-Erweiterung für ihn erstellt und einen strahlenden Mikrocontroller darauf montiert.

- PowerPC (fast da): Es gibt einen Chip aus dem STC „Module“, der keinen deklarierten Widerstand hat, aber für „On-Board-Equipment“ ausgelegt ist. Anscheinend für die Avionik.

Darüber hinaus gibt es mehrere 8- und 16-Bit-Mikrocontroller, eine Auswahl an DSP / VLIW (eigene und fremde „Analoga“) und fast alles: Speicher, BMC, FPGA, FPAA, ADC, DAC, Mikrowelle, diskrete Geräte. Es gibt einige Mikroschaltungen für Weltraumanwendungen für fast jeden Geschmack - aber die Tatsache ist, dass wir keine brauchen, sondern wettbewerbsfähige, gut dokumentierte und gut unterstützte, und mit dem zweiten und dritten Punkt hatten die russischen Hersteller traditionell alles (und es gibt, was schon da ist) schlecht.

Abbildung 11. Noch eine Bemerkung zur Frage der Vielfalt der inländischen Mikroprozessoren: So sieht ein „importsubstituiertes“ Prozessormodul normalerweise aus. Wir schwenkten die Flagge "Wir haben einen inländischen Prozessor" und machten dann im normalen Modus weiter. Das gleiche Foto kann im Prinzip als Beispiel dafür dienen, wie viel alles importiert werden muss.

Digit ExkursDesignstandards sind eine hervorragende Marketingkennzahl, die nicht viel mit der tatsächlichen Größe von Transistoren zu tun hat und für eine begrenzte Anzahl von Anwendungen von Bedeutung ist, darunter Datenverarbeitung, Speicher mit hoher Kapazität und FPGA, bei denen viele Metalle und Transistoren für den Anschluss von Rechnereinheiten benötigt werden. In allen anderen Anwendungen sind Designstandards nicht so kritisch: Moderne kommerzielle Mikrocontroller werden nach den Standards von 180-90 nm und Leistungsmikroschaltungen von 180-600 nm oder mehr hergestellt. Die Wahl der Technologie hängt von vielen Faktoren ab, vor allem von den Aufgaben, die gelöst werden müssen. Dies gilt auch für Weltraum-Mikroschaltungen, und trotz des wachsenden Umfangs der Informationsverarbeitung an Bord beschäftigt sich ein erheblicher Teil der Mikroschaltungen mit ganz anderen Dingen - Steuerung von Aktoren, Telemetrie, Energieumwandlung, Funkkommunikation - und erfordert daher nicht die neuesten Designstandards.

Wenn Sie Chips im Ausland produzieren, dann gibt es im Moment für Produkte, für die Sie nicht den doppelten Verwendungszweck deklarieren, keine Risiken, keine Einschränkungen , und Sie können mit allem arbeiten. Für die Produktion in Russland stehen jetzt Technologien mit Designstandards bis zu 90 nm zur Verfügung. Die „Arbeitspferde“ für die strahlungsresistenten Chips der meisten russischen Entwickler sind die 180-nm-Mikron-Volumentechnologie und ihr eigenes 240-nm-SOI-Verfahren. Die Fabriken sind jedoch auch voller Probleme mit den Sanktionen aufgrund importierter Vorräte und Ausrüstungsgegenstände, aber dies ist eine andere lange und traurige Geschichte.

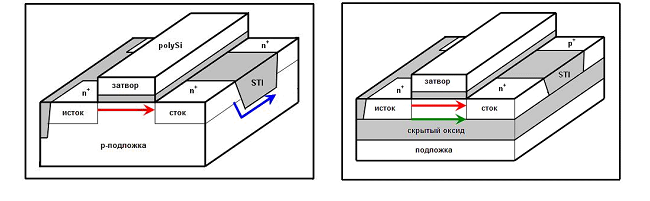

Figure 12. Vergleich des Auftretens von Leckströmen in Volumen- und SOI-MOS-Transistoren. Leckagen sind die Hauptursache für parametrische Fehler, die durch eine volle Strahlungsdosis verursacht werden. Die Abbildung zeigt deutlich, dass die SOI nicht alle Probleme mit dem Strahlungswiderstand löst, aber das grundsätzliche Fehlen eines Thyristoreffekts aufgrund der vollständigen Isolierung jedes Transistors erleichtert Entwicklern das Leben, für die viele von ihnen die SOI sehr lieben.

Da es absolut unmöglich ist, alle in Russland ohne Strahlenresistenz zu erwähnen (und sie geben nicht an jeder Ecke Informationen über die Entwicklungen preis), möchte ich kurz auf drei Unternehmen eingehen, die sich nicht ab und zu, sondern systematisch und systematisch mit Weltraummikroschaltungen befassen Natürlich beschäftigen sie sich mit Mikroprozessoren und Mikrocontrollern. Diese Unternehmen sind Elvis, Milander und NIISI. Ich würde gerne ausführlich über die Entwicklung von NIIET berichten, aber hinsichtlich der Methoden zum Schutz vor Strahlung stellte sich heraus, dass es schwierig war, etwas Spezifischeres zu finden als allgemeine Wörter wie „spezielle strukturelle und schaltungstechnische Lösungen, die im Mikrocontroller implementiert sind und dessen stabilen Betrieb auf der Ebene der akkumulierten Dosis gewährleisten mindestens 250 Crad und linearer Energieverlust (TZZ) bis zu 60 MeV V cm2 / mg “. Die Ausnahme ist ihr LEON, aber alles ist wie bei jedem anderen LEON-FT - Dreifach-Trigger und rauschresistente Codierung im Speicher.

JSC SPC "Elvis"

Das Unternehmen Elvis entwickelt seit Anfang der 2000er Jahre die Multicor-Plattform, die eine Kombination aus RISC-Steuerungskern und DSP auf einem Chip darstellt. Sie begannen ihre systemische Arbeit mit der Sicherstellung der Strahlenresistenz ungefähr zur gleichen Zeit, zusammen mit der Abteilung für Elektronik am MEPhI, wobei sie zunächst ausländische Technologien einsetzten. Nach dem Erscheinen der 180-nm-Technologie von Micron wurde Elvis einer der ersten externen Kunden, der eine strahlende Bibliothek von Logikgattern und eine Reihe von IP-Blöcken für die Erstellung von Systemen auf einem Chip entwickelte. In den Beschreibungen der meisten Mikroschaltungen

der Multibort-

Plattform (der strahlenden Version von Multicore) steht die Aufschrift „Die Mikroschaltung wurde auf dem Territorium der Russischen Föderation entwickelt und hergestellt.“ Der Chipsatz wurde für den Aufbau von On-Board-Datennetzen gemäß SpaceWire- und SpaceFibre-Standards entwickelt und umfasst Prozessoren, DSP, Speicher und PLL und schaltet.

Elvis war von Anfang an aktiv an der Schaffung und Entwicklung des europäischen Standards für die Datenübertragung an Bord von SpaceWire-Raumfahrzeugen beteiligt (die Amerikaner verwenden ihren eigenen Standard - RapidIO), nahm an den Sitzungen der internationalen Arbeitsgruppe teil und war der Haupttreiber für die Umsetzung des noch schnelleren SpaceFiber-Standards.

Abbildung 13. Blockdiagramm des 1892VM206-Prozessors. Die Betriebsfrequenz des RISC-Kerns beträgt 120 MHz, die DSP-Kerne 140 MHz, vier SpaceWire-Ports haben jeweils 300 Mbit / s, zwei SpaceFibre-Ports 1,25 Gbit / s und dann gibt es verschiedene Kleinigkeiten.

Die Ausführung auf unserer eigenen freudenresistenten Bibliothek in allen Kreisläufen wird als Hauptweg zur Erzielung der Strahlenresistenz angegeben. In den Beschreibungen auf der offiziellen Website finden sich nur wenige Details zu einigen architektonischen Techniken, und die Suche nach Veröffentlichungen hat das Bild nicht klarer gemacht, da Elvis nur wenig und hauptsächlich zu anderen Themen veröffentlicht wird. Für alle Prozessoren wird die Hamming-Codierung des gesamten Speichers deklariert, und in einem der Chips gibt es eine dreifache Reservierung der Registerdatei und des Taktbaums. In Bezug auf die Vollständigkeit dieser Informationen mit gesunder Skepsis nehmen wir an, dass die Architekturverteidigung in den Multiborts etwas weniger entwickelt ist als in LEON-FT.

JSC PKK "Milander"

Ein anderer Hersteller, der sich viel mit regenbeständigen Mikroschaltungen beschäftigt, ist Milander. Die meisten ihrer

freude-resistenten Chips sind irgendwie für On-Board-Telemetriesysteme konzipiert - das sind Signalverarbeitungs-Chips von Sensoren, analogen und digitalen Schaltern, ADCs, Speichern und natürlich drei Mikrocontrollern, an denen wir interessiert sind. Genauer gesagt, nicht drei, sondern zweieinhalb, denn der 1986BE8T und der 1986BE81T verfügen beide über ARM Cortex-M4F-Kerne, identische Peripheriesätze und unterscheiden sich nur in der Art des Programmspeichers - ROM im ersten Fall und SRAM im zweiten Fall. Angenommen, die SRAM-Variante wird tatsächlich zum Debuggen der ROM-Variante benötigt. 1923014 ist mit einem bescheideneren ARM Cortex-M0-Kern ausgestattet und Teil des Chipsatzes für die Organisation eines Mehrkanalsensorsystems. Dieser Chip ist kein Mikrocontroller im üblichen Sinne, sondern ein spezialisierter Controller, der für eine bestimmte Anwendung entwickelt wurde.

In den Spezifikationen für 1986BE8T und 1986BE81T (sie haben eine gemeinsame) finden Sie eine Beschreibung des Controllers für die Verarbeitung von Fehlerereignissen, Fehlern und Fehlern, einschließlich unter anderem der Funktionalität zum Parieren einzelner Fehler, ähnlich der oben beschriebenen, die auch den ERC32-Prozessor verwendet eine detaillierte Beschreibung der Funktionsweise der fehlerkorrigierenden Codierung (SECDED Hamming Code) in verschiedenen Speichertypen. Ich konnte keine offenen Informationen zum Beispiel über die dreifache Reservierung von Triggern oder einen Uhrenbaum finden. Nehmen wir also an, dass aus Sicht der architektonischen Fehlertoleranz 1986 19868 zwischen ERC32 und LEON-FT liegt.

Figure 14. Querschnitt einer SOI-BCD mit einem Hochspannungs-LDMOS-Transistor in einer isolierten TascheDie technologische Basis für die meisten strahlungsresistenten Milander-Chips bilden Bibliotheken und ein proprietäres IP-Set mit 180-nm-BCD-SOI-Prozesstechnologie aus dem deutschen Werk XFAB. Diese Technologie hat im Gegensatz zu herkömmlicher SOI eine dicke Siliziuminstrumentenschicht (in der Größenordnung von einem Mikron) und verhält sich in den meisten Fällen wie eine herkömmliche Massentechnologie. Das Vorhandensein von latentem Oxid ermöglicht es, die dielektrische Isolation der Elemente voneinander zu organisieren und somit die Abwesenheit eines Thyristoreffekts zu gewährleisten, und die Tatsache, dass es sich in großer Tiefe befindet, ermöglicht es Ihnen, sich keine Sorgen über Undichtigkeiten an der Grenzfläche von Silizium und einem verborgenen Dielektrikum zu machen, die den Dosiswiderstand der herkömmlichen SOI-Technologie verringern.

Abbildung 15. Vergleich zweier OR-Elemente.

Die Abbildung zeigt zwei identische Logikelemente (ODER mit zwei Eingängen) aus den Milander-Bibliotheken, die mit verschiedenen Methoden zur Erhöhung des Strahlungswiderstands hergestellt wurden. Links sehen Sie Ring-N-Kanal-Transistoren, die den Transistorverlust vollständig neutralisieren. Eine solche radikale Maßnahme ist jedoch oftmals zu groß, da herkömmliche Lineartransistoren (manchmal mit geringfügigen Änderungen) für mäßige Strahlungsdosen ausreichen und aufgrund ihrer Anwendung ein ausreichender Widerstand bei kleinerer Fläche und geringerem Energieverbrauch erzielt werden kann - was in der Abbildung deutlich gezeigt wird.

Ein wichtiges Merkmal der von Milander gewählten Technologie ist das Vorhandensein von Transistoren und anderen Elementen, die für den Betrieb mit hohen Spannungen bis zu 200 V ausgelegt sind. Durch die Integration von digitalen Logik- und Leistungsbauelementen auf einem einzigen Chip können hocheffiziente DC / DC-Wandler, Schlüsseltreiber und Mikrocontroller mit integriertem Prozessor erstellt werden Fahrer und viele andere Dinge sind gefragt. Momentan werden diese Möglichkeiten nicht genutzt, aber wenn sie beginnen, wird Milander ernsthafte Wettbewerbsvorteile gegenüber anderen Entwicklern erzielen, da es in Russland keine direkten Analoga dieser Technologie gibt. oder 180 nm bei einer Spannung von 3,3 V oder hohe Spannungen bei Auslegungsstandards von 1-3 Mikrometer. Die Arbeiten zum Thema Hochspannungs-LDMOS (und sogar deren Freude) wurden in den letzten Jahren vom NIIIS veröffentlicht. Bisher handelt es sich jedoch nur um wissenschaftliche Veröffentlichungen, und von Massenproduktion ist keine Rede. Bereits im Frühjahr gab es die Nachricht, dass die Konstruktionsstandards von 500 nm „für Mikroschaltungen von Sekundärstromquellen“ in Bryansk „Silicon-L“ gemeistert wurden, aber keine Details angegeben wurden.

Föderale Institution Wissenschaftliches Forschungszentrum für Systemforschung der Russischen Akademie der Wissenschaften

NIISI untersucht systematisch das Rechnen, einschließlich strahlender Mikroprozessoren für Weltraumanwendungen. Eine systematische Forschung impliziert, wie es sich für ein akademisches Institut gehört, einen KPI bei der Anzahl der Veröffentlichungen. Daher ist die Überwachung des Institutsfortschritts viel einfacher als für kommerzielle Unternehmen. Wir interessieren uns für den „Space“ -Teil der „COMDIV“ -Linie (es gibt auch einen „High-Performance“ -Teil).Die Architektur von KOMDIV ist eine kreative Überarbeitung von MIPS32, die Anfang der neunziger Jahre von NIIIS lizenziert wurde. Anfänglich arbeitete das Institut mit ausländischen Fabriken und nach dem Erscheinen seiner eigenen Produktion begann es an zwei Fronten zu arbeiten, wobei der größte Teil der freudenträchtigen Linie nach Hause verlegt wurde. Das NIIIS-Werk befindet sich in Moskau am Kurchatov-Institut. Es wurde 2003 gestartet und ist eine kleine Pilotproduktion, die in versiegelten Clustern auf einem sehr bescheidenen Gebiet angesiedelt ist. Tatsächlich haben die Akademiker Betelin, Valiev und Velikhov das heutige Konzept der Minimal Fab verwirklicht, das normalerweise erst fünfzehn Jahre früher funktionierte als die Japaner (und das erste wurde 1983 von VA Labunov in Minsk erfunden). Anfänglich arbeitete die Fabrik mit Konstruktionsstandards von 500 nm, später wurden die Standards von 350 und 250 nm gemeistert.sowie die Silizium-auf-Isolator-Technologie, die zur Grundlage der strahlungsresistenten NIIIS-Linie wurde.Zwei Hauptvorteile des 1890VM1T-Prozessors (volumetrische 500-nm-Technologie, 50 MHz): Er funktioniert und ist inländisch. Russische Mikroschaltungen sind jedoch so schwerwiegend, dass sie für eine niedrige Umlaufbahn (nämlich für Bordcomputer des neuen „digitalen“ Raumfahrzeugs Sojus-TMA und Progress-M) trotz des gänzlichen Fehlens eines besonderen Strahlenschutzes ausreichen. Für den normalen Betrieb benötigt der 1890BM1T einen Companion-Chip, der für die Arbeit mit externen Schnittstellen zuständig ist (ähnlich wie ERC32 auf drei Chips hergestellt wurde). Für ernstere Bedingungen wurden Analoge (Serien 5890, 1900 und 1907) unter Verwendung der SOI-Technologie entwickelt, um den Thyristoreffekt zu beseitigen. Gleichzeitig befindet sich in den Chips der Serie 1907 der Schnittstellencontroller bereits auf demselben Chip wie der Prozessor.Wie ich bereits sagte, ist einer der Vorteile des Studiums von NIISI-Produkten die Fülle an Veröffentlichungen. Nehmen wir als Beispiel zwei Artikel, die 2011 und 2013 in IEEE Transactions on Nuclear Science veröffentlicht wurden. Das erste ist MS Gorbunov et al., "Analyse der SEE-Empfindlichkeit des SOI-CMOS-Mikroprozessors: Korrelation der mit verschiedenen Testmethoden erhaltenen Ergebnisse". Es beschreibt einen 500-nm-SOI-Prozessor mit einer Taktfrequenz von 33 MHz. Von den deklarierten architektonischen Maßnahmen zur Erhöhung der Fehlertoleranz nur die Cache-Parität, bei der ein Fehler dieselbe Unterbrechung wie ein Cache-Miss verursacht. Zusätzlich wurde eine spezielle Topologie von Transistoren angewendet, die den parasitären bipolaren Effekt unterdrückt und dadurch die Schwelle für Fehlfunktionen erhöht (und gleichzeitig aus nicht verwandten Gründen die Beständigkeit gegen die volle Strahlungsdosis erhöht). Relativ einfachAber wenn das Hauptziel Fehlertoleranz ist, dann ist dies genau das, was Sie brauchen. Und wenn das Problem der Ausfälle gelöst ist, können Sie anfangen, über Fehlertoleranz nachzudenken.Der zweite Artikel ist PN Osipenko et al., "Fault-Tolerant SOI Microprocessor for Space Applications". Hier sehen wir bereits 350 nm anstelle von 500 und 50-66 MHz anstelle von 33 (Leistung 8,9 MFLOPS bei 50 MHz). Dies sind noch immer keine 150 MHz, wie das amerikanische RAD750, das ungefähr zur gleichen Zeit in den Weltraum fliegt, aber der Fortschritt ist offensichtlich. Noch interessanter ist die detaillierte interne Struktur des Chips. Der gesamte Kern wird verdreifacht - nicht Trigger wie in LEON-FT, sondern alle kombinatorischen Logiken. Dies erhöht natürlich die Fläche und den Verbrauch um das Dreifache (1,8 W bei 66 MHz), hilft aber nicht nur bei Speicherelementen, sondern auch bei kombinierten Ausfällen. Sie sind viel kleiner als im Speicher, weil sie zeitlich mit der Vorderseite des Taktsignals zusammenfallen müssen, um etwas zu beeinflussen (und es gibt auch einen Maskierungseffekt, wenn der Fehler nicht durch die Logik geht, aber dies ist besonders).Aber wenn Sie bereits damit begonnen haben, alles richtig zu machen, müssen Sie sie loswerden.

, – , . – , . , . – ? , ( ) , . 1907014 0.25 5 CPU 89 MIPS ( 100 ) FPU 20 MFLOPS, 1907044 66 9 – 49 MIPS 14 MFLOPS . ,

Diagramm und Beschreibungen von der offiziellen Website, und weiterhin NIISI troirovannye Kern und konventionelle zu entwickeln.Abbildung 18. Grafik zur Entwicklung von Mikroschaltungen von der offiziellen Website des NIIIS (Mine). In roten Ovalen - Chips mit einem dreifachen Kern. Alles, was mit der SOI-Technologie gemacht wurde, ist strahlenresistent.Aus dem Diagramm geht hervor, dass NIISI zuerst die Technologie verbessert hat und sie sich dann, laut SOI, nach den besten verfügbaren Standards umgedreht haben, wie sie sollten. Der für uns interessanteste Teil der Tabelle ist die obere linke Ecke, die die Entwicklung eines dreifach strahlenden Mikroprozessors auf Basis der 65-nm-Technologie verspricht. Natürlich gibt es im Internet keine spezifischen Informationen zu diesem Prozessor, aber es werden erneut Veröffentlichungen veröffentlicht, die es uns ermöglichen, Studien zur Strahlenresistenz von 65 nm zu betrachten - und die ersten Artikel zu diesem Thema stammen aus dem Jahr 2012.Und jetzt endlich Sub-100

Figure 19. Mehrere Speicherfehler am Beispiel des 65-nm-Testkristalls.( ) , 65 . – , – . ! , – . , , , ( 2-2.5 ) – . , , . , , – , . – , . – , ( , ). – , . , ( ) – . , 65 DICE , . , .

Abbildung 20. Vergleich der Topologie einer herkömmlichen 6T-Speicherzelle (oben rechts) und einer regensicheren Version aus der DARE65-Bibliothek (IMEC, Belgien). Helle blaue Tore, braunes aktives Silizium.Mit dreifachen Triggern macht es auch Spaß - damit zwei Speicherelemente nicht vom selben Partikel abweichen, müssen sie durch dieselben 2 bis 2,5 Mikrometer voneinander getrennt sein. Bei 180 oder 350 nm ist dies nicht schwierig, aber gemäß den 65-nm-Standards ist die Fläche des dreifachen Triggers zwölfmal so groß wie die einer gewöhnlichen (und der größte Teil dieser Fläche ist leer). Unter dem Gesichtspunkt des Verbrauchs, der Fläche und der Einfachheit der Konstruktion im CAD ist ein Durchgangs-Threading-Schema, das für vollständig standardisierte Elemente ausgeführt wird, die weit genug voneinander entfernt sind, rentabler als die Verwendung von vorgefertigten Tripel-Triggern und anderen Basiselementen mit interner Redundanz.Abbildung 21. Dreifache modulare Redundanz und doppelte modulare Redundanz mit automatischer Abstimmung. Aus dem Artikel von J.Teufel, „Self-Voting Dual-Modular-Redundancy Circuits for

Single-Event-Transient Mitigation “, IEEE Transactions on Nuclear Science, 2008 (Sandia Labs ist immer noch bei uns bzw. immer noch bei ihnen)

Das Diagramm in der Abbildung stammt aus dem Jahr 2008 und zeigt, dass unsere vereidigten Freunde auch viele andere interessante Dinge in weniger öffentlichen Produkten verwenden als das RAD750 (und das Haupttätigkeitsfeld von Sandia Labs ist das amerikanische Nuklearprogramm). Insbesondere wird in dem oben erwähnten Artikel und in einer Reihe anderer neuerer Veröffentlichungen die Frage, wie eine dreifache und zweifache modulare Redundanz in verschiedenen Teilen des Chips zusammen verwendet werden kann, ausführlich erörtert. Übrigens, wenn das Abstimmungselement eine ausreichend große Verzögerung aufweist, werden einzelne Fehler in der Logik im Doppelreservierungsschema herausgefiltert, und das Ergebnis ist so stabil wie eine Dreifachreservierung.

Nun wollen wir sehen, wie Bibliothekselemente auf 65-nm-Technologie aussehen. Ich zitiere noch einmal die Arbeit von NIISI - Yu.B. Rogatkin et al., "Entwicklung einer Bibliothek strahlungsresistenter Elemente mit 65-nm-CMOS-Technologie", Proceedings of the NIISI RAS, 2018. Da die Sorge um die Fehlertoleranz nahezu vollständig auf andere Entwicklungsebenen übertragen wird - Architektur und automatische Synthese der Topologie unter Berücksichtigung von Einschränkungen bei der Lokalisierung von Elementen - wurden die Hauptaufgaben der Entwickler von Elementbibliotheken erneut zum Schutz vor der gesamten Energiedosis und dem Thyristoreffekt.

Figure 22. Mit 65-nm-Technologie hergestellte Logikzellen.

Das am weitesten links stehende Element in der Figur ist ein regulärer Bibliotheksinverter.

Das zweite Element ist die Strahlungsversion, die mit Schutzringen ausgestattet ist, die den Thyristoreffekt verhindern. Es ist wichtig, dass der Ring nur auf einer Seite Kontakte zum Metall hat, und wir müssen den Widerstand der Siliziumschicht berücksichtigen, der groß genug sein kann, um die Wirksamkeit dieser Lösung zu beeinträchtigen.

Der dritte ist der gleiche Wechselrichter, bei dem die Seiten des Schutzrings platzsparend abgeschnitten sind.

Der vierte ist derselbe, jedoch mit Kontakten zum äußeren Teil der Schutzringe, um deren Widerstand gut zu kontrollieren und sich nicht darum zu kümmern, wie sie zu Blöcken zusammengesetzt werden.

Fünftens - ein Block aus zwei Wechselrichtern und einem 2INE-Element mit den abschließenden Teilen der Schutzringe.

Was die volle Strahlungsdosis betrifft, so ist hier bei Standards unter 100 nm alles noch einfacher und verständlicher als bei älteren Technologien. Die Leckströme in ihnen sind bereits strahlungsfrei, alles ist auf sie gelegt, und so bleibt nur eine zusätzliche Korrektur für die Tatsache vorzunehmen, dass sie weiter wachsen werden. Typische Technologien dieser Stufe bieten normalerweise drei Arten von Transistoren - mit niedriger Schwellenspannung (schnell, aber mit großen Leckagen), mit mittlerer Schwellenspannung und mit hoher Schwellenspannung (langsam, aber mit kleinen Leckagen), und der Benutzer kann sie bei Bedarf kombinieren. Standardbibliotheken werden in der Regel auch in drei Versionen hergestellt. Bei der Entwicklung einer strahlungsresistenten Bibliothek muss ein Kompromiss zwischen Geschwindigkeit und Leckage eingegangen werden, da die Transistoren in Reihe oder parallel geschaltet sind.

Abbildung 23. Schemata der Logikelemente 2I-NOT und 2OR-NOT.

In Element 2, ODER NICHT, sind n-Kanal-Transistoren parallel geschaltet, was den Leckstrom verdoppelt, was bedeutet, dass es sinnvoll ist, an dieser Stelle Transistoren mit einer höheren Schwellenspannung zu verwenden. Und in 2I-NOT sind sie in Reihe geschaltet, und dort kann man die übliche Schwelle der Transistoren belassen. Und eine solche Argumentation (die vorzugsweise von Messdaten unterstützt wird) muss auf mehrere Hundert Elemente in der Bibliothek angewendet werden und dann überlegt werden, was mit den Speicherelementen zu tun ist, damit sie weniger verwirrt sind und über die in modernen Triggern häufig verwendeten analogen Schlüssel durchgesickert werden. Sie haben nicht alles kaputt gemacht und so weiter und so fort.

Ab heute verfügt NIIIS über eine vollwertige Plattform für die Entwicklung bei 65-nm-Designstandards, einschließlich Bibliotheken, IP-Blöcken, Speicherkompilierern, Hochgeschwindigkeitsschnittstellen usw. Es ist auch wichtig, dass diese Plattform an andere russische Unternehmen lizenziert wird, was dazu beiträgt, die Kluft zu den Amerikanern zu überwinden und die Europäer praktisch einzuholen. Wenn die Fabrik nicht TSMC wäre, sondern eine eigene, wie in Amerika und Europa ... Aber dies ist eine andere Geschichte, die sich vor unseren Augen abspielt. Nach 2014 ist die Micron-Prozesstechnologie von Mikron im Status des „Bestehens der Qualifikation und des Mastering in der Produktion“ eingefroren, und es gibt seit einiger Zeit keine Nachrichten mehr darüber. In den letzten Monaten gab es jedoch genug Neuigkeiten über langfristige Pläne, in Russland eine Produktion mit 28-nm-Standards zu schaffen. Wann und ob diese Pläne umgesetzt werden, ist eine große Frage.

Zusammenfassend stellen wir fest, dass sich die Aufgaben, mit denen Entwickler konfrontiert sind, mit sinkenden Designstandards erneut geändert haben. Tief-Submikron-Technologien sind beständig gegen eine volle Strahlungsdosis, die für die meisten Anwendungen ausreicht, und ermöglichen es Ihnen, den Schutz gegen Thyristoreffekte und Einzel- / Mehrfachfehler in der Phase der Chipentwicklung zu organisieren, ohne die ursprüngliche Prozesstechnologie zu ändern. Dies hilft, die Produktionskosten zu senken und die Entwicklung neuer Technologien zu beschleunigen. Die Haupthindernisse für den Fortschritt sind wirtschaftlicher Natur: Die Entwicklung und umfassende Untersuchung von Test- und Kampfchips wird mit jeder neuen Technologiegeneration teurer, und die mageren Umläufe von Weltraumchips ermöglichen es uns nicht, diese Kosten angemessen zu kompensieren. Daher versuchen Entwickler, die Fähigkeiten jeder verwendeten Technologie zu maximieren und sie so lange wie möglich zu nutzen. Sie arbeiten nur dann weiter, wenn dies unbedingt erforderlich ist, und entwickeln Entwicklungsplattformen, mit denen Sie eine breite Palette von Mikroschaltkreisen erstellen können. Russische Entwickler sind heute weit hinter westlichen Kollegen zurückgeblieben, und die Gründe für diese Verzögerung sind nicht wissenschaftlich oder ingenieurwissenschaftlich, sondern organisatorisch und wirtschaftlich.

Zwangsweise eine kurze Analyse aller anderen

Japan

Die japanische Weltraumagentur JAXA ist nur mäßig an internationalen Aktivitäten beteiligt, und der größte Teil ihrer Weltraumforschung wird von den Japanern selbst durchgeführt. Die Missionen beeindrucken mit Ehrgeiz und atemberaubenden Geschichten über die erfolgreiche Überwindung der Schwierigkeiten, die im Orbit auftreten. Wenn Matt Damon eine Raumsonde spielen könnte, würden wir schon Filme über Hayabusa an der Abendkasse sehen (die Japaner haben übrigens schon drei Stücke gedreht) und über Akatsuki. Mikroprozessoren für den Weltraum, wie alles andere, haben die Japaner ihre eigenen, eigenen Architekturen, und selbst ihre Designstandards für die Produktion sind nicht die gleichen wie im Rest der Welt (300 und 200 nm zum Beispiel). Ich würde sehr gerne ausführlich darüber schreiben, aber es gibt nur wenige Informationen und es gibt fast keine Informationen in einer nicht-japanischen Sprache, so dass ich mich auf einen kurzen Überblick beschränken muss.

Abbildung 24. Eine typische Informationsquelle für strahlungsresistente japanische Prozessoren.

Die Hauptlieferanten von JAXA-Instrumenten sind Hitachi, NEC und MHI (Mitsubishi Heavy Industries). In den achtziger Jahren begeisterte sich die japanische Industrie für das TRON-Projekt, das ein durchgängiges Design der Netzwerkinfrastruktur bot. Die Japaner verwenden das TRON-Echtzeitbetriebssystem bisher in der Industrie und im Weltraum, aber die Architektur der TRON-Mikroprozessoren wurde ziemlich schnell aufgegeben (obwohl strahlungsresistente Chips darauf hergestellt wurden und höchstwahrscheinlich flogen sie), und zwar zugunsten von MIPS64 (im Fall von NEC) und einem anderen Japanische 32-Bit-SuperH-Architektur (H ist Hitachi; die SH2-Version ist in japanischen Autos und SH4 in den Automobilprodukten Sega Dreamcast und Hitachi und Renesas zu finden).

Abbildung 25. Mikroprozessoren für den japanischen Weltraum. HR5000 - MIPS64, SOI-SOC - SH4.

Abbildung 26. Darstellung von SOI-SOC2-Anwendungen.

"SOI" in SOI-SOC bedeutet natürlich "Silizium auf dem Isolator". Das technologische Niveau von SOI-SOC3 beträgt 200 nm, die nächste Generation in der Entwicklung wird weniger haben. Ebenfalls ein kleines, aber wichtiges Zitat von JAXA: „Es gibt ein großes Problem mit weichen Fehlern bei Konsum- / Industrieprozessoren aufgrund atmosphärischer Neutronen auf Bodenniveau. SOI-SOC MPU wird als hochzuverlässiges Teil an Benutzer dieser Prozessoren geliefert. " Das Problem der atmosphärischen Neutronen hängt hauptsächlich mit der Luftfahrt zusammen, aber das ist eine andere Geschichte. Das ist alles mit den Japanern, geh zu ihren Nachbarn.

China

Das chinesische Weltraumprogramm ist das am schnellsten wachsende und eine der am dichtesten geschlossenen Informationen über japanische Prozessoren im Vergleich zu Chinesen, die nur auf See sind. Es ist schwierig, etwas Konkretes zu sagen, außer dass die Chinesen mit dem schichtweisen Kopieren von allem in einer Reihe begannen und 2014 viele Positionen für Russland hatten, die unter Sanktionen standen. In letzter Zeit wurde jedoch viel Geld in die chinesische Astronautik und die chinesische Mikroelektronik investiert, und die neuesten Geräte arbeiten mit MIPS-kompatiblen Prozessoren, die von der chinesischen Akademie der Wissenschaften entwickelt wurden (ähnelt nichts?). Loongson. Loongson Civilians bauen PCs, Tablets und sogar einen Supercomputer. Dieser Prozess beschleunigte sich nach dem Ausbruch des Handelskrieges zwischen den Vereinigten Staaten und China erheblich.

Israel

Die Israel Space Agency wurde 1981 gegründet, der erste eigene Satellit wurde 1988 von Israel aus gestartet. Gegenwärtig entwickelt und startet Israel (unabhängig und von ausländischen Weltraumhäfen) mehrere Familien von zivilen wissenschaftlichen und militärischen Fahrzeugen. Ich konnte keine Informationen über ihre Ausrüstung finden, aber ich wage vorzuschlagen, dass zumindest die ersten Aufklärungsfahrzeuge, die von einem der wichtigsten israelischen Luftfahrtunternehmen entwickelt wurden, mit Chips der Architektur 1750A geflogen sind. Im modernen Tiefbau arbeiten israelische Unternehmen viel mit ihren europäischen Kollegen zusammen. Daher ist es logisch, die Verwendung von LEONs zu übernehmen. Die Bestätigung dafür ist, dass der private Bereshit-Satellit im vergangenen Jahr auf dem GR712 geflogen ist, einer in Israel entwickelten und hergestellten Version von LEON.

Indien

In Indien werden keine Mikroschaltkreise hergestellt, nur eine Versuchsfabrik der örtlichen Akademie der Wissenschaften (erinnert das nicht an irgendetwas?) Mit 180-nm-Standards. Die Indianer erforschen die Freude, aber nichts Wichtiges ist von ihnen zu hören. Nach fragmentarischen Informationen aus verschiedenen Quellen verwendeten / verwenden sie für ihre Satelliten ERC32- und LEON-Prozessoroptionen, und die großartige Marsmission „Mangalyan“ wurde vollständig von Mil-Std-1750A-Architekturprozessoren (wieder europäisch) gesteuert.

Brasilien

Die brasilianische Mikroelektronik ist fast wie ein brasilianisches Weltraumprogramm: Man weiß nichts darüber, aber es existiert. Insbesondere Brasilianer sind starke Spezialisten für die Behebung einzelner Fehler auf gewöhnlicher Hardware mithilfe von Softwaremethoden (z. B. mehrmaliges Ausführen eines Teils von Befehlen und Überprüfen der Ergebnisse) und für die FPGA-Fehlertoleranz. Fachhochschulgruppen beteiligen sich aktiv an internationalen wissenschaftlichen Konferenzen und machen gemeinsame Projekte mit europäischen und amerikanischen Kollegen.

Das scheint alles zu sein. Die übrigen Länder entwickeln nicht unabhängig voneinander Mikroprozessoren oder darauf basierende Systeme für den Weltraum und kaufen Schlüsselkomponenten, Blöcke oder Satelliten, die an der Seite montiert wurden, wie beispielsweise Pakistan, das in enger Zusammenarbeit mit den Chinesen seine eigene Satellitenindustrie entwickelt. Nun, es ist klar, dass das Befüllen von iranischen und nordkoreanischen Geräten nur ihren Machern und, wenn sie Glück haben, einigen Geheimdiensten bekannt ist. Wir sind keine Intelligenz, also fahren wir mit dem nächsten Teil fort.

Die nahe Zukunft - ein Beispiel für alles zusammen

Das technologische Niveau der neuesten Weltraummikroprozessoren liegt bei 45 nm für die USA (RAD5500), 65 nm für Europa (GR740) und 65 nm für Russland (sie versprechen, noch in diesem Jahr etwas herauszubringen). Gleichzeitig ist in den ersten beiden Fällen ein Generationswechsel zu beobachten: In den USA wird die nächste Generation von Weltraumprozessoren (HPSC) nicht vom derzeitigen Monopolisten von BAE Systems für PowerPC-Architektur, sondern von Boeing für ARM (gemäß Designstandards 32 nm für SOI-Technologie), sondern in Europa hergestellt Parallel zur Veröffentlichung des nächsten SPARC LEON wird ein DAHLIA-Multi-Core-Prozessor mit ARM-Architektur für 28-nm-Designstandards (auch SOI) gebaut. Parallel dazu begann die Europäische Weltraumorganisation in ihrem gewohnten Wunsch, nicht von Lizenzen anderer abhängig zu sein, mit der Entwicklung der neuen RISC-V-Architektur, die im kommerziellen Sektor rasch an Dynamik gewinnt und sich zu einem Software-Ökosystem entwickelt. Die ersten Prototypen von TMR-modifizierten RISC-V-Chips wurden bereits 2018 durch die Zusammenarbeit von Antmicro und Thales demonstriert. Trotz der Popularität von LEON (wie man in engen Kreisen sagt) gegenüber SPARC gab es lange Fragen zur Softwareunterstützung, und die Wettbewerber haben es eilig, dies auszunutzen. Konkurrenten haben es mit ARM besonders eilig, da der praktisch freie Zugriff auf eine große Menge an industrieller und kommerzieller Anwendungssoftware ein sehr wichtiger Trumpf im Gespräch mit Raumfahrzeugentwicklern ist, dessen Bedeutung im Vergleich zu dem Wunsch nach Abwärtskompatibilität mit alten Projekten rapide zunimmt.

Neben Mikroprozessoren und DSP, bei denen Geschwindigkeit eine offensichtliche Priorität darstellt, besteht ein Bedarf an Mikrocontrollern. Es gibt solche Chips auf den meisten Architekturen mit Sprachausgabe - europäische GR716 (SPARC / LEON), amerikanische RAD EMC (PowerPC), ARM von verschiedenen Herstellern (Vorago, Microchip, Milander, Angstrom), regensichere Versionen von MSP430 von Texas Instruments, MCS- 96 und MCS-51 von NIIET und so weiter und so fort. Mikrocontroller sind in der Regel einfacher zu schützen als ihre "großen" Gegenstücke, wobei das Fehlen von Ausfällen (Thyristoreffekt) und die minimale Korrektur gekaufter Kerne im Vordergrund stehen (oder keine Korrektur und Synthese mithilfe von Triggern und speziellen Elementbibliotheken). Kehren wir zu den Prozessoren zurück und schauen wir uns an, welche Entwicklungsplattformen für Sub-100-Nanometer existieren oder gerade angekündigt werden.

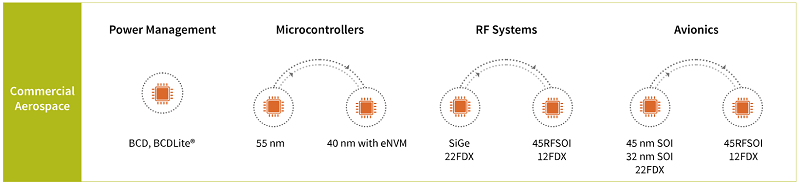

Abbildung 27. Sub-100-nm-Entwicklungsplattform für strahlungsresistente integrierte Schaltkreise.

65 Seemeilen für die Entwickler in Europa und Russland sind bereits "heute", und die Amerikaner sind im Allgemeinen von 150 Seemeilen sofort auf 45 Seemeilen gesprungen. Höchstwahrscheinlich werden diese Technologien in den nächsten zehn Jahren die wichtigsten sein, und die subtileren Standards, die bereits in diesem Diagramm dargestellt sind, werden von den frühen in die späten Entwicklungsstadien übergehen. Was in der Abbildung gezeigt wird, sind jedoch nur große öffentliche Kooperationen, in der Tat behindert nichts (außer Zeit und Geld) die Entwicklung strahlungsresistenter Chips auf anderen technischen Prozessen ohne zu viel Lärm. Zum Beispiel bietet GlobalFoundries an, Luft- und Raumfahrtchips mit einer ganzen Reihe von Technologien für unterschiedliche Geschmäcker und Budgets herzustellen. In ihren Werken werden die neuesten RAD5545 hergestellt, und auch HPSC wird dort hergestellt. Dies ist nicht verwunderlich, da die GloFo-Fabriken seit ihrer Zugehörigkeit zu IBM Trusted Foundry-zertifiziert sind. Und es ist unwahrscheinlich, dass alle deklarierten Prozesse ohne amerikanische Kunden sind.

Abbildung 28. GlobalFoundries-Angebote für die Luft- und Raumfahrtindustrie.

Bei GlobalFoundries, obwohl nicht amerikanisch, sondern deutsch (in Dresden), planen sie, ihre zukünftigen strahlungsresistenten IMEC-Chips (dh ganz Europa minus STM) und Milander zu produzieren.

Abbildung 29. Die Milandra-Roadmap für die Entwicklung strahlungsresistenter Chips auf Basis der 22-nm-Technologie. Wie Sie sehen, gibt es viele Pläne, einschließlich großer FPGAs und schneller ADCs für Software Defined Radio (SDR). Der erste Testchip wurde bereits produziert, daher freuen wir uns auf gute Neuigkeiten.

Was ist FDSOI? FD ist vollständig erschöpft, vollständig erschöpft; Die dünne aktive Siliziumschicht zwischen dem Gateoxid und dem latenten Oxid ist vollständig erschöpft, und der gesamte Kanal des Transistors belegt sie. Auf diese Weise können Sie die Streukapazität von Drain und Source vollständig beseitigen sowie die für ähnliche Massentechnologien typische Kriechstrecke entlang der Siliziumtiefe beseitigen und den statischen Stromverbrauch senken. Zusätzlich kann FDSOI anstelle der Verwendung mehrerer Transistortypen wie in der Volumentechnologie lokal eine negative oder positive Spannung an ein verborgenes Oxid liefern und dadurch die Schwelle des Transistors (und damit die Geschwindigkeit und den Stromverbrauch) ändern - abhängig davon, ob sich der Chip in befindet aktiv oder im Schlafmodus. Zusammen macht dies FDSOI beispielsweise für das Internet der Dinge äußerst attraktiv. Bei Weltraumschaltkreisen mit geringem Stromverbrauch lindert der Vorteil der SOI-Technologie automatisch die Entstehung von Kopfschmerzen mit katastrophalen Ausfällen aufgrund des Thyristoreffekts.

Abbildung 30. Querschnittsansichten von Surround- und FDSOI-Transistoren.

Der Hauptnachteil von FDSOI in Bezug auf den Strahlungswiderstand ist der zusätzliche Leckpfad entlang der Grenze des Kanals und des latenten Oxids. Die im versteckten Oxid akkumulierte Ladung spielt die Rolle einer positiven Spannung, die an das versteckte Oxid angelegt wird, und anstatt das Verhalten der Transistoren durch das untere Gate zu steuern, muss der Strahlungseffekt kompensiert werden. Dazu muss eine große negative Spannung angelegt werden, die den Ladungsansammlungsprozess im latenten Oxid beschleunigt und den Dosiswiderstand verschlechtert. Im Allgemeinen ergibt sich ein Teufelskreis, aus dem sich herausstellen kann, dass er nicht trivial ist. Es stimmt, es gibt viele Leute, die nach ihm suchen wollen, damit Sie sich mit Popcorn eindecken können. Das erste Popcorn wird sehr bald nützlich sein - das europäische Projekt DAHLIA ist fast abgeschlossen.

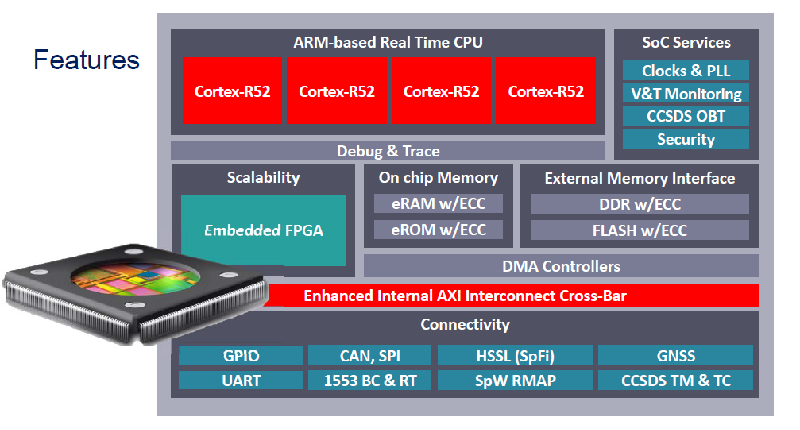

Abbildung 31. Blockdiagramm von DAHLIA. 28 nm FDSOI, vier ARM-Cortex R52-Kerne (versprochen 4000 DMIPS bei 600 MHz), geschärft für Echtzeitanwendungen mit erweiterter Leistungstrennung, integriertem Speicher, den gängigsten Schnittstellen und sogar einem integrierten FPGA für 500.000 LUT, sodass ein Chip genau ist decken die Bedürfnisse aller Nutzer über viele Jahre hinweg ab.

Die volumetrische Technologie wird in der Zwischenzeit nicht aufgeben.

Es kann Entwicklern das Fehlen eines „zusätzlichen“ Leckpfads und langfristig niedrigere Designstandards bieten. Darüber hinaus beginnt bei FinFET-Transistoren das Gate, den Kanal immer dichter zu bedecken, und das isolierende Oxid entfernt sich von dem starken elektrischen Feld, was sich auch positiv auf den Widerstand gegen die volle Strahlungsdosis auswirken sollte. IMEC beginnt bereits mit der Entwicklung von strahlungsresistenten 16-nm-Bibliotheken, und die kommerzielle Industrie setzt weiterhin auf neue Technologien.Abbildung 32. Verschiedene Generationen von MOS-Transistoren.Auf lange Sicht verspricht Samsung, dass GAA (Gate All Around) beständig gegen eine volle Strahlungsdosis ist, was die Entwickler völlig von den Problemen befreit: Sie haben einfach keinen Seitenweg von der Quelle zum Abfluss, hinter dem Hauptkanal und dem Hauptverschluss und einen Gate-Isolator so subtil, dass die Verschiebung der Schwellenspannung selbst bei sehr hohen Dosen vernachlässigbar ist. Aber natürlich wird es einige neue Schwierigkeiten geben - nicht nur bei einzelnen Ausfällen, sondern beispielsweise auch bei Vorspannungseffekten, die für die Entwickler von HEMT-Galliumnitrid-Transistoren bereits in vollem Umfang von Belang sind. In Bauelementen aus komplexen Halbleitern sind Quanten- und Nanomaßstabseffekte nichts Neues, und Siliziumentwickler werden sehr bald Kenntnisse darüber benötigen.Daher wird es in den nächsten Jahren ausreichen, die Strahlungsbeständigkeit von Mikrochips für den Weltraum sicherzustellen. Es gibt aber auch Hadron Collider, atomare und thermonukleare Energie; Fortschritt ist unerbittlich und er wird nicht aufhören - aber ich werde auf dieser positiven Note aufhören. Vielen Dank für das Lesen bis zum Ende, ich hoffe es war interessant.