Journal: Shock and Vibration 16 (2009) 45–59Autoren: Robin Alastair Amy, Guglielmo S. Aglietti (E-Mail: gsa@soton.ac.uk) und Guy RichardsonOrte der Autoren: Astronautical Research Group, Universität Southampton, School of Engineering Sciences, Southampton, Großbritannien

Surrey Satellite Technology Limited, Guildford, Surrey, GroßbritannienCopyright 2009 Hindawi Publishing Corporation. Dies ist ein Open-Access-Artikel, der unter der Creative Commons Attribution License vertrieben wird und der die uneingeschränkte Verwendung, Verteilung und Reproduktion auf jedem Medium gestattet, sofern das Originalwerk ordnungsgemäß zitiert wird.

Anmerkung. In Zukunft wird davon ausgegangen, dass alle modernen elektronischen Geräte eine ständig wachsende Funktionalität aufweisen und gleichzeitig den Belastungen durch Stöße und Vibrationen standhalten. Die Vorhersage der Zuverlässigkeit wird aufgrund der komplexen Eigenschaften der Reaktionen und Ausfälle elektronischer Geräte erschwert, sodass die derzeitigen Methoden einen Kompromiss zwischen der Genauigkeit der Berechnungen und ihren Kosten darstellen.

Eine zuverlässige und schnelle Vorhersage der Zuverlässigkeit elektronischer Geräte während des Betriebs mit dynamischen Lasten ist für die Branche von großer Bedeutung. Dieser Artikel zeigt die Probleme bei der Vorhersage der Zuverlässigkeit elektronischer Geräte, wodurch der Empfang von Ergebnissen verlangsamt wird. Es ist auch zu beachten, dass das Modell zur Berechnung der Zuverlässigkeit normalerweise unter Berücksichtigung einer Vielzahl von Ausrüstungskonfigurationen für eine Reihe von Komponenten desselben Typs erstellt wird. In diesem Artikel werden vier Klassen von Methoden zur Vorhersage der Zuverlässigkeit (Referenzmethoden, Testdaten, experimentelle Daten und Modellierung der physikalischen Ursachen des Versagens - Physik des Versagens) verglichen, um die Möglichkeit der Verwendung der einen oder anderen Methode zu ermitteln. Es wird angemerkt, dass die meisten Fehler in elektronischen Geräten durch thermische Belastungen verursacht werden. Diese Überprüfung konzentriert sich jedoch auf Fehler, die durch Schock und Vibration während des Betriebs verursacht werden.

Anmerkung des Übersetzers.

Anmerkung des Übersetzers. Der Artikel ist eine Überprüfung der Literatur zu diesen Themen. Trotz seines relativ hohen Alters bietet es eine hervorragende Einführung in das Problem der Zuverlässigkeitsbewertung mit verschiedenen Methoden.

1. Terminologie

BGA Ball Grid Array.

DIP-Dual-In-Line-Prozessor, manchmal auch als Dual-In-Line-Paket bezeichnet.

FE Finite Elemente.

PGA Pin Grid Array.

PCB Printed Circuit Board, manchmal auch als PWB (Printed Wiring Board) bekannt.

PLCC Kunststoff-Chipträger.

PTH-beschichtetes Durchgangsloch, manchmal auch als Pin-Durchgangsloch bezeichnet.

QFP Quad Flat Pack - auch als Möwenflügel bekannt.

SMA Formgedächtnislegierungen.

SMT Surface Mount Technologie.

Anmerkung der Autoren des Originals: In diesem Artikel bezieht sich der Begriff „Komponente“ auf ein bestimmtes elektronisches Gerät, das an eine Leiterplatte gelötet werden kann. Der Begriff „Gehäuse“ bezieht sich auf eine beliebige Komponente einer integrierten Schaltung (normalerweise eine SMT- oder DIP-Komponente). Der Begriff „angehängte Komponente“ bezieht sich auf eine beliebige Kombination aus Leiterplatte oder Komponentensystem, wobei betont wird, dass angehängte Komponenten ihre eigene Masse und Steifigkeit haben. (Die Kristallverpackung und ihre Auswirkung auf die Zuverlässigkeit werden in dem Artikel nicht berücksichtigt, daher kann der Begriff "Verpackung" weiter als der "Fall" des einen oder anderen Typs verstanden werden - ungefähr übersetzt.)

2. Erklärung des Problems

Auf die Leiterplatte ausgeübte Schock- und Vibrationsbelastungen verursachen Spannungen auf dem Leiterplattensubstrat, den Baugruppengehäusen, den Leiterbahnen und den Lötstellen. Diese Spannungen sind auf eine Kombination von Biegemomenten in der Leiterplatte und der Trägheit der Masse des Bauteils zurückzuführen. Im schlimmsten Fall können diese Spannungen einen der folgenden Fehlermodi verursachen: Abblättern der Leiterplatte, Zerstörung der Lötstelle, Zerstörung des Bleis oder Zerstörung des Bauteilpakets. Wenn einer dieser Zerstörungsmodi aufgetreten ist, folgt höchstwahrscheinlich ein vollständiger Ausfall des Geräts. Der während des Betriebs auftretende Fehlermodus hängt von der Art der Verpackung, den Eigenschaften der Leiterplatte sowie der Häufigkeit und Amplitude der Biegemomente und Trägheitskräfte ab. Der langsame Fortschritt bei der Analyse der Zuverlässigkeit elektronischer Geräte ist auf die zahlreichen Kombinationen von Eingangsfaktoren und Arten von Fehlern zurückzuführen, die berücksichtigt werden müssen.

Im Rest dieses Abschnitts werden wir versuchen, die Komplexität der gleichzeitigen Berücksichtigung verschiedener Eingabefaktoren zu erklären.

Der erste komplizierende Faktor, der berücksichtigt werden muss, ist die breite Palette von Pakettypen, die in der modernen Elektronik verfügbar sind, da jedes Paket aus verschiedenen Gründen fehlschlagen kann. Schwere Bauteile sind anfälliger für Trägheitslasten, während das Verhalten von SMT-Bauteilen stärker von der Krümmung der Leiterplatte abhängt. Aufgrund dieser grundlegenden Unterschiede weisen diese Arten von Bauteilen je nach Masse oder Größe erheblich unterschiedliche Ausfallkriterien auf. Dieses Problem wird durch das ständige Auftauchen neuer auf dem Markt erhältlicher Komponenten noch verschärft. Daher muss jedes vorgeschlagene Verfahren zur Vorhersage der Zuverlässigkeit an neue Komponenten angepasst werden, um in Zukunft eine praktische Anwendung zu haben. Die Reaktion der Leiterplatte auf Vibrationen wird durch die Steifheit und Masse der Komponenten bestimmt, die die lokale Reaktion der Leiterplatte beeinflussen. Es ist bekannt, dass die schwersten oder größten Komponenten die Reaktion der Platine auf Vibrationen an den Stellen ihrer Installation erheblich verändern. Die mechanischen Eigenschaften der Leiterplatte (Elastizitätsmodul und Dicke) können die Zuverlässigkeit in schwer vorhersehbarer Weise beeinflussen.

Eine steifere Leiterplatte kann die Gesamtreaktionszeit der Leiterplatte unter Last verringern, gleichzeitig können die auf die Komponenten einwirkenden Biegemomente lokal zunehmen. (Außerdem ist es im Hinblick auf thermisch bedingte Ausfälle vorzuziehen, eine kompatiblere Leiterplatte anzugeben. da es die thermischen Beanspruchungen der Verpackung reduziert - ca. Die Häufigkeit und Amplitude lokaler Biegemomente und Trägheitslasten, die dem Paket überlagert sind, wirken sich auch auf den wahrscheinlichsten Fehlermodus aus. Hochfrequente Lasten mit niedriger Amplitude können zum Ermüdungsversagen der Struktur führen, was die Hauptursache für das Versagen sein kann (geringe / hohe zyklische Ermüdung, LCF bezieht sich auf Versagen, bei denen plastische Verformung vorherrscht (N_f <10 ^ 6), während HCF das Versagen der elastischen Verformung bezeichnet , normalerweise (N_f> 10 ^ 6) bis zum Versagen [56] - Anmerkung des Autors) Die endgültige Anordnung der Elemente auf der Leiterplatte bestimmt die Ursache des Versagens, das aufgrund der Spannung in einem einzelnen Bauteil auftreten kann, die durch Trägheitslast oder lokale Biegemomente. Schließlich ist es notwendig, den Einfluss des menschlichen Faktors und der Produktionsmerkmale zu berücksichtigen, was die Wahrscheinlichkeit eines Geräteausfalls erhöht.

Bei der Betrachtung einer erheblichen Anzahl von Eingabefaktoren und ihrer komplexen Wechselwirkung wird deutlich, warum noch keine wirksame Methode zur Vorhersage der Zuverlässigkeit elektronischer Geräte entwickelt wurde. Eine von den Autoren empfohlene Literaturübersicht zu diesem Thema wird in IEEE [26] vorgestellt. Diese Übersicht konzentriert sich jedoch hauptsächlich auf relativ breite Klassifikationen von Zuverlässigkeitsmodellen, wie z. B. die Methode zur Vorhersage der Zuverlässigkeit in der Referenz- und Zulassungsliteratur, experimentelle Daten und computergestützte Modellierung von Ausfallbedingungen (Physics-of-Failure Reliability (PoF)), und geht nicht detailliert genug auf Ausfälle ein. verursacht durch Schock und Vibration. Foucher et al. [17] folgen einem ähnlichen Schema des IEEE-Reviews, da der Schwerpunkt auf thermischen Ausfällen liegt. Die bisherige Kürze der Analyse von PoF-Methoden, insbesondere in Bezug auf Schock- und Vibrationsfehler, verdient ihre weitere Berücksichtigung. Eine ähnliche Überprüfung wie die IEEE befindet sich derzeit in der Erstellung der AIAA, der Umfang dieser Überprüfung ist jedoch noch nicht bekannt.

3. Die Entwicklung von Methoden zur Zuverlässigkeitsvorhersage

Die früheste Zuverlässigkeitsvorhersage-Methode, die in den 1960er Jahren entwickelt wurde, ist derzeit in MIL-HDBK-217F [44] beschrieben (Mil-Hdbk-217F ist die neueste und endgültige Version der 1995 veröffentlichten Methode - Anmerkung des Autors). Using Mit dieser Methode, bei der eine Datenbank mit Ausfällen elektronischer Geräte verwendet wird, wird die durchschnittliche Lebensdauer der Leiterplatte ermittelt, die aus bestimmten Komponenten besteht. Dieses Verfahren ist als Verfahren zur Vorhersage der Zuverlässigkeit gemäß der Referenzliteratur bekannt. Trotz der Tatsache, dass Mil-Hdbk-217F immer veralteter wird, wird die Referenzmethode noch heute verwendet. Die Einschränkungen und Ungenauigkeiten dieser Methode waren gut dokumentiert [42,50], was zur Entwicklung von drei Klassen alternativer Methoden führte: Computersimulation physikalischer Versagenszustände (PoF), experimentelle Daten und Feldtestdaten.

PoF-Methoden sagen Zuverlässigkeit analytisch voraus, ohne zuvor gesammelte Daten zu verwenden. Alle PoF-Methoden haben zwei Gemeinsamkeiten der in Steinberg [62] beschriebenen klassischen Methode: Zunächst wird das Schwingungsverhalten der Leiterplatte auf einen bestimmten Schwingungseffekt untersucht, dann werden die Versagenskriterien der einzelnen Komponenten nach Schwingungseinwirkung überprüft. Eine wichtige Errungenschaft bei PoF-Methoden war die Verwendung der verteilten (gemittelten) Eigenschaften der Leiterplatte, um schnell ein mathematisches Modell der Leiterplatte zu erstellen [54], was die Komplexität und den Zeitaufwand für die genaue Berechnung der Vibrationsleistung der Leiterplatte erheblich verringerte (siehe Abschnitt 8.1.3). Jüngste Entwicklungen auf dem Gebiet der PoF-Methoden haben die Ausfallvorhersage für SMT-Lötkomponenten verbessert. Mit Ausnahme der Barkers-Methode [59] sind diese neuen Methoden jedoch nur in sehr speziellen Kombinationen von Bauteilen und Leiterplatten anwendbar. Für große Bauteile wie Transformatoren oder große Kondensatoren stehen nur sehr wenige Methoden zur Verfügung.

Methoden experimenteller Daten verbessern die Qualität und Leistungsfähigkeit des Modells, das in Methoden zur Vorhersage der Zuverlässigkeit in der Referenzliteratur verwendet wird. Die erste Methode, die auf experimentellen Daten zur Vorhersage der Zuverlässigkeit elektronischer Geräte basiert, wurde 1999 durch die von Honeywell, Inc [20] entwickelte HIRAP-Methode (Honeywell In-Service Reliability Assessment Program) beschrieben. Die experimentelle Datenmethode hat mehrere Vorteile gegenüber Zuverlässigkeitsprognosemethoden in der Referenz- und Zulassungsliteratur. In letzter Zeit sind viele ähnliche Methoden aufgetaucht (REMM und TRACS [17], auch FIDES [16]). Das experimentelle Datenverfahren sowie das Zuverlässigkeitsprognoseverfahren gemäß der Referenz- und Zulassungsliteratur erlauben es nicht, das Layout der Leiterplatte und die Arbeitsumgebung ihres Betriebs bei der Zuverlässigkeitsbewertung zufriedenstellend zu berücksichtigen. Dieser Nachteil kann aufgrund von Daten zu Platinenfehlern behoben werden, die im Design ähnlich sind, oder aufgrund von Platinen, die sich unter ähnlichen Betriebsbedingungen befanden.

Die experimentellen Datenmethoden hängen von der Verfügbarkeit einer umfangreichen Datenbank ab, die Daten zu Fehlern im Zeitverlauf enthält. Jeder Fehlertyp in dieser Datenbank muss korrekt identifiziert und die wahre Ursache ermittelt werden. Diese Methode zur Bewertung der Zuverlässigkeit eignet sich für Unternehmen, die die gleichen Geräte in ausreichend großen Chargen herstellen, sodass eine erhebliche Anzahl von Fehlern verarbeitet werden kann, um die Zuverlässigkeit zu bewerten.

Seit Mitte der 1970er Jahre werden Methoden zum Testen elektronischer Komponenten auf Zuverlässigkeit verwendet. Sie werden normalerweise in beschleunigte und nicht beschleunigte Tests unterteilt. Der Hauptansatz besteht darin, Geräte zu testen, um die erwartete Betriebsumgebung so realistisch wie möglich zu gestalten. Tests werden durchgeführt, bis ein Fehler auftritt, der eine Vorhersage der MTBF ermöglicht (mittlere Zeit zwischen Fehlern - MTBF). Wenn MTBF als sehr lang eingestuft wird, kann die Testdauer durch beschleunigte Tests verkürzt werden, die durch die Stärkung der Umweltfaktoren und die Verwendung der bekannten Formel zur Verknüpfung der Ausfallrate in einem beschleunigten Test mit der im Betrieb zu erwartenden Ausfallrate erreicht werden. Ein solches Testen ist für Komponenten mit einem hohen Ausfallrisiko von entscheidender Bedeutung, da es dem Forscher Daten mit dem höchsten Vertrauensniveau liefert. Es wäre jedoch aufgrund der langen Zeitspanne einer Iteration der Studie unpraktisch, sie zur Optimierung des Designs der Leiterplatten zu verwenden.

Ein kurzer Überblick über die in den 1990er Jahren veröffentlichten Arbeiten legt nahe, dass dies eine Zeit war, in der Methoden, die experimentelle Daten, Testdaten und PoF-Methoden verwendeten, miteinander konkurrierten, um veraltete Methoden zur Vorhersage der Zuverlässigkeit aus der Referenz- und Zulassungsliteratur zu ersetzen. Darüber hinaus hat jede Methode ihre Vor- und Nachteile und liefert bei richtiger Anwendung wertvolle Ergebnisse. Infolgedessen hat IEEE kürzlich einen Standard veröffentlicht [26], der alle Methoden auflistet, die heute zur Vorhersage der Zuverlässigkeit verwendet werden. Das Ziel von IEEE war es, ein Handbuch zu erstellen, das dem Ingenieur Informationen zu allen verfügbaren Methoden sowie zu den Vor- und Nachteilen der einzelnen Methoden liefert. Obwohl der IEEE-Ansatz noch am Anfang eines langen Evolutionswegs steht, scheint er seine eigenen Vorzüge zu haben, da die AIAA (American Institute of Aeronautics and Astronautics) einen Leitfaden mit der Bezeichnung S-102 erstellt, der dem IEEE-Leitfaden ähnelt, aber auch berücksichtigt die relative Qualität der Daten aus jeder Methode [27]. Diese Richtlinien sollen nur die Methoden zusammenführen, die weltweit in der zu diesen Themen veröffentlichten Literatur verbreitet werden.

4. Störungen durch Vibration

Die meisten früheren Studien haben sich hauptsächlich auf zufällige Vibrationen als Belastung der Leiterplatte konzentriert, die nächste Studie befasst sich jedoch speziell mit Schockausfällen. Solche Methoden werden hier nicht vollständig erörtert, da sie unter die Klassifizierung von PoF-Methoden fallen und in den Abschnitten 8.1 und 8.2 dieses Artikels erörtert werden. Hin et al. [24] erstellten eine Testplatine, um die Unversehrtheit gelöteter BGA-Verbindungen unter Schlag zu überprüfen. Lau et al. [36] beschrieben die Zuverlässigkeit von PLCC-, PQFP- und QFP-Komponenten, die entlang der Ebene und außerhalb der Ebene beeinflusst werden. Pitarresi et al. [53, 55] untersuchten das Versagen von Computer-Motherboards aufgrund von Stoßbelastungen und gaben einen guten Überblick über die Literatur, die elektronische Geräte unter Stoßbelastung beschreibt. Steinberg [62] enthält ein ganzes Kapitel zum Entwurf und zur Analyse von gestörten elektronischen Geräten, wobei sowohl Methoden zur Vorhersage des Stoßmediums als auch Methoden zur Gewährleistung der Funktionsfähigkeit elektronischer Komponenten berücksichtigt werden. Sukhir [64.65] beschrieb Fehler in linearen Berechnungen der Reaktion der Leiterplatte auf die Stoßbelastung der Leiterplattenhalterungen. So können Referenzmethoden und experimentelle Datenmethoden aufprallbedingte Geräteausfälle berücksichtigen, aber "Schock" -Fehler werden in diesen Methoden implizit beschrieben.

5. Referenzmethoden

Von den in den Handbüchern beschriebenen verfügbaren Methoden beschränken wir uns auf nur zwei, die Vibrationsfehler berücksichtigen: Mil-Hdbk-217 und CNET [9]. Mil-Hdbk-217 wird von den meisten Herstellern als Referenz akzeptiert. Wie alle Methoden aus Handbüchern und Handbüchern basieren sie auf empirischen Ansätzen, die darauf abzielen, die Zuverlässigkeit einer Komponente aus experimentellen oder Labordaten vorherzusagen. Die in der Referenzliteratur beschriebenen Verfahren sind relativ einfach zu implementieren, da sie keine komplexe mathematische Modellierung erfordern, nur Arten von Teilen, Anzahl von Teilen, Betriebsbedingungen der Platine und andere leicht zugängliche Parameter verwenden. Die Eingabe wird dann in das Modell eingegeben, um MTBF - MTBF zu berechnen. Trotz seiner Vorteile wird Mil-Hdbk-217 immer weniger populär [12, 17,42,50,51]. Betrachten Sie eine unvollständige Liste von Einschränkungen für die Anwendbarkeit.

- Die Daten sind seit ihrer letzten Aktualisierung im Jahr 1995 zunehmend veraltet und beziehen sich nicht auf neue Komponenten. Es besteht keine Chance, das Modell zu überarbeiten, da der Rat zur Verbesserung der Verteidigungsstandards beschlossen hat, die Methode „durch natürlichen Tod sterben zu lassen“ [26].

- Das Verfahren liefert keine Informationen über den Fehlermodus, daher kann das Layout der Leiterplatte nicht verbessert oder optimiert werden.

- Modelle gehen davon aus, dass der Fehler unabhängig vom Design ist, wobei die Position der Komponenten auf der Leiterplatte ignoriert wird. Es ist jedoch bekannt, dass das Layout der Komponenten einen großen Einfluss auf die Ausfallwahrscheinlichkeit hat. [50].

- Die gesammelten empirischen Daten enthalten viele Ungenauigkeiten, wobei Daten von Bauteilen der ersten Generation mit einer unnatürlich hohen Ausfallrate aufgrund fehlerhafter Aufzeichnungen von Betriebszeiten, Reparaturen usw. verwendet werden, was die Zuverlässigkeit der Ergebnisse der Zuverlässigkeitsvorhersage verringert [51].

All diese Mängel weisen darauf hin, dass die Verwendung von Referenzmethoden vermieden werden sollte. Im Rahmen der Zulässigkeit dieser Methoden sollten jedoch eine Reihe von Anforderungen der technischen Spezifikationen umgesetzt werden. Daher sollten Referenzmethoden nur verwendet werden, wenn dies angemessen ist, d.h. in den frühen Stadien des Designs [46]. , , 1995 . , - .

6.

. , . (MTTF, ), [26]. .

, . , , . . , [70,71]. , , . , , . .

, , , , , , . Hart [23], Hin et al. [24], [37], . [36], . [57], Liguore Followell [40], . [15], Wang . [67], Jih Jung [30]. IEEE [26].

7.

, . , . : . , ; , . , , , , , . , , .

(HALT) , , [27]. [27], , MTBF , , . [11,17,20,26].

8. (PoF)

, , PoF, . , , . , . , .

, . [15,36,37,67], , [40], , [62] [59], , .

, [21,38], , , , . , ( , ) , .

SMT, , . , , .

PoF, PoF, FE ( ), . , , , , PoF . PoF [17,19,26,49].

8.1.

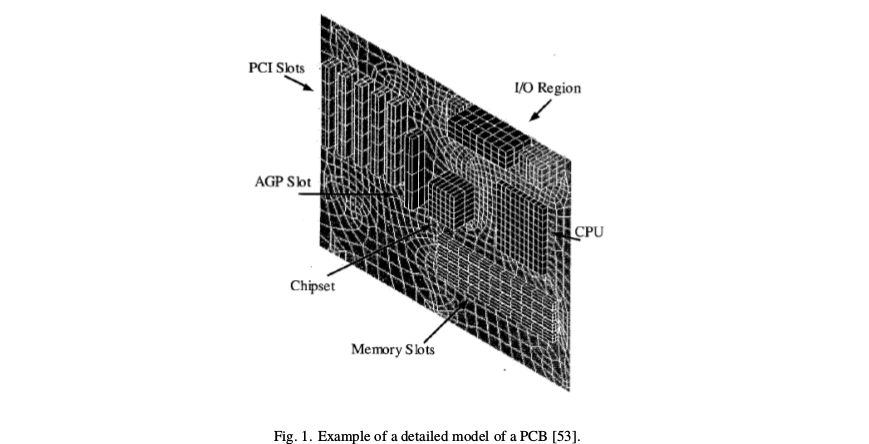

. , , . : , FE FE, . , , ( 8.1.4). . 1. [53].

8.1.1.

[62] . , ; . , , . , .

, . [53] 2% , 3,5% ( 54 ), .

8.1.2. FE

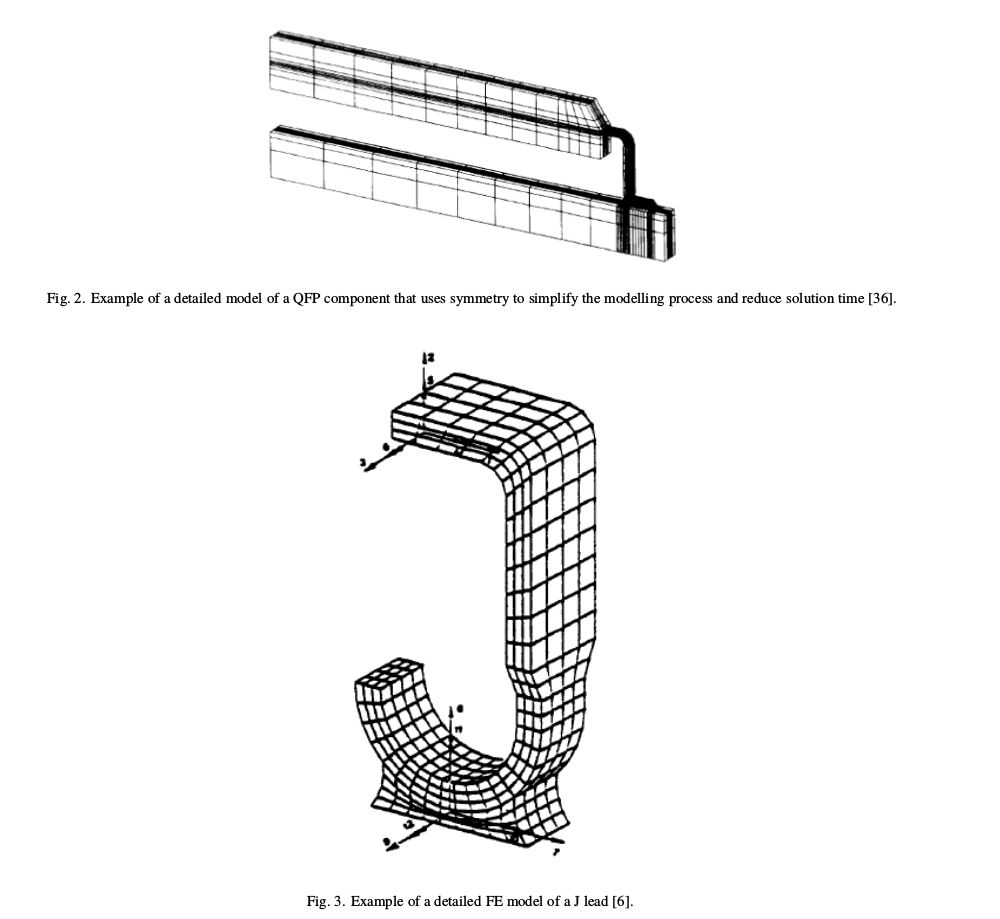

FE [30,37,53, 57,58] ( . 1-3 ), ( ), , , . . , FE , JEDEC 4, [33-35], FE . , ( ), , . , FE , , , , .

8.1.3. FE

FE . , .

. 2. QFP, [36]. . 3. FE- J- [6].

[52]. Pitarresi . [52,54] , , .

FE- , . , , .

, . . . M ( ) . , , M , . , Cifuentes [10] .

- 90% .

- , , , .

- .

- , .

8.1.4.

[59], , . ( ) , , . [5] , , . , . , . , . Lim et al. [41] , FE PCB; , Barker Chen [5]. , - , . , , [21]; Aglietti [2]; Aglietti Schwingshackl [3], Lim . [41].

8.1.5.

Pitarresi . [53-55] FE- PCB , , 3D — . . (SRS) , .

8.2.

, (MTBF), , (. IEEE [26]; Jensen [28]; O'Connor [47] ). . . , - ( , ), , , . .

8.2.1.

Wie bereits erwähnt, besteht die Einschränkung der meisten empirischen Modelle darin, dass sie nur für Konfigurationen anwendbar sind, die die gleiche Dicke der Leiterplatte, ähnliche Arten von Bauteilen und Eingangsbelastung aufweisen, was unwahrscheinlich ist. Die verfügbare Literatur ist jedoch aus folgenden Gründen nützlich: Sie bietet gute Beispiele für Fehlertests, zeigt verschiedene Optionen für Fehlermetriken auf und liefert wertvolle Informationen über die Mechanik von Fehlern. Lee [37] erstellte ein empirisches Modell zur Vorhersage der Zuverlässigkeit von 272-Pin-BGA- und 160-Pin-QFP-Gehäusen. Das Ermüdungsversagen in den Leitern und im Gehäusekörper wird untersucht. Die experimentellen Ergebnisse stimmen gut mit der Schadensanalyse auf der Grundlage von Spannungen überein, die mit dem detaillierten FE-Modell berechnet wurden (siehe auch Li und Poglitsch [38, 39]). Der Prozess führt zu einer kumulativen Schädigung eines bestimmten Pegels der Vibrationsbeschleunigung des Eingangsvibrationssignals.

Lau et al. [36] schätzten die Zuverlässigkeit bestimmter Komponenten unter Schock- und Vibrationsbelastung mithilfe von Weibull-Statistiken. Liguore und Followell [40] untersuchten das Versagen von LLCC- und J-Blei-Bauteilen, indem sie die lokale Beschleunigung in den Betriebszyklen änderten. Die lokale Beschleunigung wird im Gegensatz zur Eingangsbeschleunigung des Chassis verwendet, außerdem wurde der Einfluss der Temperatur auf die Testergebnisse untersucht. Der Artikel bezieht sich auch auf die Untersuchung des Einflusses der Leiterplattendicke auf die Zuverlässigkeit von Bauteilen.

Guo und Zhao [21] vergleichen die Zuverlässigkeit von Bauteilen bei Verwendung der lokalen Torsionskrümmung als Last im Gegensatz zu früheren Studien, bei denen die Beschleunigung verwendet wurde. Ermüdungsschäden werden simuliert und das FE-Modell mit experimentellen Ergebnissen verglichen. Der Artikel beschreibt auch die Optimierung der Anordnung der Komponenten, um die Zuverlässigkeit zu erhöhen.

Ham und Lee [22] stellten eine Testdatenmethode zur Bestimmung von Bleilotspannungen unter zyklischer Torsionsbelastung vor. Estes und Mitarbeiter [15] untersuchten das Problem des Versagens der Komponenten des „Möwenflügels“ (GOST IEC 61188-5-5-2013) bei angelegter Eingangsbeschleunigung und thermischer Belastung. Die untersuchten Komponenten sind die Gehäusetypen CQFP 352, 208, 196, 84 und 28 sowie FP 42 und 10. Der Artikel befasst sich mit dem Versagen elektronischer Komponenten aufgrund von Schwingungen in der Umlaufbahn des geostationären Erdsatelliten. Die MTBF wird in Bezug auf die geostationären Flugjahre oder angegeben niedrige Erdumlaufbahnen. Es ist anzumerken, dass das Versagen der Drähte des "Möwenflügels" an Stellen, die mit dem Gehäusekörper in Kontakt stehen, wahrscheinlicher ist als bei einer Lötverbindung.

Jih und Jung [30] untersuchen Geräteausfälle, die auf angeborene Herstellungsfehler in einer Lötstelle zurückzuführen sind. Dazu wird ein sehr detailliertes FE-Modell der Leiterplatte erstellt und die Leistungsspektraldichte (PSD) für verschiedene Längen von Produktionsrissen ermittelt. Ligyore, Followell [40] und Shetty, Reinikainen [58] haben vorgeschlagen, dass empirische Methoden die genauesten und nützlichsten Fehlerdaten für bestimmte Konfigurationen verbundener Komponenten liefern. Solche Methoden kommen zum Einsatz, wenn bestimmte Eingangsdaten (Plattendicke, Bauteiltyp, Krümmungsbereich) für die gesamte Konstruktionszeit als konstant angenommen werden können oder wenn sich der Anwender echte Tests dieser Art leisten kann.

8.2.2. Analytisches Fehlerkriterium

Modelle mit SMT-EckverbindungVerschiedene Forscher, die Fehler an SMT-Eckklemmen untersuchen, schlagen vor, dass dies die häufigste Fehlerursache ist. Artikel von Sidhart und Barker [59] vervollständigen eine frühere Reihe von Arbeiten, in denen ein Modell zur Bestimmung der Verformung von Winkelleitungen von SMT- und Konturleitungskomponenten vorgestellt wird. Das vorgeschlagene Modell weist im Vergleich zum detaillierten FE-Modell für die sechs Worst-Case-Szenarien einen Fehler von weniger als 7% auf. Das Modell basiert auf einer zuvor von Barker und Sidhart [4] veröffentlichten Formel, bei der die Durchbiegung des Anbauteils unter dem Einfluss eines Biegemoments simuliert wurde. Suhiras Arbeit [63] analysiert analytisch die Spannungen, die bei Paketausgaben aufgrund lokal angewandter Biegemomente zu erwarten sind. Barker und Sidhart [4] stützen sich auf die Arbeit von Suhir [63], Barker et al. [4], die den Einfluss der führenden Rotationssteifigkeit berücksichtigt. Schließlich verwendeten Barker et al. [7] detaillierte FE-Modelle, um den Effekt von Dimensionsänderungen in Blei auf die Lebensdauer von Blei zu untersuchen.

An dieser Stelle sei auf die Arbeit mit den JEDEC-Bleifederkonstanten hingewiesen, aufgrund derer die Erstellung von Modellen für Bleikomponenten stark vereinfacht wurde [33–35]. Federkonstanten können anstelle eines detaillierten Modells von Bleiverbindungen verwendet werden, während das Modell die Zeit zum Erstellen und Lösen des FE-Modells verkürzt. Die Verwendung solcher Konstanten im Bauteil-FE-Modell verhindert die direkte Berechnung lokaler Leitspannungen. Stattdessen wird eine allgemeine Verformung der Zuleitung angegeben, die entweder mit lokalen Zuleitungsspannungen oder mit Zuleitungsfehlerkriterien auf der Grundlage des Produktlebenszyklus verbunden sein muss.

MaterialermüdungsdatenDie meisten Daten zur Zerstörung von Materialien, die für Lote und Bauteile verwendet werden, beziehen sich hauptsächlich auf thermische Brüche, und es gibt relativ wenige Daten zu Ermüdungsbrüchen. Die Hauptreferenz zu diesem Bereich liefert Sandor [56], der Daten zur Mechanik von Ermüdung und Bruch von Loten liefert. Steinberg [62] befasst sich mit der Zerstörung von Lotproben. Ermüdungsdaten für Standardlote und -drähte sind in einem Artikel von Yamada [69] verfügbar.

Figur 4. Der übliche Fehlerstatus des Handbuchs für QFP-Komponenten befindet sich in der Nähe des Verpackungskörpers.

Modellierungsfehler, die mit dem Löten einhergehen, sind aufgrund der ungewöhnlichen Eigenschaften dieses Materials eine Herausforderung. Die Lösung dieser Frage hängt von der Komponente ab, die getestet werden muss. Es ist bekannt, dass dies bei QFP-Paketen normalerweise nicht berücksichtigt wird und die Zuverlässigkeit aus der Referenz- und Zulassungsliteratur geschätzt wird. Wenn jedoch das Löten von BGA, PGA von großen Bauteilen berechnet wird, können Bleiverbindungen aufgrund ihrer ungewöhnlichen Eigenschaften das Produktversagen beeinflussen. Daher sind für QFP-Pakete die Ermüdungseigenschaften von Blei die nützlichste Information. Für BGA sind Informationen zur Haltbarkeit von Lötstellen, die einer sofortigen plastischen Verformung ausgesetzt sind, nützlicher [14]. Für größere Bauteile liefert Steinberg [62] Daten zur Zugspannung von Lötstellen.

Modelle mit schwerem KomponentenversagenDie einzigen Bruchmodelle, die für schwere Bauteile existieren, werden in einem Artikel von Steinberg [62] vorgestellt, in dem die Zugfestigkeit von Bauteilen untersucht und ein Beispiel für die Berechnung der maximal zulässigen Spannung angegeben wird, die auf eine Bleiverbindung angewendet werden kann

8.3. Schlussfolgerungen zur Anwendbarkeit von PoF-Modellen

Die folgenden Schlussfolgerungen in Bezug auf PoF-Methoden wurden in der Literatur gemacht.

Lokale Reaktionen sind entscheidend für die Vorhersage von Komponentenfehlern. Wie in Li, Poglitsch [38] erwähnt, sind Bauteile an den Rändern einer Leiterplatte aufgrund lokaler Biegeunterschiede weniger störanfällig als solche, die sich in der Mitte einer Leiterplatte befinden. Daher weisen Komponenten an unterschiedlichen Stellen auf der Leiterplatte unterschiedliche Ausfallwahrscheinlichkeiten auf.

Die lokale Krümmung der Platine wird als ein wichtigeres Ausfallkriterium angesehen als die Beschleunigung für SMT-Bauteile. Neuere Veröffentlichungen [38, 57, 62, 67] zeigen, dass die Krümmung der Platine das Hauptkriterium für ein Versagen ist.

Verschiedene Pakettypen, sowohl hinsichtlich der Anzahl der Ausgaben als auch des verwendeten Typs, sind von Natur aus zuverlässiger als andere, unabhängig von der spezifischen lokalen Umgebung [15.36.38].

Die Temperatur kann die Zuverlässigkeit der Komponenten beeinträchtigen. Liguore und Followell [40] gaben an, dass die Ermüdungslebensdauer im Temperaturbereich von 0 ° C bis 65 ° C am höchsten ist und bei Temperaturen unter -30 ° C und über 95 ° C spürbar abnimmt. Bei QFP-Bauteilen wird die Stelle, an der der Draht mit dem Beutel verbunden ist (siehe Abb. 4), als Hauptschadensstelle und nicht als Lötstelle angesehen [15,22,38].

Die Dicke der Platte hat einen gewissen Einfluss auf die Lebensdauer von SMT-Bauteilen, da die Lebensdauer des BGA nachweislich um das 30- bis 50-fache abnimmt, wenn die Dicke der Platte von 0,85 mm auf 1,6 mm zunimmt (unter Beibehaltung einer konstanten Gesamtkrümmung). [13] Die Flexibilität (Biegsamkeit) der Zuleitungen beeinflusst die Zuverlässigkeit der peripheren Zuleitungskomponenten erheblich [63], dies ist jedoch eine nichtlineare Abhängigkeit, und die Schlussfolgerungen der Zwischenverbindung der Elemente sind am wenigsten zuverlässig.

8.4. Software-Methoden

Das Life-Cycle-Technologie-Kompetenzzentrum (CALCE) an der University of Maryland bietet Software zur Berechnung der Schwingungs- und Stoßantwort von Leiterplatten. Die Software (CALCE PWA) verfügt über eine Benutzeroberfläche, die das Starten des FE-Modells vereinfacht und die Antwortberechnung automatisch in das Vibrationsmodell eingibt. Es werden keine Annahmen zur Erstellung des FE-Antwortmodells verwendet, und die verwendeten Ablehnungskriterien stammen von Steinberg [61] (obwohl auch die Barkers-Methode [48] implementiert werden soll). Um allgemeine Empfehlungen zur Verbesserung der Zuverlässigkeit von Geräten zu geben, liefert die beschriebene Software gute Ergebnisse, zumal sie gleichzeitig thermisch induzierte Spannungen berücksichtigt und nur minimale Spezialkenntnisse erfordert, die Genauigkeit der Ausfallkriterien in den Modellen jedoch nicht experimentell bestätigt wurde.

9. Methoden zur Verbesserung der Zuverlässigkeit der Ausrüstung

In diesem Abschnitt werden Änderungen nach dem Projekt behandelt, die die Zuverlässigkeit elektronischer Geräte erhöhen. Sie lassen sich in zwei Kategorien einteilen: solche, die die Randbedingungen der Leiterplatte verändern, und solche, die die Dämpfung erhöhen.

Der Hauptzweck der Modifikationen der Randbedingungen ist es, die dynamische Abweichung der Leiterplatte zu verringern, dies kann durch Versteifungsrippen, zusätzliche Abstützungen oder durch Verringerung der Vibration des Eingangsmediums erreicht werden. Versteifungen können nützlich sein, weil sie die Eigenfrequenzen erhöhen und dadurch die dynamische Durchbiegung verringern [62]. Gleiches gilt für das Hinzufügen zusätzlicher Stützen [3], obwohl die Position der Stützen auch optimiert werden kann, wie JH Ong und Lim zeigen [40] Leider erfordern Rippen und Träger in der Regel eine Neugestaltung des Layoutschemas, sodass diese Methoden am besten zu Beginn des Entwurfszyklus in Betracht gezogen werden. Außerdem ist darauf zu achten, dass die Modifikationen die Eigenfrequenzen nicht so verändern, dass sie mit den Eigenfrequenzen der Tragstruktur zusammenfallen, da dies kontraproduktiv wäre.

Das Hinzufügen einer Isolierung kann die Zuverlässigkeit des Produkts verbessern, den Einfluss des auf das Gerät übertragenen dynamischen Mediums verringern und kann entweder passiv oder aktiv erfolgen.

Passive Verfahren sind in der Regel einfach und kostengünstiger zu realisieren, beispielsweise mit Kabelisolatoren [66] oder mit den pseudoelastischen Eigenschaften von Formgedächtnislegierungen (SMA) [32]. Es ist jedoch bekannt, dass schlecht ausgelegte Isolatoren das Ansprechverhalten tatsächlich erhöhen können.

Aktive Methoden bieten eine bessere Dämpfung über einen breiteren Frequenzbereich, in der Regel aufgrund der Einfachheit und Masse. Deshalb sind sie in der Regel darauf ausgelegt, die Genauigkeit sehr empfindlicher Präzisionsinstrumente zu erhöhen und Beschädigungen nicht zu verhindern. Die aktive Schwingungsisolation umfasst elektromagnetische [60] und piezoelektrische Verfahren [18, 43]. Im Gegensatz zu Methoden zur Änderung der Randbedingungen zielt die Dämpfungsänderung darauf ab, die Resonanzspitzenantwort elektronischer Geräte zu verringern, während die tatsächlichen Eigenfrequenzen geringfügig variieren sollten.

Wie bei der Schwingungsisolation kann die Dämpfung sowohl passiv als auch aktiv durchgeführt werden, wobei im ersten Fall eine ähnliche Vereinfachung des Aufbaus und im zweiten Fall eine höhere Komplexität und Dämpfung vorliegt.

Zu den passiven Methoden zählen beispielsweise sehr einfache Methoden wie das Aufkleben von Material, das die Dämpfung der Leiterplatte erhöht [62]. Anspruchsvollere Methoden umfassen die Teilchendämpfung [68] und die Verwendung breitbandiger dynamischer Absorber [25].

Die aktive Vibrationskontrolle wird in der Regel durch die Verwendung von piezokeramischen Elementen erreicht, die auf die Oberfläche der Leiterplatte geklebt sind [1.45]. Die Verwendung von Härtungsmethoden ist fallspezifisch und sollte in Bezug auf andere Methoden sorgfältig abgewogen werden. Das Anwenden dieser Verfahren auf Geräte, von denen bekannt ist, dass sie keine Probleme mit der Zuverlässigkeit haben, erhöht nicht notwendigerweise die Kosten und das Gewicht der Struktur. Wenn jedoch ein Produkt mit einer genehmigten Konstruktion während des Testens einen Fehler aufweist, kann es viel schneller und einfacher sein, die Härtungstechnik anzuwenden, als die Ausrüstung neu zu konstruieren.

10. Möglichkeiten zur Methodenentwicklung

In diesem Abschnitt werden die Möglichkeiten zur Verbesserung der Vorhersage der Zuverlässigkeit elektronischer Geräte beschrieben, auch wenn die jüngsten Fortschritte in den Bereichen Optoelektronik, Nanotechnologie und Verpackungstechnologie die Anwendbarkeit dieser Vorschläge möglicherweise bald einschränken werden. Vier grundlegende Methoden zur Vorhersage der Zuverlässigkeit können zum Zeitpunkt der Entwicklung des Geräts nicht verwendet werden. Der einzige Faktor, der solche Methoden attraktiver machen könnte, wäre die Schaffung vollautomatisierter kostengünstiger Produktions- und Prüftechnologien, da auf diese Weise das vorgeschlagene Design mit minimalem menschlichem Aufwand viel schneller als derzeit erstellt und getestet werden könnte.

Die PoF-Methode bietet viele Verbesserungsmöglichkeiten. Der Hauptbereich, in dem Verbesserungen vorgenommen werden können, ist die Integration in den gesamten Entwurfsprozess. Das Entwerfen elektronischer Geräte ist ein iterativer Prozess, der den Entwickler nur in Zusammenarbeit mit Ingenieuren, die sich auf Elektronik, Fertigungs- und Wärmetechnik sowie Tragwerksplanung spezialisiert haben, näher an das Endergebnis bringt. Eine Methode, die einige dieser Probleme gleichzeitig automatisch behebt, reduziert die Anzahl der Entwurfsiterationen und spart erheblich Zeit, insbesondere unter Berücksichtigung des Umfangs der Zusammenarbeit zwischen Agenturen. Andere Bereiche, in denen die PoF-Techniken verbessert werden sollen, werden in Typen von Antwortvorhersage- und Ausfallkriterien unterteilt.

Für die Antwortvorhersage gibt es zwei mögliche Entwicklungspfade: entweder schnellere, detailliertere Modelle oder verbesserte vereinfachte Modelle. Mit dem Aufkommen immer leistungsfähigerer Computerprozessoren kann die Zeit zum Lösen detaillierter FE-Modelle sehr kurz werden, während moderne Software gleichzeitig die Montagezeit verkürzt, was letztendlich die Personalkosten minimiert. Vereinfachte FE-Methoden können auch durch die automatische Erstellung von FE-Modellen verbessert werden, ähnlich den für detaillierte FE-Methoden angebotenen. Dafür steht derzeit eine automatische Software (CALCE PWA) zur Verfügung, die Technologie ist jedoch in der Praxis nicht ausreichend getestet und die bei der Modellierung getroffenen Annahmen sind unbekannt.

Die Berechnung des Fehlers, der verschiedenen Vereinfachungsmethoden inhärent ist, wäre sehr nützlich, um nützliche Kriterien für die Fehlertoleranz zu implementieren.

Schließlich wäre eine Datenbank oder ein Verfahren nützlich, um angebrachten Bauteilen eine erhöhte Steifigkeit zu verleihen, wobei diese Steifigkeitsverbesserungen verwendet werden könnten, um die Genauigkeit von Antwortmodellen zu verbessern. Die Erstellung von Kriterien für das Versagen von Komponenten hängt von geringfügigen Abweichungen ähnlicher Komponenten verschiedener Hersteller sowie von der möglichen Entwicklung neuer Verpackungstypen ab, da bei jeder Methode oder Datenbank zur Bestimmung von Versagenskriterien diese Abweichungen und Änderungen berücksichtigt werden sollten.

Eine Lösung wäre die Erstellung einer Methode / Software zur automatischen Erstellung detaillierter FE-Modelle auf der Grundlage von Eingabeparametern wie Blei und Packungsgrößen. Ein solches Verfahren kann für Komponenten mit einer im Allgemeinen einheitlichen Form wie SMT- oder DIP-Komponenten durchführbar sein, jedoch nicht für komplexe unregelmäßige Komponenten wie Transformatoren, Drosseln oder nicht standardmäßige Komponenten.

Nachfolgende FE-Modelle können für Spannungen aufgelöst und mit Materialfehlerdaten (S-N-Duktilitätskurvendaten, Bruchmechanik oder dergleichen) kombiniert werden, um die Lebensdauer der Komponenten zu berechnen, obwohl Materialfehlerdaten von hoher Qualität sein müssen. Der FE-Prozess sollte mit realen Testdaten korreliert werden, vorzugsweise in einem möglichst großen Konfigurationsbereich.

Der Aufwand für ein solches Verfahren ist relativ gering im Vergleich zu direkten Labortests, bei denen eine statistisch signifikante Anzahl von Tests für verschiedene Dicken von Leiterplatten, verschiedene Belastungsintensitäten und Richtungen durchgeführt werden sollte. Hunderte verschiedener Arten von Bauteilen sind sogar für verschiedene Arten von Leiterplatten verfügbar. , , .

- , , , . FE , .

, , : FE, , , , . PoF , . , , , , ( ).

, , , , , (), .

11.

, ( - , , PoF), . - , , , , , , .

PF , , . « » , FE. , FE, . « » , SMT .

, , , . . , , , .

[1] GS Aglietti, RS Langley, E. Rogers and SB Gabriel, An efficient model of an equipment loaded panel for active control design studies, The Journal of the Acoustical Society of America 108 (2000), 1663–1673.

[2]GS Aglietti, A lighter enclosure for electronics for space applications, Proceeding of Institute of Mechanical Engineers 216 (2002), 131–142.

[3] GS Aglietti and C. Schwingshackl, Analysis of enclosures and anti vibration devices for electronic equipment for space applications, Proceedings of the 6th International Conference on Dynamics and Control of Spacecraft Structures in Space, Riomaggiore, Italy, (2004).

[4] DB Barker and Y. Chen, Modeling the vibration restraints of wedge lock card guides, ASME Journal of Electronic Packaging 115(2) (1993), 189–194.

[5] DB Barker, Y. Chen and A. Dasgupta, Estimating the vibration fatigue life of quad leaded surface mount components, ASME Journal of Electronic Packaging 115(2) (1993), 195–200.

[6] DB Barker, A. Dasgupta and M. Pecht, PWB solder joint life calculations under thermal and vibrational loading, Annual Reliability and Maintainability Symposium, 1991 Proceedings (Cat. No.91CH2966-0), 451–459.

[7] DB Barker, I. Sharif, A. Dasgupta and M. Pecht, Effect of SMC lead dimensional variabilities on lead compliance and solder joint fatigue life, ASME Journal of Electronic Packaging 114(2) (1992), 177–184.

[8] DB Barker and K. Sidharth, Local PWB and component bowing of an assembly subjected to a bending moment, American Society of Mechanical Engineers (Paper) (1993), 1–7.

[9] J. Bowles, A survey of reliability-prediction procedures for microelectronic devices, IEEE Transactions on Reliability 41(1) (1992), 2–12.

[10] AO Cifuentes, Estimating the dynamic behavior of printed circuit boards, IEEE Transactions on Components, Packaging, and Manufacturing Technology Part B: Advanced Packaging 17(1) (1994), 69–75.

[11] L. Condra, C. Bosco, R. Deppe, L. Gullo, J. Treacy and C. Wilkinson, Reliability assessment of aerospace electronic equipment, Quality and Reliability Engineering International 15(4) (1999), 253–260.

[12] MJ Cushing, DE Mortin, TJ Stadterman and A. Malhotra, Comparison of electronics-reliability assessment approaches, IEEE Transactions on Reliability 42(4) (1993), 542–546.

[13] R. Darveaux and A. Syed, Reliability of area array solder joints in bending, SMTA International Proceedings of the Technical Program (2000), 313–324.

[14] NF Enke, TJ Kilinski, SA Schroeder and JR Lesniak, Mechanical behaviors of 60/40 tin-lead solder lap joints, Proceedings – Electronic Components Conference 12 (1989), 264–272.

[15] T. Estes, W. Wong, W. McMullen, T. Berger and Y. Saito, Reliability of class 2 heel fillets on gull wing leaded components. Aerospace Conference, Proceedings 6 (2003), 6-2517–6 C2525

[16] FIDES, FIDES Guide 2004 issue A Reliability Methodology for Electronic Systems. FIDES Group, 2004.

[17] B. Foucher, D. Das, J. Boullie and B. Meslet, A review of reliability prediction methods for electronic devices, Microelectronics Reliability 42(8) (2002), 1155–1162.

[18] J. Garcia-Bonito, M. Brennan, S. Elliott, A. David and R. Pinnington, A novel high-displacement piezoelectric actuator for active vibration control, Smart Materials and Structures 7(1) (1998), 31–42.

[19] W. Gericke, G. Gregoris, I. Jenkins, J. Jones, D. Lavielle, P. Lecuyer, J. Lenic, C. Neugnot, M. Sarno, E. Torres and E. Vergnault, A methodology to assess and select a suitable reliability prediction method for eee components in space applications, European Space Agency, (Special Publication) ESA SP (507) (2002), 73–80.

[20] L. Gullo, In-service reliability assessment and top-down approach provides alternative reliability prediction method. Annual Reliability and Maintainability, Symposium Proceedings (Cat. No.99CH36283), 1999, 365–377.

[21] Q. Guo and M. Zhao, Fatigue of SMT solder joint including torsional curvature and chip location optimization, International Journal of Advanced Manufacturing Technology 26(7–8) (2005), 887–895.

[22] S.-J. Ham and S.-B. Lee, Experimental study for reliability of electronic packaging under vibration, Experimental Mechanics 36(4) (1996), 339–344.

[23] D. Hart, Fatigue testing of a component lead in a plated through hole, IEEE Proceedings of the National Aerospace and Electronics Conference (1988), 1154–1158.

[24] TY Hin, KS Beh and K. Seetharamu, Development of a dynamic test board for FCBGA solder joint reliability assessment in shock & vibration. Proceedings of the 5th Electronics Packaging Technology Conference (EPTC 2003), 2003, 256–262.58

[25] V. Ho, A. Veprik and V. Babitsky, Ruggedizing printed circuit boards using a wideband dynamic absorber, Shock and Vibration 10(3) (2003), 195–210.

[26] IEEE, IEEE guide for selecting and using reliability predictions based on ieee 1413, 2003, v+90 C.

[27] T. Jackson, S. Harbater, J. Sketoe and T. Kinney, Development of standard formats for space systems reliability models, Annual Reliability and Maintainability Symposium, 2003 Proceedings (Cat. No.03CH37415), 269–276.

[28] F. Jensen, Electronic Component Reliability, Wiley, 1995.

[29] JH Ong and G. Lim, A simple technique for maximising the fundamental frequency of structures, ASME Journal of Electronic Packaging 122 (2000), 341–349.

[30] E. Jih and W. Jung, Vibrational fatigue of surface mount solder joints. IThermfl98. Sixth Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (Cat. No.98CH36208), 1998, 246–250.

[31] B. Johnson and L. Gullo, Improvements in reliability assessment and prediction methodology. Annual Reliability and Maintainability Symposium. 2000 Proceedings. International Symposium on Product Quality and Integrity (Cat. No. 00CH37055), 2000, -:181–187.

[32] M. Khan, D. Lagoudas, J. Mayes and B. Henderson, Pseudoelastic SMA spring elements for passive vibration isolation: part i modeling, Journal of Intelligent Material Systems and Structures 15(6) (2004), 415–441.

[33] R. Kotlowitz, Comparative compliance of representative lead designs for surface-mounted components, IEEE Transactions on Components, Hybrids, and Manufacturing Technology 12(4) (1989), 431–448.

[34] R. Kotlowitz, Compliance metrics for surface mount component lead design. 1990 Proceedings. 40th Electronic Components and Technology Conference (Cat. No. 90CH2893-6), 1990, 1054–1063.

[35] R. Kotlowitz and L. Taylor, Compliance metrics for the inclined gull-wing, spider j-bend, and spider gull-wing lead designs for surface mount components. 1991 Proceedings. 41st Electronic Components and Technology Conference (Cat. No. 91CH2989-2), 1991, 299–312.

[36] J. Lau, L. Powers-Maloney, J. Baker, D. Rice and B. Shaw, Solder joint reliability of fine pitch surface mount technology assemblies, IEEE Transactions on Components, Hybrids, and Manufacturing Technology 13(3) (1990), 534–544.

[37] R. Li, A methodology for fatigue prediction of electronic components under random vibration load, ASME Journal of Electronic Packaging 123(4) (2001), 394–400.

[38] R. Li and L. Poglitsch, Fatigue of plastic ball grid array and plastic quad flat packages under automotive vibration. SMTA International, Proceedings of the Technical Program (2001), 324–329.

[39] R. Li and L. Poglitsch, Vibration fatigue, failure mechanism and reliability of plastic ball grid array and plastic quad flat packages.

[40] Proceedings 2001 HD International Conference on High-Density Interconnect and Systems Packaging (SPIE Vol. 4428), 2001, 223–228.

[41] S. Liguore and D. Followell, Vibration fatigue of surface mount technology (smt) solder joints. Annual Reliability and Maintainability Symposium 1995 Proceedings (Cat. No. 95CH35743), 1995, -:18–26.

[42] G. Lim, J. Ong and J. Penny, Effect of edge and internal point support of a printed circuit board under vibration, ASME Journal of Electronic Packaging 121(2) (1999), 122–126.

[43] P. Luthra, Mil-hdbk-217: What is wrong with it? IEEE Transactions on Reliability 39(5) (1990), 518.

[44] J. Marouze and L. Cheng, A feasibility study of active vibration isolation using thunder actuators, Smart Materials and Structures 11(6) (2002), 854–862.

[45] MIL-HDBK-217F. Reliability Prediction of Electronic Equipment. US Department of Defense, F edition, 1995.

[46] SR Moheimani, A survey of recent innovations in vibration damping and control using shunted piezoelectric transducers, IEEE Transactions on Control Systems Technology 11(4) (2003), 482–494.

[47] S. Morris and J. Reilly, Mil-hdbk-217-a favorite target. Annual Reliability and Maintainability Symposium. 1993 Proceedings (Cat. No.93CH3257-3), (1993), 503–509.

P. O'Connor, Practical reliability engineering. Wiley, 1997.

[48] M. Osterman and T. Stadterman, Failure assessment software for circuit card assemblies. Annual Reliability and Maintainability. Symposium. 1999 Proceedings (Cat. No.99CH36283), 1999, 269–276.

[49] M. Pecht and A. Dasgupta, Physics-of-failure: an approach to reliable product development, IEEE 1995 International Integrated Reliability Workshop Final Report (Cat. No. 95TH8086), (1999), 1–4.

[50] M. Pecht and W.-C. Kang, A critique of mil-hdbk-217e reliability prediction methods, IEEE Transactions on Reliability 37(5) (1988), 453–457.

[51] MG Pecht and FR Nash, Predicting the reliability of electronic equipment, Proceedings of the IEEE 82(7) (1994), 992–1004.

[52] J. Pitarresi, D. Caletka, R. Caldwell and D. Smith, The smeared property technique for the FE vibration analysis of printed circuit cards, ASME Journal of Electronic Packaging 113 (1991), 250–257.

[53] J. Pitarresi, P. Geng, W. Beltman and Y. Ling, Dynamic modeling and measurement of personal computer motherboards. 52nd Electronic Components and Technology Conference 2002., (Cat. No. 02CH37345)(-), 2002, 597–603.

[54] J. Pitarresi and A. Primavera, Comparison of vibration modeling techniques for printed circuit cards, ASME Journal of Electronic Packaging 114 (1991), 378–383.

[55] J. Pitarresi, B. Roggeman, S. Chaparala and P. Geng, Mechanical shock testing and modeling of PC motherboards. 2004 Proceedings, 54th Electronic Components and Technology Conference (IEEE Cat. No. 04CH37546) 1 (2004), 1047–1054.

[56] BI Sandor, Solder Mechanics – A State of the Art Asssessment. The Minerals, Metals and Materials Society, 1991.

[57] S. Shetty, V. Lehtinen, A. Dasgupta, V., Halkola and T. Reinikainen, Fatigue of chip scale package interconnects due to cyclic bending, ASME Journal of Electronic Packaging 123(3) (2001), 302–308.

[58] S. Shetty and T. Reinikainen, Three- and four-point bend testing for electronic packages, ASME Journal of Electronic Packaging 125(4) (2003), 556–561.

[59] K. Sidharth and DB Barker, Vibration induced fatigue life estimation of corner leads of peripheral leaded components, ASME Journal of Electronic Packaging 118(4) (1996), 244–249.

[60] J. Spanos, Z. Rahman and G. Blackwood, Soft 6- axis active vibration isolator, Proceedings of the American Control Conference 1 (1995), 412–416.

[61] D. Steinberg, Vibration Analysis for Electronic Equipment, John Wiley & Sons, 1991.

[62] D. Steinberg, Vibration Analysis for Electronic Equipment, John Wiley & Sons, 2000.

[63] E. Suhir, Could compliant external leads reduce the strength of a surface-mounted device? 1988 Proceedings of the 38th Electronics Components Conference (88CH2600-5), 1988, 1–6.

[64] E. Suhir, Nonlinear dynamic response of a printed circuit board to shock loads applied to its support contour, ASME Journal of Electronic Packaging 114(4) (1992), 368–377.

[65] E. Suhir, Response of a flexible printed circuit board to periodic shock loads applied to its support contour, American Society of Mechanical Engineers (Paper) 59(2) (1992), 1–7.

[66] A. Veprik, Vibration protection of critical components of electronic equipment in harsh environmental conditions, Journal of Sound and Vibration 259(1) (2003), 161–175.

[67] H. Wang, M. Zhao and Q. Guo, Vibration fatigue experiments of SMT solder joint, Microelectronics Reliability 44(7) (2004), 1143–1156.

[68] ZW Xu, K. Chan and W. Liao, An empirical method for particle damping design, Shock and Vibration 11(5–6) (2004), 647–664.

[69] S. Yamada, A fracture mechanics approach to soldered joint cracking, IEEE Transactions on Components, Hybrids, and Manufacturing Technology 12(1) (1989), 99–104.

[70] W. Zhao and E. Elsayed, Modelling accelerated life testing based on mean residual life, International Journal of Systems Science 36(11) (1995), 689–696.

[71] W. Zhao, A. Mettas, X. Zhao, P. Vassiliou and EA Elsayed, Generalized step stress accelerated life model. Proceedings of 2004 International Conference on the Business of Electronic Product Reliability and Liability, 2004, 19–25.