Cadence presentará Genus en seminarios sobre desarrollo de chips en San Petersburgo y Zelenograd

Noticias de organizaciones amigas (Cadence, MIET, ITMO, NPC Elvis y otras):Cadence Design Systems, una de las dos compañías mundiales más grandes en el campo de la automatización del desarrollo de microchips, llevará a cabo seminarios del 15 al 16 de octubre en el Instituto de Tecnología Electrónica de Moscú (MIET) en Zelenograd y San Petersburgo ITMO University, donde (según la experiencia de mi viaje en 2012), los estudiantes entienden muy bien Verilog y los sistemas en un chip.Tres empresas rusas Elekropribor, NIIMA Progress y SPC Elvis también participarán en los seminarios. Vea el artículo sobre cooperación con Imagination Technologies del centro de investigación y desarrollo de Elvis relacionado de la organización Elvis-Neotech en el sitio web de Rusnano.Entre las presentaciones, personalmente recomiendo mirar la nueva herramienta de síntesis Genus: vi y filmé su presentación en junio en la Conferencia de automatización de diseño en San Francisco:

El anuncio que recibí sobre el seminario ruso se encuentra a continuación. En la foto de la derecha, estoy en el contexto del edificio MIET en Zelenograd durante un viaje en MIPS Technologies en 2011. Allí, la gente de Cadence realizará uno de los talleres:

Cadence Technology Days 15- 16- . : kustarev@yandex.ru. : dsd@miee.ru.

: , .. 14 « »

:

Technology day at ITMO – Seminar Title:

Virtual Model Prototyping, High Level Synthesis, Synthesis and Digital Implementation by Cadence

9:15 – 9:45 Welcome and Cadence Overview

9:45 – 11:15 Cadence: Virtual Model Prototyping

11:15 -11:30 Break

11:30 – 12:30 Cadence: High Level Synthesis

12:30 – 13:30 Lunch

13:30 – 14:30 Cadence: Genus the new synthesis solution

14:30 – 15:30 Cadence: Innovus – state of the art digital implementation

15:30 – 15:45 Break

15:45 – 16:45 “» — experience with Cadence tools

16:45 – 17:45

17:45 – 18:15 Round table and open discussions with the speakers

:

09:00 – 09:15 .

09:15 – 09:45 Cadence; 0:30 hour.

09:45 – 11:15 Cadence: Virtual Model Prototyping

11:15 – 11:30 – .

11:30 – 12:30 Cadence: High Level Synthesis

12:30 – 13:30 .

13:30 – 14:45 Cadence: Genus the new synthesis solution

14:45 – 15:00 – .

15:00 – 16:15 Cadence: Innovus – state of the art digital implementation

16:15 – 16:45 « «» – Cadence

16:45 – 17:15 «» – Cadence Incisive .

17:15 – 18:00 , .

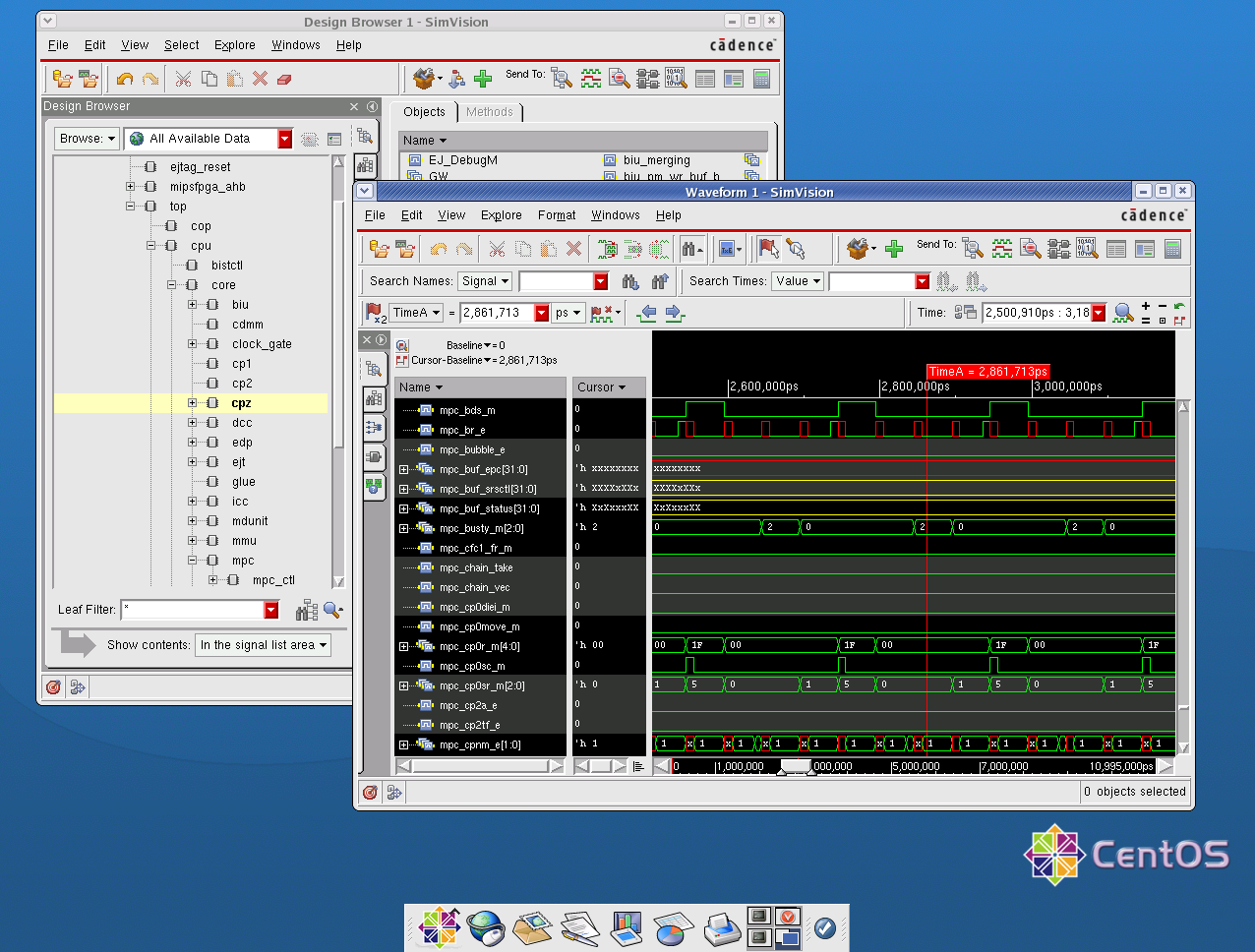

Cadence. MIPS microAptiv UP MIPSfpga SimVision:

Source: https://habr.com/ru/post/es384913/

All Articles