T1: computadora de bricolaje discreta de 8 bits

Siempre ha habido muchos "caseros". Con el advenimiento de la red, los amantes de hacer algo con sus propias manos se organizaron de inmediato y crearon muchos tipos diferentes de comunidades, foros y otros lugares donde puedes chatear con los tuyos. Gracias a esto, regularmente aparecen trabajos interesantes en Internet, algunos de los cuales vale la pena prestar mucha atención.Uno de estos trabajos es, en particular, un proyecto para crear una computadora discreta de 8 bits. El autor del proyecto es Andrew Starr , y el proyecto en sí se encuentra aquí en esta página . ¿Cómo es un proyecto?Según el autor, esto es en parte un ensamblaje cinético, en parte un homenaje a los logros de la ciencia y la tecnología, y los logros de los últimos años. En parte, este es un proyecto educativo.Para crear este sistema, el autor utiliza los siguientes elementos:

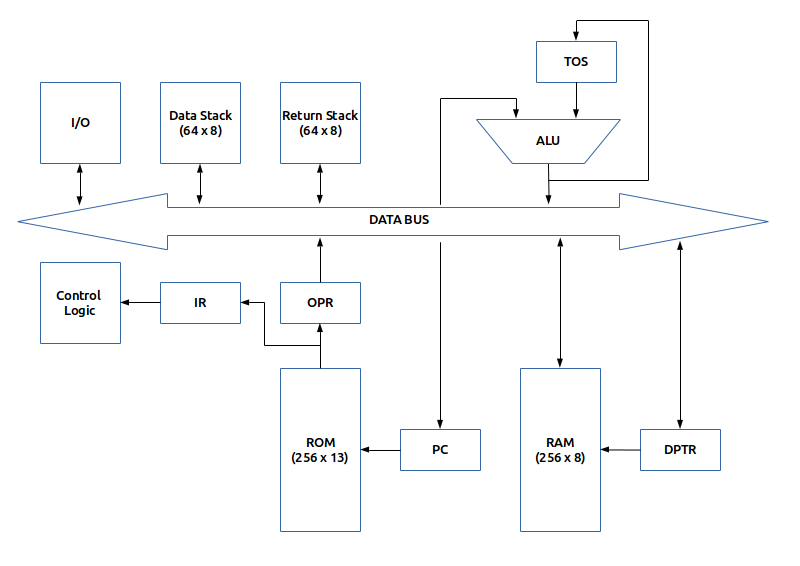

Siempre ha habido muchos "caseros". Con el advenimiento de la red, los amantes de hacer algo con sus propias manos se organizaron de inmediato y crearon muchos tipos diferentes de comunidades, foros y otros lugares donde puedes chatear con los tuyos. Gracias a esto, regularmente aparecen trabajos interesantes en Internet, algunos de los cuales vale la pena prestar mucha atención.Uno de estos trabajos es, en particular, un proyecto para crear una computadora discreta de 8 bits. El autor del proyecto es Andrew Starr , y el proyecto en sí se encuentra aquí en esta página . ¿Cómo es un proyecto?Según el autor, esto es en parte un ensamblaje cinético, en parte un homenaje a los logros de la ciencia y la tecnología, y los logros de los últimos años. En parte, este es un proyecto educativo.Para crear este sistema, el autor utiliza los siguientes elementos:- Bus de 8 bits

- 2 * pilas de 64 bits (datos, retorno);

- Arquitectura de Harvard : memoria principal de 256 bytes y memoria de programa de 256 palabras;

- Palabra de comando de software de 13 bits: 5 bits por código de operación, operando de 8 bits;

- Todos los elementos de memoria están hechos con núcleos de ferrita;

- La memoria del programa se realiza utilizando transformadores de ferrita;

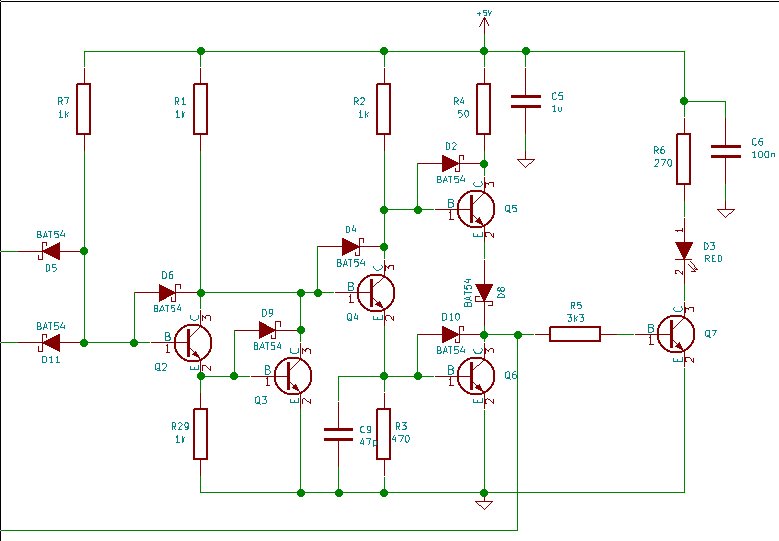

- Los elementos lógicos están hechos de elementos discretos en forma de módulos enchufables;

- La frecuencia del reloj objetivo es de 1 MHz.

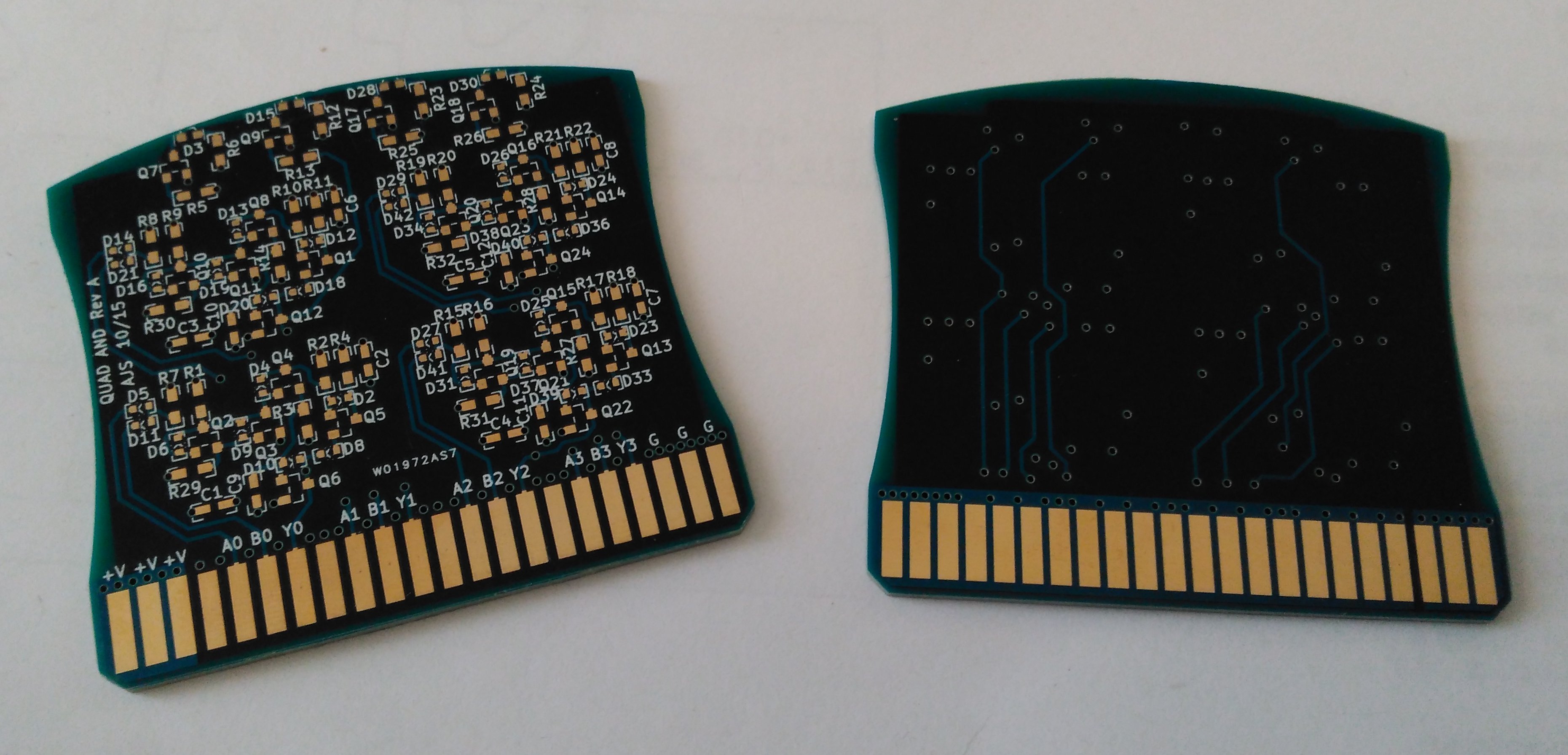

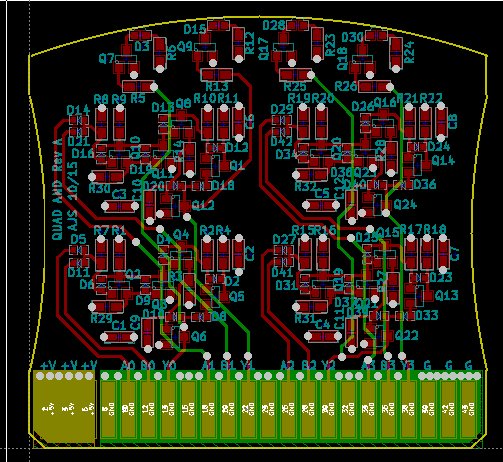

En la arquitectura de Harvard, las características de los dispositivos de memoria para instrucciones y la memoria para datos no necesitan ser las mismas. En particular, el ancho de palabra, la sincronización, la tecnología de implementación y la estructura de la dirección de memoria pueden variar. En algunos sistemas, las instrucciones pueden almacenarse en la memoria de solo lectura, mientras que el almacenamiento de datos generalmente requiere memoria de lectura y escritura. Algunos sistemas requieren mucha más memoria para instrucciones que memoria para datos, ya que los datos generalmente se pueden cargar desde una memoria externa o más lenta. Tal necesidad aumenta el ancho de bit (ancho) del bus de dirección de memoria de instrucciones en comparación con el bus de dirección de memoria de datos.Arquitectura del sistema: Utiliza una máquina estándar de 2 pilas con varias modificaciones que permiten utilizar la arquitectura de Harvard y el campo de datos opcional en las instrucciones.Ahora el autor ya ha desarrollado un esquema de módulo AND y ordenó los módulos apropiados, que llegaron el otro día. Prueba de

Utiliza una máquina estándar de 2 pilas con varias modificaciones que permiten utilizar la arquitectura de Harvard y el campo de datos opcional en las instrucciones.Ahora el autor ya ha desarrollado un esquema de módulo AND y ordenó los módulos apropiados, que llegaron el otro día. Prueba de

esquemas

esquemas

:

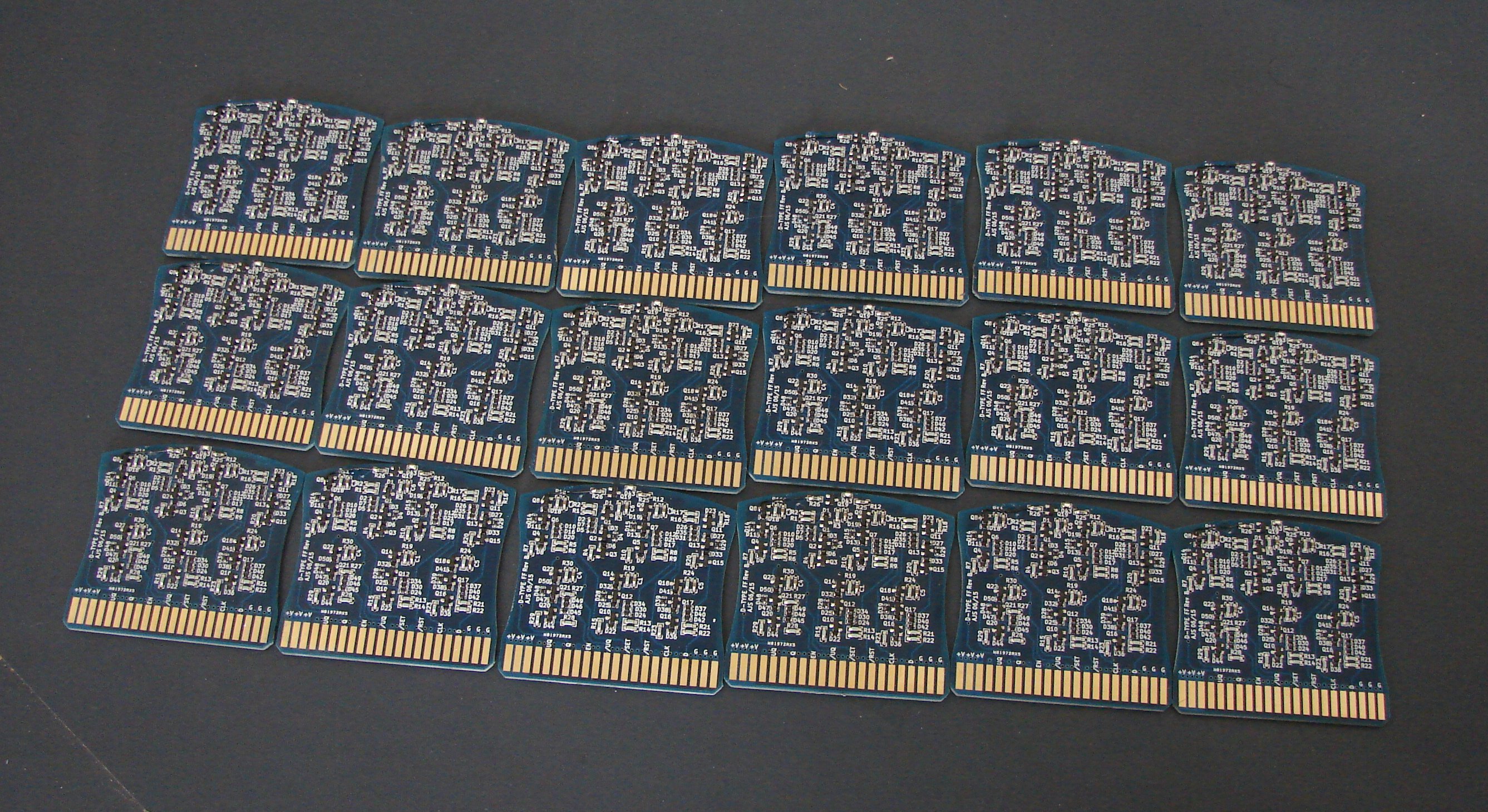

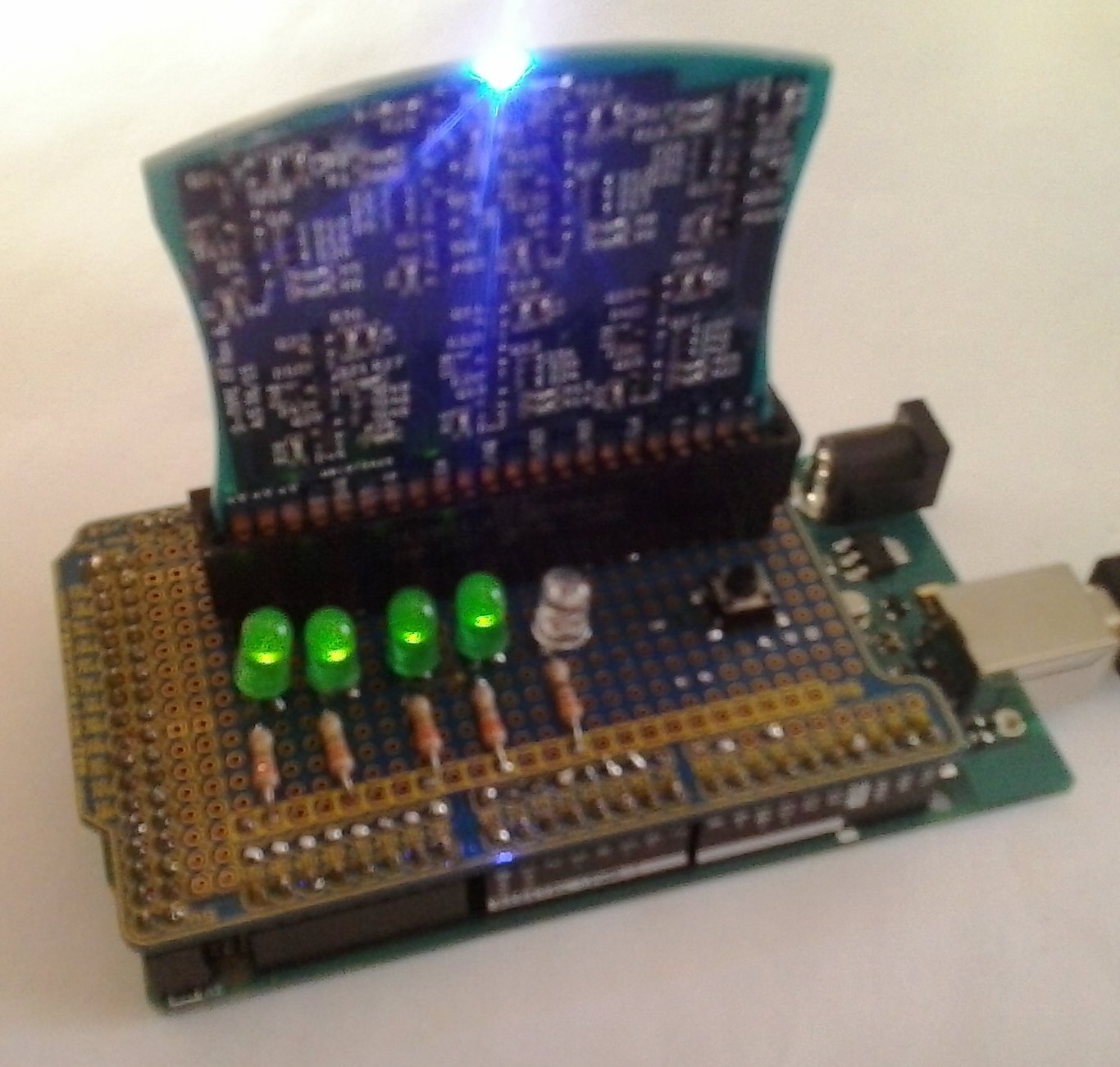

: otros componentes también están listos, incluidos los decodificadores de direcciones para la memoria de la pila.

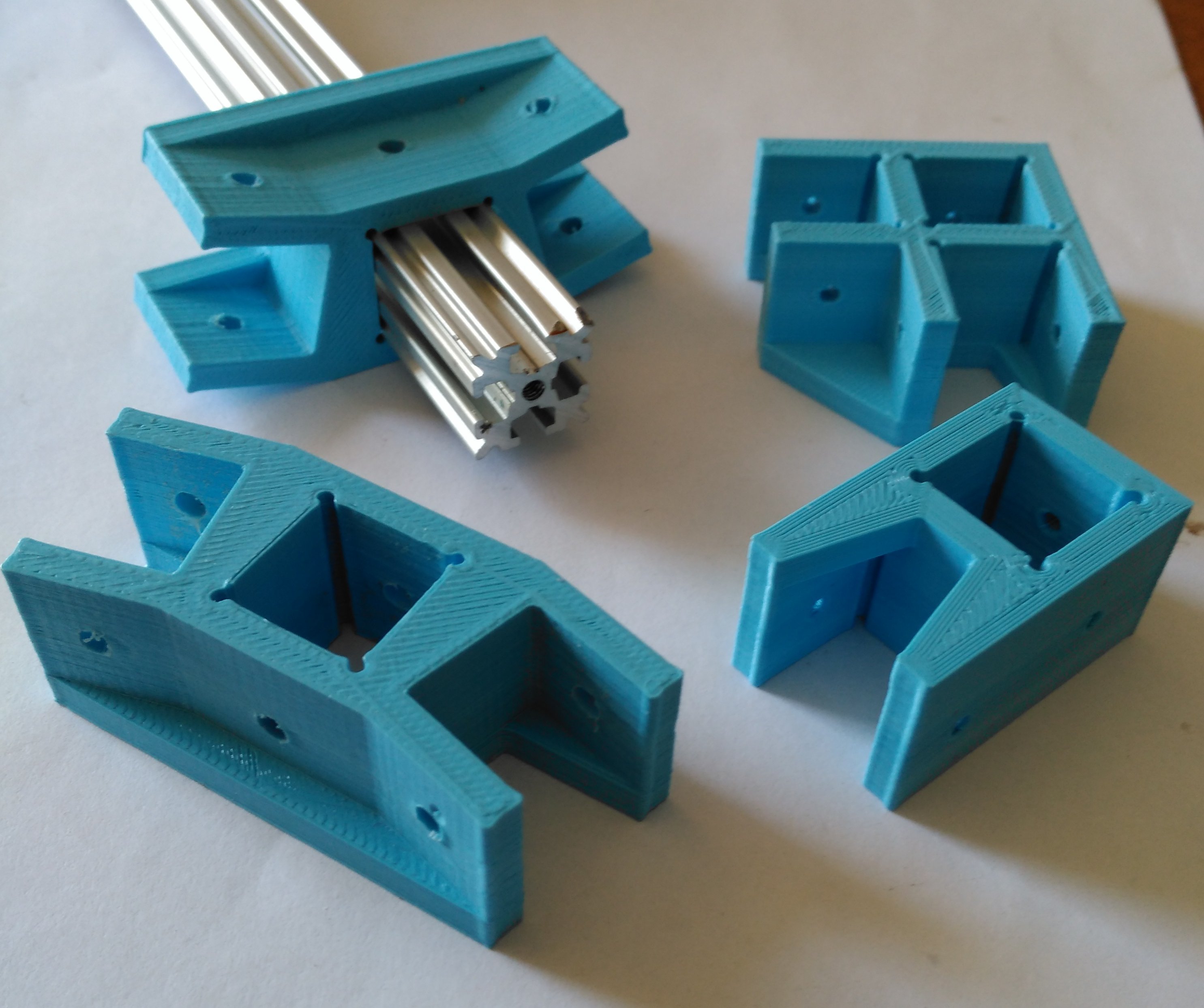

otros componentes también están listos, incluidos los decodificadores de direcciones para la memoria de la pila. Entre otras cosas, el autor también está desarrollando un caso para su creación:

Entre otras cosas, el autor también está desarrollando un caso para su creación: ahora el trabajo aún está en curso, por lo que puede monitorear la implementación del proyecto aquí .

ahora el trabajo aún está en curso, por lo que puede monitorear la implementación del proyecto aquí .Source: https://habr.com/ru/post/es385409/

All Articles