Fotos, materiales y giros y vueltas del seminario MIPSfpga en MEPhI

A finales de octubre, se llevó a cabo un seminario sobre MIPSfpga en MEPhI, uno de una serie de seminarios organizados por universidades rusas junto con Imagination Technologies, Microchip Technology en asociación con Gamma St. Petersburg, representantes del Grupo Macro de Xilinx en Rusia, con la participación de oradores de MathWorks y NIISI. A continuación se muestra una mezcla de fotografías, enlaces a materiales, notas sobre la preparación del seminario y la cultura mítica. A continuación se muestra una imagen de MEPhI afuera. La palabra "nuclear" recuerda que hay un reactor nuclear en el Instituto de Física de Ingeniería de Moscú, por lo que es difícil llegar allí, especialmente con un pasaporte estadounidense. Obtuve un pase durante dos semanas y el rector firmó la orden para el seminario. En la entrada hay un artillero con Kalashnikov (!) (No se me permitió fotografiar al artillero ) Aquí estoy (Yuri Panchul) con otros organizadores del seminario: Igor Ivanovich Shagurin y Maxim Gorbunov: Igor Ivanovich Shagurin, diputado. Jefe del Departamento de Micro y Nanoelectrónica - autor de libros y artículos sobre microprocesadores Intel, Motorola y PowerPC, trabajo de laboratorio en MIPS . UPD: Aclaración de un compañero de NIIIS:

(No se me permitió fotografiar al artillero ) Aquí estoy (Yuri Panchul) con otros organizadores del seminario: Igor Ivanovich Shagurin y Maxim Gorbunov: Igor Ivanovich Shagurin, diputado. Jefe del Departamento de Micro y Nanoelectrónica - autor de libros y artículos sobre microprocesadores Intel, Motorola y PowerPC, trabajo de laboratorio en MIPS . UPD: Aclaración de un compañero de NIIIS:

«, -32 -64 MIPS- — ( :) ). , — MIPS- . RISC , . MIPS-I. , , MIPS- , . , „ MIPS“ MIPS- . „

Curiosamente, Igor Ivanovich Shagurin fue a representar a la electrónica soviética en una conferencia en San Francisco en la década de 1970, cuando la URSS era un país bastante aislado. Los participantes de esa conferencia VLSI en la década de 1970 fueron llevados a Muir Woods, el área con las secuoyas más altas del mundo Sequoia sempervirens Maxim Gorbunov , un investigador de NIISI / SRISA , un instituto que participa en el desarrollo de microprocesadores rusos con arquitectura MIPS - COMDIV-32 y COMISIÓN-64. Maxim se especializa en el diseño de la topología de VLSI resistente a la radiación y fue copresidente de una de las secciones de la conferencia internacional RADECS en Moscú:

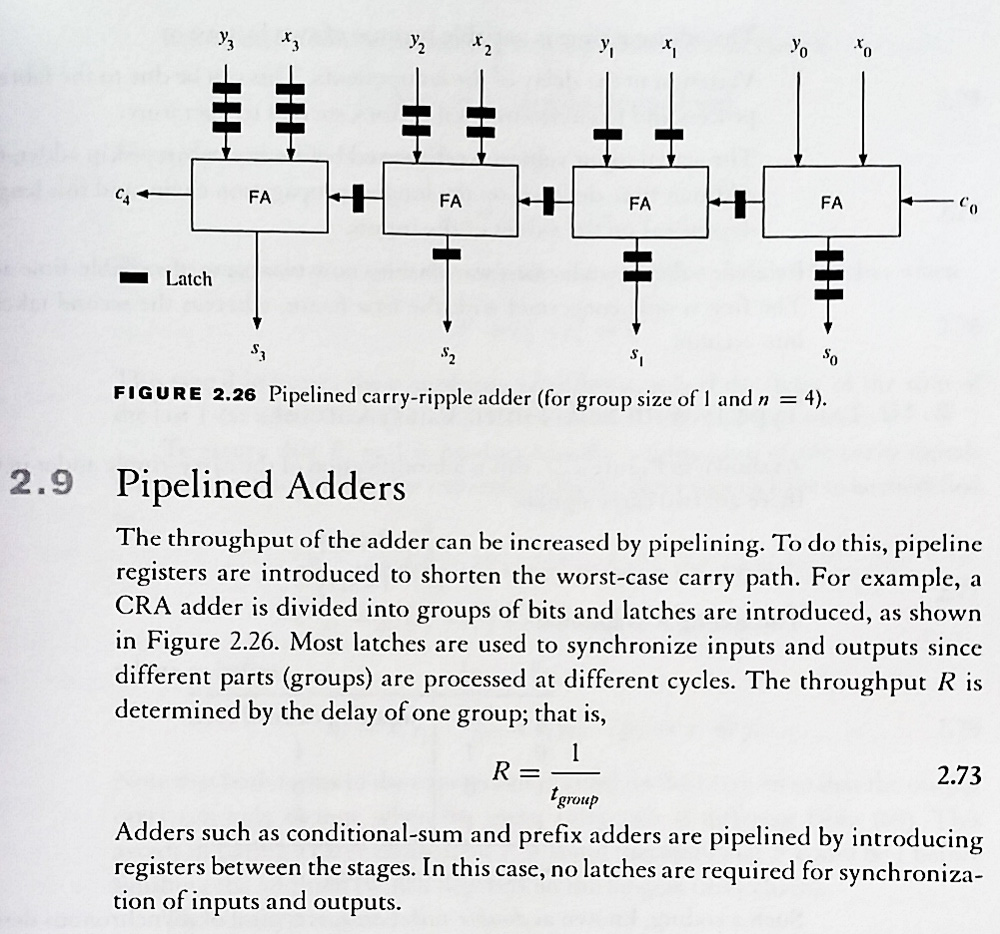

Antes del seminario MIPSfpga en MEPhI, uno de los instructores, Yegor Kuzmin, comenzó a preguntarme sobre las condiciones de carrera en un cierto esquema de computación especializada que surgió como un proyecto estudiantil. No estoy seguro de haberlo entendido correctamente, pero expresé que en un diseño síncrono bien organizado estos problemas no surgen y prometí enviar como ejemplo una fotografía de una página del libro "Aritmética digital", que comprende la organización del sumador de canalización, que contiene una pequeña cantidad de lógica combinatoria (lo mismo que en el sumador con acarreo secuencial), pero al mismo tiempo coloca los registros (D-flip-flops) de tal manera que el sumador puede iniciar una nueva operación de adición cada ciclo de reloj, con una frecuencia señal de reloj, determinada por el retraso de un sumador combinatorio completo de un solo bit:aritmética digital, 1.a edición, de Milos D. Ercegovac y Tomás Lang Al mismo tiempo, fotografié un par de páginas sobre circuitos asincrónicos de tiempo propio, también relacionados con el tema .

Antes del seminario MIPSfpga en MEPhI, uno de los instructores, Yegor Kuzmin, comenzó a preguntarme sobre las condiciones de carrera en un cierto esquema de computación especializada que surgió como un proyecto estudiantil. No estoy seguro de haberlo entendido correctamente, pero expresé que en un diseño síncrono bien organizado estos problemas no surgen y prometí enviar como ejemplo una fotografía de una página del libro "Aritmética digital", que comprende la organización del sumador de canalización, que contiene una pequeña cantidad de lógica combinatoria (lo mismo que en el sumador con acarreo secuencial), pero al mismo tiempo coloca los registros (D-flip-flops) de tal manera que el sumador puede iniciar una nueva operación de adición cada ciclo de reloj, con una frecuencia señal de reloj, determinada por el retraso de un sumador combinatorio completo de un solo bit:aritmética digital, 1.a edición, de Milos D. Ercegovac y Tomás Lang Al mismo tiempo, fotografié un par de páginas sobre circuitos asincrónicos de tiempo propio, también relacionados con el tema . Luego me presentaron a Vladimir Dementiev, quien, junto con Andrei Andrianov, Dmitry Kozlovsky, dirige clases de laboratorio en el MEPhI para programar microcontroladores Microchip PIC32MX. Le dije a Vladimir que el profesor Alex Dean de la Universidad de Carolina del Norte colaboró con Imagination, Microchip y Digilent y ahora está desarrollando un nuevo curso sobre programación de microcontroladores PIC32MZ de MicrochipEste curso incluye RTOS y la nueva conexión de microcontroladores a la nube. El microcontrolador PIC32MZ se basa en el núcleo del microprocesador MIPS microAptiv UP, el mismo que el utilizado en MIPSfpga. Por lo tanto, comencé a agitar a los camaradas MEPhI para que participaran en la revisión y (si les gusta) las pruebas beta de este curso: Pero volvamos a nuestro seminario. El tema del seminario fue MIPSfpga. Lo que es:

Luego me presentaron a Vladimir Dementiev, quien, junto con Andrei Andrianov, Dmitry Kozlovsky, dirige clases de laboratorio en el MEPhI para programar microcontroladores Microchip PIC32MX. Le dije a Vladimir que el profesor Alex Dean de la Universidad de Carolina del Norte colaboró con Imagination, Microchip y Digilent y ahora está desarrollando un nuevo curso sobre programación de microcontroladores PIC32MZ de MicrochipEste curso incluye RTOS y la nueva conexión de microcontroladores a la nube. El microcontrolador PIC32MZ se basa en el núcleo del microprocesador MIPS microAptiv UP, el mismo que el utilizado en MIPSfpga. Por lo tanto, comencé a agitar a los camaradas MEPhI para que participaran en la revisión y (si les gusta) las pruebas beta de este curso: Pero volvamos a nuestro seminario. El tema del seminario fue MIPSfpga. Lo que es:

MIPSfpga — MIPS microAptiv UP. Microchip PIC32MZ, « » — Samsung Artik 1.

MIPS microAptiv UP 25 , Verilog, , .

MIPS microAptiv UP — MIPSfpga — : (), () Field Programmable Gate Array (FPGA).

Entonces, primero hablé y hablé sobre:1. Imagination Technologies y su unidad de negocios MIPS2. Programas educativos de Imagination Technologies3. Actualizar el concepto de flujo de RTL a GDSII para aquellos en la audiencia que no tenían Verilog / VHDL a especialización: cómo se diseñan los bloques y sistemas IP en un chip (SoC).4. Hablé un poco sobre las tres líneas de núcleos de microprocesador MIPS y con más detalle sobre la línea de núcleos de clase de microcontrolador, en base a uno de los cuales (MIPS microAptiv UP) se creó el paquete MIPSfpga5. Como uno de los ejercicios incluía además demostrar la caché, dije un par palabras y sobre cachés en MIPS microAptiv UP

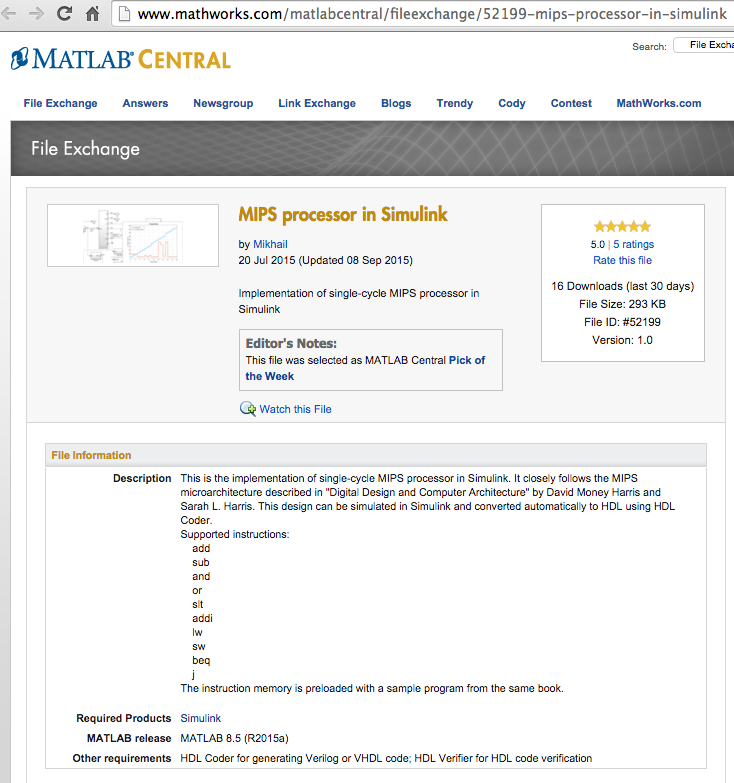

Después de mi primer discurso, Mikhail Peselnik, un orador de MathWorks, pronunció un discurso: Mikhail Peselnik implementó un subconjunto de MIPS en Simulink , que recibió una especie de premio editorial . al menos en Verilog y VHDL, al menos con la ayuda de modelos C, al menos con la ayuda de Simulink. Pero después de estudiar los conceptos básicos de arquitectura y microarquitectura, el estudiante debe experimentar con un procesador industrial, y aquí MIPSfpga entra en escena, con lo cual:

Después de mi primer discurso, Mikhail Peselnik, un orador de MathWorks, pronunció un discurso: Mikhail Peselnik implementó un subconjunto de MIPS en Simulink , que recibió una especie de premio editorial . al menos en Verilog y VHDL, al menos con la ayuda de modelos C, al menos con la ayuda de Simulink. Pero después de estudiar los conceptos básicos de arquitectura y microarquitectura, el estudiante debe experimentar con un procesador industrial, y aquí MIPSfpga entra en escena, con lo cual:

- Los estudiantes pueden construir sus propios prototipos de sistemas en un chip, combinando un núcleo de microprocesador, memoria y dispositivos de E / S diseñados por ellos.

- , . « ».

- , , .

Pero para experimentar con los desarrollos de SoC y con el núcleo, necesitan tener un buen dominio de la herramienta / herramienta de implementación. Por lo tanto, después de que Mikhail Mikhail Filippov, ingeniero de aplicaciones de Macro Group, un representante oficial de Xilinx en Rusia, habló. Xilinx es la compañía que una vez inventó los FPGA y hasta el día de hoy sigue siendo el número 1 en la mayoría de los FPGA de alta velocidad.Alexander Filippov hizo dos informes:- Nuevos FPGA de la serie 7 y MPSoC UltraScale: productos XILINX para potentes sistemas de chips programables

- Entorno de diseño XILINX VIVADO para crear sistemas en un chip

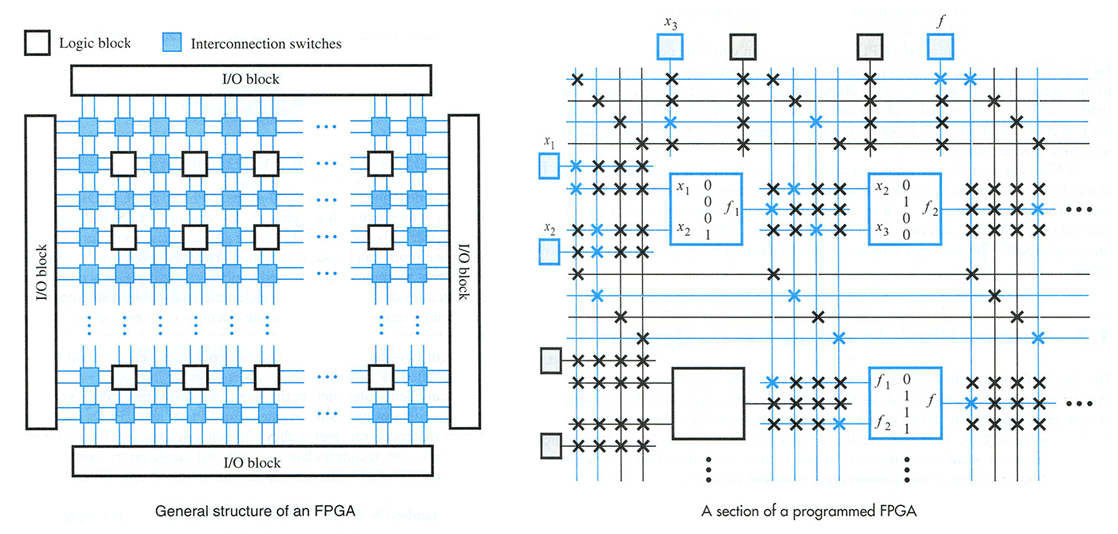

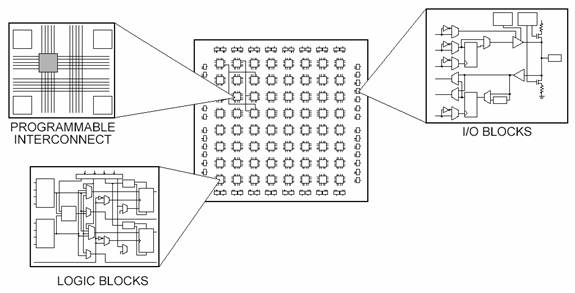

Lo que FPGA / FPGA expliqué en los dedos en otra publicación sobre Habr - Cómo comenzar a desarrollar hierro usando FPGAs - instrucciones paso a paso . Pero repitamos esta información nuevamente:en la versión más simple, el FPGA consiste en una matriz de células homogéneas, cada una de las cuales se puede cambiar para que funcione utilizando multiplexores conectados a los bits de la memoria de configuración. Una celda puede convertirse en una puerta AND con cuatro entradas y una salida, otra: un registro de un solo bit, etc. Cargamos una secuencia de bits de la memoria en la memoria de configuración, y el circuito electrónico dado se forma en el FPGA, que puede ser un procesador, controlador de pantalla, etc.Los FPGA / FPGA no son procesadores; al "programar" los FPGA (llenando la memoria de configuración de los FPGA) se crea un circuito electrónico (hardware), mientras que al programar un procesador (hardware fijo) se desliza una cadena de instrucciones de programa secuenciales escritas en él (software).A continuación se muestra un diagrama de la unidad FPGA más simple, que incluye una tabla de búsqueda (LUT) y un flip-flop. Es cierto que, en este esquema, no se muestran multiplexores que cambian la función de la celda y las conexiones a la memoria de configuración.

Lo que FPGA / FPGA expliqué en los dedos en otra publicación sobre Habr - Cómo comenzar a desarrollar hierro usando FPGAs - instrucciones paso a paso . Pero repitamos esta información nuevamente:en la versión más simple, el FPGA consiste en una matriz de células homogéneas, cada una de las cuales se puede cambiar para que funcione utilizando multiplexores conectados a los bits de la memoria de configuración. Una celda puede convertirse en una puerta AND con cuatro entradas y una salida, otra: un registro de un solo bit, etc. Cargamos una secuencia de bits de la memoria en la memoria de configuración, y el circuito electrónico dado se forma en el FPGA, que puede ser un procesador, controlador de pantalla, etc.Los FPGA / FPGA no son procesadores; al "programar" los FPGA (llenando la memoria de configuración de los FPGA) se crea un circuito electrónico (hardware), mientras que al programar un procesador (hardware fijo) se desliza una cadena de instrucciones de programa secuenciales escritas en él (software).A continuación se muestra un diagrama de la unidad FPGA más simple, que incluye una tabla de búsqueda (LUT) y un flip-flop. Es cierto que, en este esquema, no se muestran multiplexores que cambian la función de la celda y las conexiones a la memoria de configuración. Diagramas que ilustran la estructura de FPGA:

Diagramas que ilustran la estructura de FPGA: Y uno más:

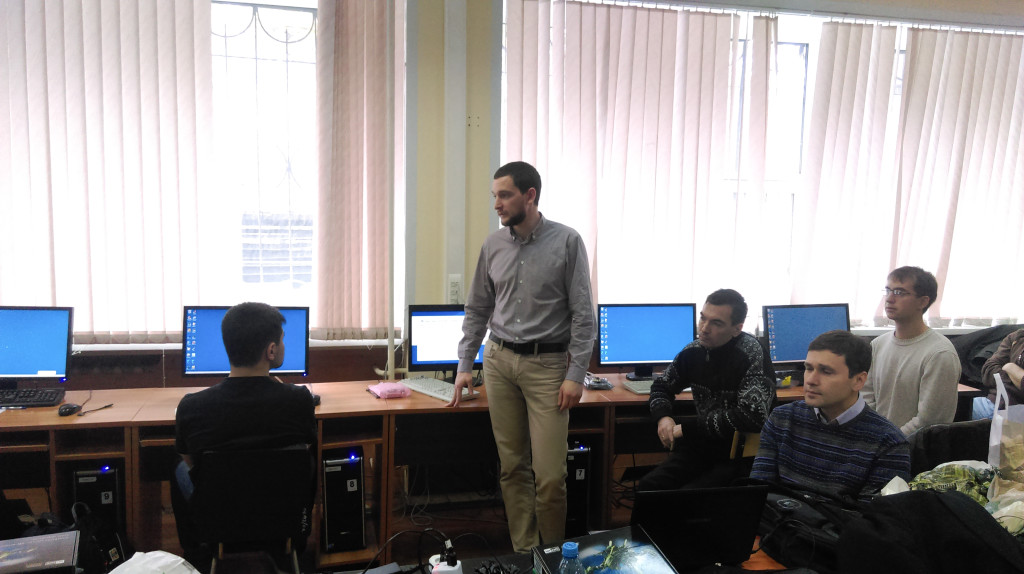

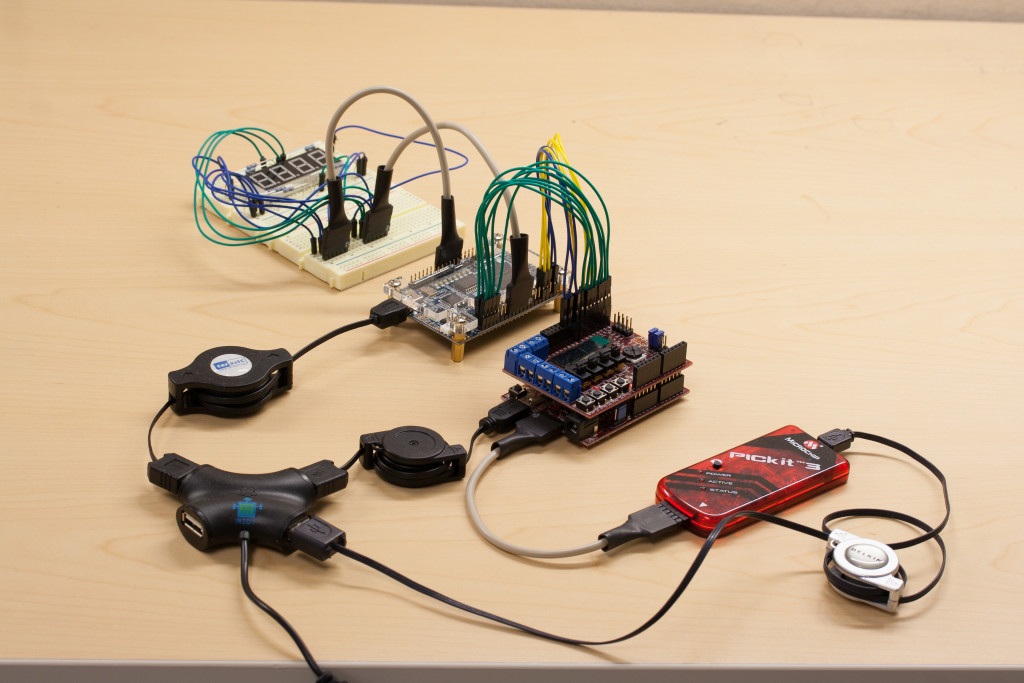

Y uno más: después del almuerzo en el comedor del Instituto de Física de Ingeniería de Moscú, comenzamos la parte práctica. Inicialmente, cuando Imagination Technologies y Xilinx celebraron dicho seminario en Los Ángeles, utilizarondiapositivas preparadas por los profesores David y Sarah Harris del sur de California . Como se veía originalmente, puedes ver en el video:Los 8 videos deltaller de Los Ángeles Para los seminarios en Rusia, las fijaciones del núcleo y del laboratorio de Harris tuvieron que modificarse sustancialmente. Las modificaciones se pueden encontrar en https://github.com/MIPSfpga/mipsfpga-plus . Las diferencias incluyen:1. Todo está ordenado para placas base baratas de Altera, disponibles en Rusia sin motor de exportación-importación2. Implementado la carga del programa en un sistema sintetizado sin usar BusBlaster, simplemente a través de UART3. Sensor de luz como periférico en lugar de una pantalla LCD4. Conmutable señal de reloj de frecuencia ultrabaja, que permite a los laboratorios visualizar el funcionamiento de cualquier procesador interno5. Se agregó un laboratorio simple para visualizar errores de caché+ cada pequeña cosa y cosméticos: un gestor de arranque / cargador de arranque más compacto, la posibilidad de transacciones estrechas no almacenables en caché a la memoria, etc.Más detalles:1. Traslado bajo Altera Enprimer lugar, las diapositivas de Harris mostraron todo para Xilinx, y recientemente, el envío de tableros de FPGA de Xilinx a Rusia se ha convertido en un procedimiento burocrático bastante complicado que lleva de 3 a 4 meses. Lo mismo sucedió con la licencia del software para síntesis y Xilinx Vivado, incluso con licencias gratuitas. Algunas universidades rusas no tenían juntas Xilinx ni licencias de Vivado; otros solo tenían la licencia anterior para el predecesor de Vivado: el software ISE 2013, que no admitía FPGA en placas que transporté en Rusia.En resumen, para los seminarios en Rusia, los camaradas y yo, en California, habíamos trasladado MIPSfpga a un par de tableros baratos disponibles en Rusia del rival de Xilinx, Altera (esta compañía ahora se está fusionando con Intel). Los tableros Alter fueron donados para las necesidades del taller por la compañía Zelenograd SPC Elvis . La placa principal de MEPhI, MIPT y SSAU fue el Terasic DE0-CV basado en Altera Cyclone V: otra placa fue el Terasic DE0-Nano, un chal muy compacto adecuado para proyectos como robots voladores, pero con una pequeña cantidad de periféricos a bordo: Terasic DE0- desventaja Nano es un pequeño número de dispositivos periféricos en la placa en sí, pero también es una ventaja, ya que DE0-Nano se puede conectar como diseñador con otras placas e integrarse en diferentes dispositivos:

después del almuerzo en el comedor del Instituto de Física de Ingeniería de Moscú, comenzamos la parte práctica. Inicialmente, cuando Imagination Technologies y Xilinx celebraron dicho seminario en Los Ángeles, utilizarondiapositivas preparadas por los profesores David y Sarah Harris del sur de California . Como se veía originalmente, puedes ver en el video:Los 8 videos deltaller de Los Ángeles Para los seminarios en Rusia, las fijaciones del núcleo y del laboratorio de Harris tuvieron que modificarse sustancialmente. Las modificaciones se pueden encontrar en https://github.com/MIPSfpga/mipsfpga-plus . Las diferencias incluyen:1. Todo está ordenado para placas base baratas de Altera, disponibles en Rusia sin motor de exportación-importación2. Implementado la carga del programa en un sistema sintetizado sin usar BusBlaster, simplemente a través de UART3. Sensor de luz como periférico en lugar de una pantalla LCD4. Conmutable señal de reloj de frecuencia ultrabaja, que permite a los laboratorios visualizar el funcionamiento de cualquier procesador interno5. Se agregó un laboratorio simple para visualizar errores de caché+ cada pequeña cosa y cosméticos: un gestor de arranque / cargador de arranque más compacto, la posibilidad de transacciones estrechas no almacenables en caché a la memoria, etc.Más detalles:1. Traslado bajo Altera Enprimer lugar, las diapositivas de Harris mostraron todo para Xilinx, y recientemente, el envío de tableros de FPGA de Xilinx a Rusia se ha convertido en un procedimiento burocrático bastante complicado que lleva de 3 a 4 meses. Lo mismo sucedió con la licencia del software para síntesis y Xilinx Vivado, incluso con licencias gratuitas. Algunas universidades rusas no tenían juntas Xilinx ni licencias de Vivado; otros solo tenían la licencia anterior para el predecesor de Vivado: el software ISE 2013, que no admitía FPGA en placas que transporté en Rusia.En resumen, para los seminarios en Rusia, los camaradas y yo, en California, habíamos trasladado MIPSfpga a un par de tableros baratos disponibles en Rusia del rival de Xilinx, Altera (esta compañía ahora se está fusionando con Intel). Los tableros Alter fueron donados para las necesidades del taller por la compañía Zelenograd SPC Elvis . La placa principal de MEPhI, MIPT y SSAU fue el Terasic DE0-CV basado en Altera Cyclone V: otra placa fue el Terasic DE0-Nano, un chal muy compacto adecuado para proyectos como robots voladores, pero con una pequeña cantidad de periféricos a bordo: Terasic DE0- desventaja Nano es un pequeño número de dispositivos periféricos en la placa en sí, pero también es una ventaja, ya que DE0-Nano se puede conectar como diseñador con otras placas e integrarse en diferentes dispositivos:

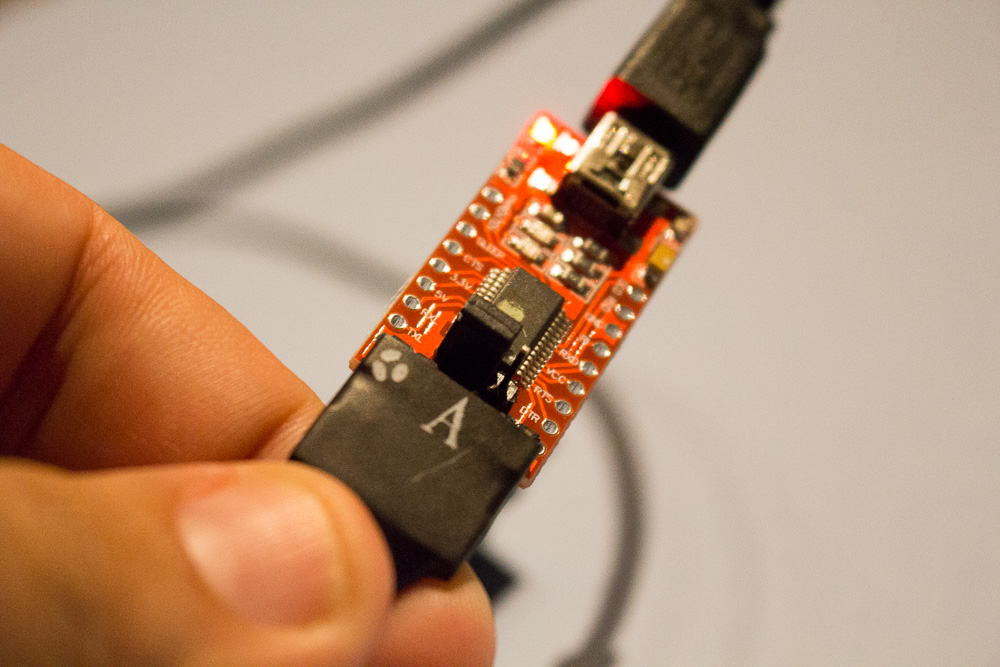

2. Descargar a través de UART Elsegundo problema de diapositivas de Harris fue utilizar el adaptador de depuración de Bus Blaster y el software llamado OpenOCD . Básicamente, BusBlaster / OpenOCD es una muy buena solución de este tipo. Permite no solo cargar programas en el sistema sintetizado dentro del FPGA, sino también depurarlos de forma remota a través de la interfaz EJTAG, un complemento de un nivel superior a través de la interfaz JTAG. Al mismo tiempo, BusBlaster cuesta solo $ 43, que es mucho más barato que los adaptadores EJTAG de depuración industrial.Desafortunadamente, la combinación BusBlaster / OpenOCD es bastante cruda, y temía que no funcionara en alguna configuración de computadora inesperada en Rusia (tenía razón, no funcionó en MIPT y SSAU). Además,En un sitio que vende una combinación BusBlaster / OpenOCD para MIPS , a veces las placas se agotan.Por esta y otras razones, comencé a buscar otras formas de cargar software en el sistema (en el FPGA, debe cargar por separado la configuración / hardware y software para el procesador (en un sistema sintetizado con un procesador)). El troll anónimo de Internet Alexey intentó debilitarme durante mucho tiempo, para poder implementar el gestor de arranque EJTAG a través del Altera USB Blaster, pero como no era un experto en EJTAG, elegí una solución simple que funcionó desde la era soviética: cargar el programa a través del puerto serie / UART. Es cierto que durante la era soviética había un puerto RS-232C, y en la década de 1990 aparecieron chips de FTDI, lo que hizo posible hacer todo a través de un cable USB conectado a una PC. Se pueden comprar diferentes variaciones de dicho adaptador por $ 5 en Moscú y por menos de $ 2 a través de Internet desde China:

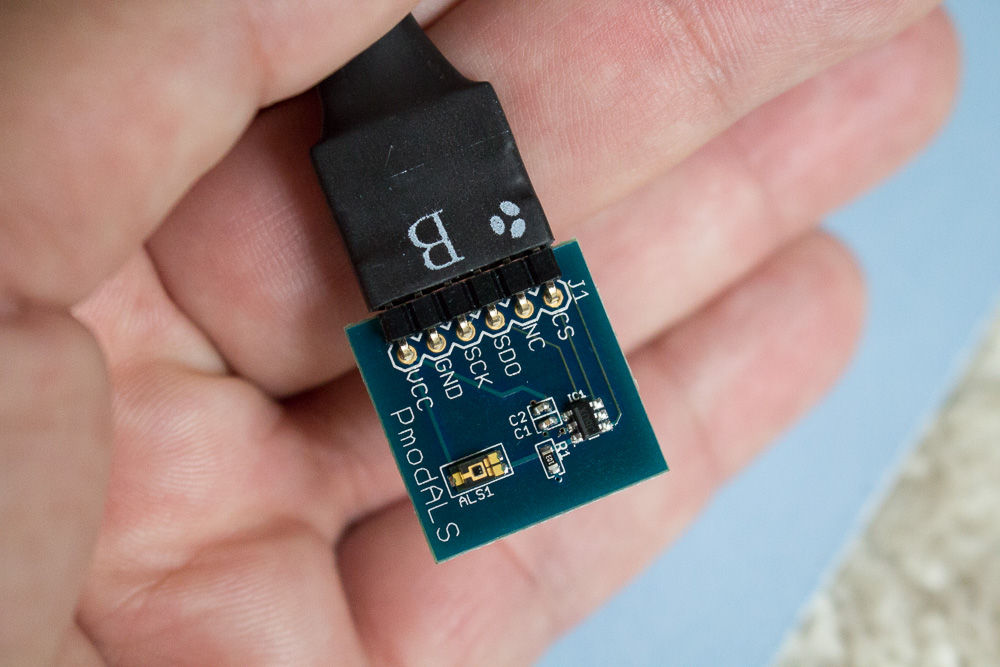

2. Descargar a través de UART Elsegundo problema de diapositivas de Harris fue utilizar el adaptador de depuración de Bus Blaster y el software llamado OpenOCD . Básicamente, BusBlaster / OpenOCD es una muy buena solución de este tipo. Permite no solo cargar programas en el sistema sintetizado dentro del FPGA, sino también depurarlos de forma remota a través de la interfaz EJTAG, un complemento de un nivel superior a través de la interfaz JTAG. Al mismo tiempo, BusBlaster cuesta solo $ 43, que es mucho más barato que los adaptadores EJTAG de depuración industrial.Desafortunadamente, la combinación BusBlaster / OpenOCD es bastante cruda, y temía que no funcionara en alguna configuración de computadora inesperada en Rusia (tenía razón, no funcionó en MIPT y SSAU). Además,En un sitio que vende una combinación BusBlaster / OpenOCD para MIPS , a veces las placas se agotan.Por esta y otras razones, comencé a buscar otras formas de cargar software en el sistema (en el FPGA, debe cargar por separado la configuración / hardware y software para el procesador (en un sistema sintetizado con un procesador)). El troll anónimo de Internet Alexey intentó debilitarme durante mucho tiempo, para poder implementar el gestor de arranque EJTAG a través del Altera USB Blaster, pero como no era un experto en EJTAG, elegí una solución simple que funcionó desde la era soviética: cargar el programa a través del puerto serie / UART. Es cierto que durante la era soviética había un puerto RS-232C, y en la década de 1990 aparecieron chips de FTDI, lo que hizo posible hacer todo a través de un cable USB conectado a una PC. Se pueden comprar diferentes variaciones de dicho adaptador por $ 5 en Moscú y por menos de $ 2 a través de Internet desde China: Notaré de inmediato que puede cargar programas en SoC sintetizado de diferentes maneras. En uno de ellos, más tradicional, el sistema tiene un pequeño programa fijo en la memoria (cargador de arranque), que se inicia después de reiniciar el sistema y carga un programa más grande a través del puerto serie / UART. Anton Pavlov de NIIIS utilizó este método, quien lo demostró en seminarios en la Universidad Estatal de Moscú y el Instituto de Física de Ingeniería de Moscú, y también escribió sobre él en geektimes "MIPSfpga: fuera del canon" .Hice la carga de una manera alternativa, en la que la memoria se llena con una máquina de estado, totalmente implementada en el hardware. La máquina acepta un archivo de texto en formato Motorola S-Record desde una PC a través de UART, lo analiza (todo en el hardware) y llena la memoria con datos, mientras el procesador está en un estado de reinicio. Luego, el procesador se activa y comienza a leer el programa desde la memoria del sistema. Todo lo que hay que hacer en el lado de la PC es convertir el archivo ELF ejecutable al formato S-Record de Motorola y enviarlo al puerto COM virtual con el comando "type" windows-shell.3. Sensor de luz como periférico en lugar de una pantalla LCDEn los laboratorios originales de Harris, utilizaron un indicador de siete segmentos y una pantalla LCD SPI como ejemplos de periféricos. Un ejemplo con un indicador de siete segmentos es aburrido: cualquier estudiante comprende que si sabe parpadear con una luz, entonces sabe cómo parpadear con siete luces. El ejemplo de SPI es un poco mejor, especialmente cuando se trata de estudiantes novatos, pero ¿por qué necesitamos una segunda pantalla si ya hay un indicador de siete segmentos? En resumen, antes de ir a Rusia, compré 20 sensores de luz, también con una interfaz SPI, y los usé en lugar de pantallas: al mismo tiempo, la interfaz es muy simple: aquí está el módulo de interfaz que escribí (nota: este código no incluye todas las modificaciones del sistema para emparejarlo con Bus AHB-Lite, para que el software vea el valor):

Notaré de inmediato que puede cargar programas en SoC sintetizado de diferentes maneras. En uno de ellos, más tradicional, el sistema tiene un pequeño programa fijo en la memoria (cargador de arranque), que se inicia después de reiniciar el sistema y carga un programa más grande a través del puerto serie / UART. Anton Pavlov de NIIIS utilizó este método, quien lo demostró en seminarios en la Universidad Estatal de Moscú y el Instituto de Física de Ingeniería de Moscú, y también escribió sobre él en geektimes "MIPSfpga: fuera del canon" .Hice la carga de una manera alternativa, en la que la memoria se llena con una máquina de estado, totalmente implementada en el hardware. La máquina acepta un archivo de texto en formato Motorola S-Record desde una PC a través de UART, lo analiza (todo en el hardware) y llena la memoria con datos, mientras el procesador está en un estado de reinicio. Luego, el procesador se activa y comienza a leer el programa desde la memoria del sistema. Todo lo que hay que hacer en el lado de la PC es convertir el archivo ELF ejecutable al formato S-Record de Motorola y enviarlo al puerto COM virtual con el comando "type" windows-shell.3. Sensor de luz como periférico en lugar de una pantalla LCDEn los laboratorios originales de Harris, utilizaron un indicador de siete segmentos y una pantalla LCD SPI como ejemplos de periféricos. Un ejemplo con un indicador de siete segmentos es aburrido: cualquier estudiante comprende que si sabe parpadear con una luz, entonces sabe cómo parpadear con siete luces. El ejemplo de SPI es un poco mejor, especialmente cuando se trata de estudiantes novatos, pero ¿por qué necesitamos una segunda pantalla si ya hay un indicador de siete segmentos? En resumen, antes de ir a Rusia, compré 20 sensores de luz, también con una interfaz SPI, y los usé en lugar de pantallas: al mismo tiempo, la interfaz es muy simple: aquí está el módulo de interfaz que escribí (nota: este código no incluye todas las modificaciones del sistema para emparejarlo con Bus AHB-Lite, para que el software vea el valor):

4.Reloj cambiado a frecuencia ultrabaja Cuando apareció MIPSfpga y los profesores universitarios rusos comenzaron a estudiarlo, algunos de ellos comenzaron a quejarse de que el paquete en su forma original no es muy interesante para estudiantes avanzados, ya que los laboratorios preparados por David y Sarah Harris usan un procesador como una "caja negra", simplemente conectando dispositivos a ella. En otras palabras, Harris ignoró por completo que el procesador se proporciona en el código fuente y, por lo tanto, es posible implementar laboratorios que permitan la salida de conexiones desde registros de procesador arbitrarios (no solo registros visibles para el programador, sino generalmente desde cualquier disparador D) para conectarse por ejemplo, a los LED, y observe lo que le sucede al procesador cuando ejecuta ciertos programas.Como comprenderá, para hacer tales observaciones "en vivo", es necesario hacer que el procesador funcione a una frecuencia de reloj muy baja, por ejemplo, un reloj por segundo. ¿Cómo hacerlo? El núcleo MIPS microAptiv UP implementado en ASIC en tecnología de 28 nm puede operar a frecuencias superiores a 500 MHz y en tecnología de 65 nm a más de 300 MHz. Cuando se implementa en FPGA, las frecuencias son mucho más bajas, pero aún altas: 50-60 MHz. Las frecuencias de los generadores de señal de reloj en los tableros son de 50-100 MHz, con la posibilidad de aumentar o disminuir la frecuencia utilizando un bucle de bloqueo de fase (PLL) / bucle de bloqueo de fase (PLL) .Desafortunadamente, usando PLL, puede reducir la frecuencia a ~ 100 KHz, pero necesita reducir la frecuencia a 1 Hz de otra manera. Al principio intenté hacer esto usando un bloque de Altera llamadoALTCLKCTRL , pero por alguna razón no funcionó. Luego intenté dividir la señal del reloj usando un contador, pero (ya lo sabía) esta solución por sí sola no funciona, porque el sintetizador no entiende que la señal de salida es una señal de reloj y comienza a dividirla incorrectamente, como resultado de lo cual el procesador no funciona. Consulté con varios camaradas y comenzamos a usar la macro Alter "global" (y su equivalente en Xilinx BUFG). 5. Se agregó un simple laboratorio de visualización de errores de caché

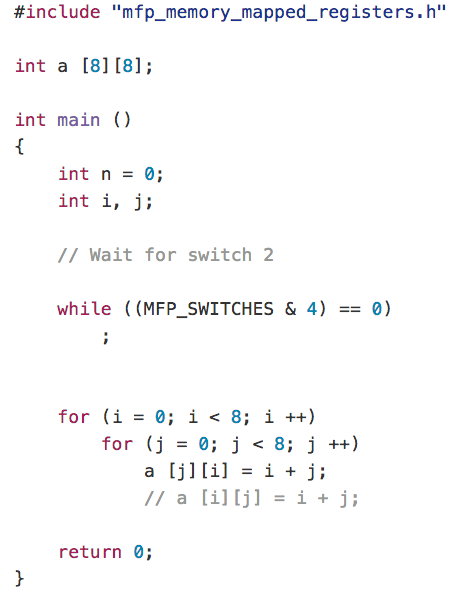

4.Reloj cambiado a frecuencia ultrabaja Cuando apareció MIPSfpga y los profesores universitarios rusos comenzaron a estudiarlo, algunos de ellos comenzaron a quejarse de que el paquete en su forma original no es muy interesante para estudiantes avanzados, ya que los laboratorios preparados por David y Sarah Harris usan un procesador como una "caja negra", simplemente conectando dispositivos a ella. En otras palabras, Harris ignoró por completo que el procesador se proporciona en el código fuente y, por lo tanto, es posible implementar laboratorios que permitan la salida de conexiones desde registros de procesador arbitrarios (no solo registros visibles para el programador, sino generalmente desde cualquier disparador D) para conectarse por ejemplo, a los LED, y observe lo que le sucede al procesador cuando ejecuta ciertos programas.Como comprenderá, para hacer tales observaciones "en vivo", es necesario hacer que el procesador funcione a una frecuencia de reloj muy baja, por ejemplo, un reloj por segundo. ¿Cómo hacerlo? El núcleo MIPS microAptiv UP implementado en ASIC en tecnología de 28 nm puede operar a frecuencias superiores a 500 MHz y en tecnología de 65 nm a más de 300 MHz. Cuando se implementa en FPGA, las frecuencias son mucho más bajas, pero aún altas: 50-60 MHz. Las frecuencias de los generadores de señal de reloj en los tableros son de 50-100 MHz, con la posibilidad de aumentar o disminuir la frecuencia utilizando un bucle de bloqueo de fase (PLL) / bucle de bloqueo de fase (PLL) .Desafortunadamente, usando PLL, puede reducir la frecuencia a ~ 100 KHz, pero necesita reducir la frecuencia a 1 Hz de otra manera. Al principio intenté hacer esto usando un bloque de Altera llamadoALTCLKCTRL , pero por alguna razón no funcionó. Luego intenté dividir la señal del reloj usando un contador, pero (ya lo sabía) esta solución por sí sola no funciona, porque el sintetizador no entiende que la señal de salida es una señal de reloj y comienza a dividirla incorrectamente, como resultado de lo cual el procesador no funciona. Consulté con varios camaradas y comenzamos a usar la macro Alter "global" (y su equivalente en Xilinx BUFG). 5. Se agregó un simple laboratorio de visualización de errores de caché Ahora puede realizar entretenidos experimentos, por ejemplo, para hacer que el LED parpadee durante una falla de caché, y luego observar en tiempo real que la caché golpea y falla al llenar una matriz bidimensional. Si llena la matriz línea por línea, los parpadeos serán diferentes a los de las columnas: debe tenerse en cuenta que no todo salió bien:

Ahora puede realizar entretenidos experimentos, por ejemplo, para hacer que el LED parpadee durante una falla de caché, y luego observar en tiempo real que la caché golpea y falla al llenar una matriz bidimensional. Si llena la matriz línea por línea, los parpadeos serán diferentes a los de las columnas: debe tenerse en cuenta que no todo salió bien: 1. El GPIO en DE0-Nano es diferente del GPIO en los tableros DE0-CV y Xilinx. En particular, por alguna razón no pude declarar todo el puerto GPIO como uno de entrada y luego usar sus bits individuales como entrada o como salida. Aunque en DE0-CV esto va bien. No tuve tiempo de dividir las diferentes salidas GPIO entre diferentes señales lógicas (en Verilog), así que simplemente no clasifiqué el laboratorio con el sensor de luz en DE0-Nano. Por la misma razón, no exporté la interfaz con Bus Blaster al DE0-CV.2. Peor aún, la descarga a través de UART para DE0-Nano no funcionó en MEPhI, aunque antes funcionó en la Universidad Estatal de Moscú y en mi computadora portátil. La razón aún no está 100% clara:2.1. Tal vez hubo un problema de incompatibilidad de la versión de Windows (7 con el parche) y el cable USB a UART utilizado para DE0-Nano. El cable era un clon de cable chino barato basado en el chipset PL2303TA, aunque no lo probé antes del seminario. Se sabe que la versión anterior de tales cables basados en chipsets con PL2303HX tenía un problema de compatibilidad con Windows 8 ( ver ). Lo más atroz que tuve conmigo fue una computadora portátil con una versión de Windows 7, y una computadora portátil con una versión de Windows 8, y varias alternativas a este cable. Pero no verifiqué todas las combinaciones antes del seminario, aunque podría haberlo hecho la noche anterior, por desgracia.2.2. Dos días antes del taller, hice cambios en el divisor del reloj. No valía la pena hacerlo tampoco.2.3. Bueno, al menos todo funcionó bien en el DE0-CV.3. En MEPhI, mostré una versión más compleja del ejemplo de caché que antes en la Universidad Estatal de Moscú. Fue un error: en un ejemplo complejo, el compilador optimizó algo, y el patrón de las luces no era tan obvio como en el ejemplo simple original. El orador adicional invitado de NIIMI Anton Pavlov, quien, aunque no tuvo tiempo en MEPhI, mostró a algunos presentes su propia versión del enlace MIPSfpga llamada myMIPSfpga, que también describió en la nota "MIPSfpga: fuera del canon" . Entre otras cosas, Anton ha portado MIPSfpga a la placa rusa Mars rover 3

1. El GPIO en DE0-Nano es diferente del GPIO en los tableros DE0-CV y Xilinx. En particular, por alguna razón no pude declarar todo el puerto GPIO como uno de entrada y luego usar sus bits individuales como entrada o como salida. Aunque en DE0-CV esto va bien. No tuve tiempo de dividir las diferentes salidas GPIO entre diferentes señales lógicas (en Verilog), así que simplemente no clasifiqué el laboratorio con el sensor de luz en DE0-Nano. Por la misma razón, no exporté la interfaz con Bus Blaster al DE0-CV.2. Peor aún, la descarga a través de UART para DE0-Nano no funcionó en MEPhI, aunque antes funcionó en la Universidad Estatal de Moscú y en mi computadora portátil. La razón aún no está 100% clara:2.1. Tal vez hubo un problema de incompatibilidad de la versión de Windows (7 con el parche) y el cable USB a UART utilizado para DE0-Nano. El cable era un clon de cable chino barato basado en el chipset PL2303TA, aunque no lo probé antes del seminario. Se sabe que la versión anterior de tales cables basados en chipsets con PL2303HX tenía un problema de compatibilidad con Windows 8 ( ver ). Lo más atroz que tuve conmigo fue una computadora portátil con una versión de Windows 7, y una computadora portátil con una versión de Windows 8, y varias alternativas a este cable. Pero no verifiqué todas las combinaciones antes del seminario, aunque podría haberlo hecho la noche anterior, por desgracia.2.2. Dos días antes del taller, hice cambios en el divisor del reloj. No valía la pena hacerlo tampoco.2.3. Bueno, al menos todo funcionó bien en el DE0-CV.3. En MEPhI, mostré una versión más compleja del ejemplo de caché que antes en la Universidad Estatal de Moscú. Fue un error: en un ejemplo complejo, el compilador optimizó algo, y el patrón de las luces no era tan obvio como en el ejemplo simple original. El orador adicional invitado de NIIMI Anton Pavlov, quien, aunque no tuvo tiempo en MEPhI, mostró a algunos presentes su propia versión del enlace MIPSfpga llamada myMIPSfpga, que también describió en la nota "MIPSfpga: fuera del canon" . Entre otras cosas, Anton ha portado MIPSfpga a la placa rusa Mars rover 3 que yo, como hombre torturado por exportación-importación (Scylla: control de exportación estadounidense + Caribdis: aduanas rusas), voy a tratar de usarlo para los siguientes eventos educativos en Rusia: durante el descanso y después del seminario, Maxim Gorbunov me mostró varias vistas míticas, que incluyen Tres paneles en el espíritu de la era de la Galaxia de Andrómeda y el Café Molecular de múltiples volúmenes en rojo y blanco proviene de 1960: UPD: Como en los comentarios comencé a discutir la iglesia mifishnuyu, y lo haré al respecto (no estoy insertado l Este fragmento era originalmente, ya que no estaba seguro de que sea apropiado para geektimes):

que yo, como hombre torturado por exportación-importación (Scylla: control de exportación estadounidense + Caribdis: aduanas rusas), voy a tratar de usarlo para los siguientes eventos educativos en Rusia: durante el descanso y después del seminario, Maxim Gorbunov me mostró varias vistas míticas, que incluyen Tres paneles en el espíritu de la era de la Galaxia de Andrómeda y el Café Molecular de múltiples volúmenes en rojo y blanco proviene de 1960: UPD: Como en los comentarios comencé a discutir la iglesia mifishnuyu, y lo haré al respecto (no estoy insertado l Este fragmento era originalmente, ya que no estaba seguro de que sea apropiado para geektimes):

Fui a la iglesia mítica, alrededor de la cual hubo tantos gritos en Internet hace unos tres años, debido a que los empleados incluso salieron del Instituto de Física de Ingeniería de Moscú en protesta. Como una persona neutral, es decir un verdadero incrédulo, y no un partidario militante de uno u otro lado del conflicto, debo decir que 1) la iglesia mítica es bastante modesta y no vulgar, similar en espíritu a la Catedral Ortodoxa en San Francisco; 2) MEPhI no es la primera universidad rusa con una religión, el curso de ortodoxia apareció en el Instituto de Física y Tecnología de Moscú ya en 1988 (luego toda la universidad de física y tecnología acudió a él, los estudiantes escucharon la primera conferencia de pie, pero después de tres meses no había más de una docena de estudiantes); 3) hay iglesias en muchas universidades americanas. Continuará.

Fui a la iglesia mítica, alrededor de la cual hubo tantos gritos en Internet hace unos tres años, debido a que los empleados incluso salieron del Instituto de Física de Ingeniería de Moscú en protesta. Como una persona neutral, es decir un verdadero incrédulo, y no un partidario militante de uno u otro lado del conflicto, debo decir que 1) la iglesia mítica es bastante modesta y no vulgar, similar en espíritu a la Catedral Ortodoxa en San Francisco; 2) MEPhI no es la primera universidad rusa con una religión, el curso de ortodoxia apareció en el Instituto de Física y Tecnología de Moscú ya en 1988 (luego toda la universidad de física y tecnología acudió a él, los estudiantes escucharon la primera conferencia de pie, pero después de tres meses no había más de una docena de estudiantes); 3) hay iglesias en muchas universidades americanas. Continuará.

Source: https://habr.com/ru/post/es387157/

All Articles