Creación de prototipos ASIC en FPGA

El desarrollo de chips es complejo, costoso y lento. Y el precio de cualquier error es extremadamente alto. Después de hacer el cristal con parches y actualizaciones, nada se puede arreglar. Por lo tanto, la verificación de los esquemas diseñados en la etapa de desarrollo es especialmente meticulosa. Para cada bloque funcional, las pruebas de bloque se escriben en todos los modos operativos y no operativos. Después de integrar el bloque en el circuito general, se realizan pruebas del sistema sobre cómo funciona este bloque como parte del sistema. Todas las pruebas están girando constantemente en las pruebas de regresión. Incluso hay una señal informal de un nivel de prueba menos o menos aceptable, cuando la cantidad de código de prueba es 10 veces la cantidad de código de la unidad que se está probando. Pero todas estas pruebas no dan la sensación de que el circuito es viable, ya que cualquier simulación es el comportamiento del circuito durante un máximo de cientos de milisegundos.Pero en la vida, el circuito debería funcionar cientos de miles de horas. Una vez busqué una falla cuando se perdieron 1 o 2 bytes por 1 GB de información transmitida y ninguna prueba funcional encontró este problema. Y este error se manifestó solo en el prototipo FPGA del futuro chip. Acerca de qué prototipos hicimos y qué está pasando en el mundo, este artículo lo dirá.La creación de prototipos de chips futuros en un FPGA es la única forma de probar cómo funciona el circuito en tareas del mundo real en menos tiempo real. El prototipo le permite depurar software, obtener características de rendimiento iniciales y mucho más. Los FPGA modernos tienen una cantidad suficientemente grande de recursos para estas tareas. Por ejemplo, usted mismo puede implementar una computadora completa con un procesador Intel 8086 en una placa base con FPGA por $ 300 .Año 2004

Desafortunadamente, no pudimos encontrar el primer prototipo en los depósitos de nuestro gabinete con esqueletos, pero era una pequeña bufanda basada en el Xilinx Spartan3-400 (XC3S400). 400 significa el número de miles de válvulas equivalentes que están disponibles para el desarrollador para crear su circuito. El precio del pañuelo fue de aproximadamente $ 50 y permitió implementar en él un simple microcontrolador de 8 bits con toda la memoria y a una frecuencia de 40 MHz. La creación de prototipos consistió en el hecho de que el microcontrolador desarrollado parpadeaba en un LED.Año 2005

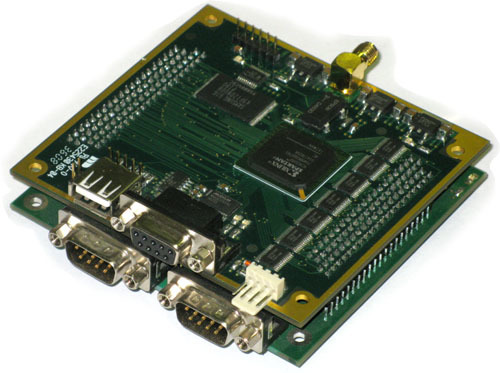

La placa especial para el prototipo ya se desarrolló no como un experimento, sino como una etapa significativa del proyecto. Ya aplicado FPGA Xilinx Spartan3-1000. Aquellos. Ya teníamos disponible 1 millón de válvulas, y el microcontrolador diseñado funcionaba a su frecuencia máxima de 48 MHz. Y fue en esta placa donde capturé los 2 bytes perdidos por gigabyte. El precio del tablero fue de aproximadamente $ 200.

Año 2007

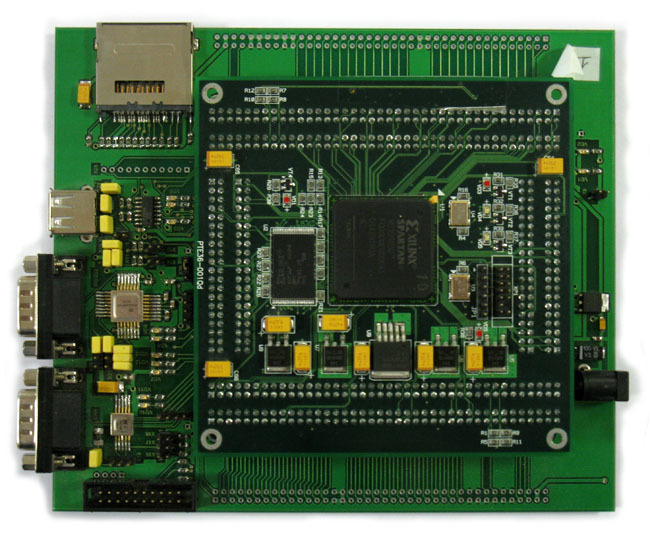

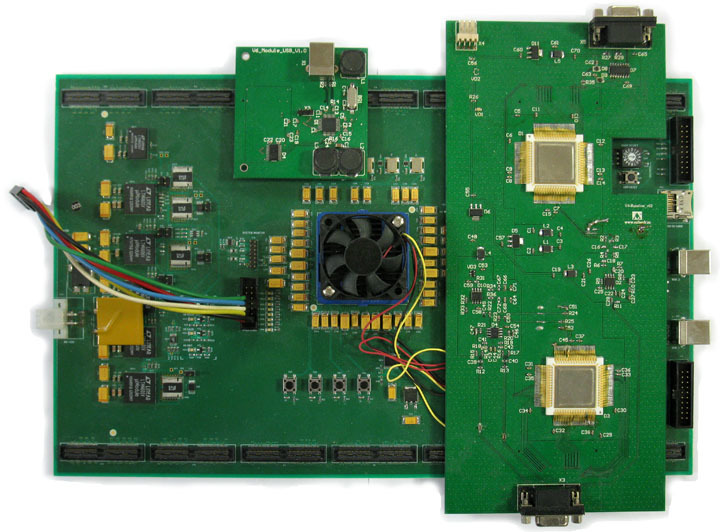

Para el nuevo microcontrolador de 32 bits, era obvio que 1 millón de válvulas podrían no ser suficientes. Por lo tanto, se desarrolló una nueva placa base basada en Xilinx Spartan3-5000, gracias a la cual estuvieron disponibles 5 millones de puertas. El precio del tablero fue de aproximadamente $ 500 y durante mucho tiempo este tablero se convirtió en el principal para la creación de prototipos de nuevos desarrollos. Sobre esta base, no solo se probaron los microcontroladores, sino también varios microcircuitos especializados. El microcontrolador que se está diseñando en FPGA ya funcionaba a una frecuencia reducida de 20 MHz, aunque en silicio funcionaba a frecuencias de 100 MHz e incluso 150 MHz.El prototipo del microcontrolador de 32 bits: el prototipo de la tarjeta de video (desafortunadamente el proyecto no se puso en marcha, pero el RTL terminado está esperando en las alas):

el prototipo de la tarjeta de video (desafortunadamente el proyecto no se puso en marcha, pero el RTL terminado está esperando en las alas): El prototipo del conmutador Ethernet de 4 vías con transceptores integrados:

El prototipo del conmutador Ethernet de 4 vías con transceptores integrados:

Año 2010

Al desarrollar un microcontrolador de doble núcleo (núcleo RISC de 32 bits + DSP de 16 bits), finalmente alcanzamos el nivel cuando 5 millones ya no eran suficientes. Pero la implementación en FPGA de varias configuraciones truncadas del futuro microcircuito permitió probar su funcionamiento. Por ejemplo, vendieron dos núcleos (RISC + DSP) con un conjunto truncado de periféricos o un núcleo (RISC), pero toda la periferia.año 2012

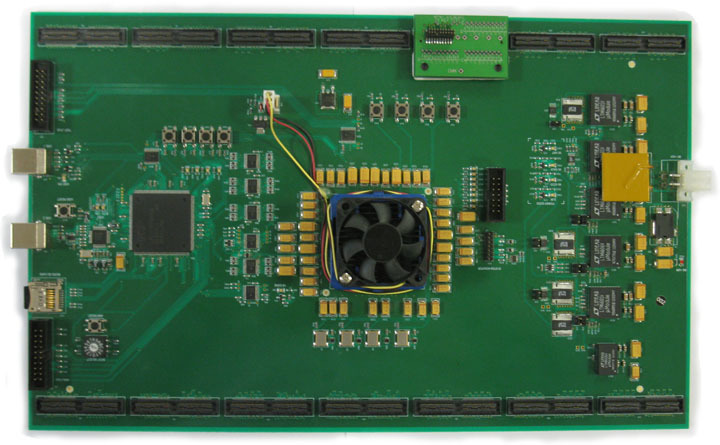

El nuevo proyecto requería una nueva placa, ya que la cantidad requerida de memoria interna para el nuevo núcleo DSP de 32 bits ya excedía la capacidad disponible en el FPGA Spartan más grande. Tuve que cambiar a FPGA más costosos y complejos. El tiempo del proyecto fue limitado y decidió encontrar una solución preparada. La elección recayó en el tablero de INREVIUM con el FPGA Xilinx Virtex-6 XC6VLX760 más grande en ese momento. Y aunque el número de puertas equivalentes ha aumentado a solo 8 millones, la cantidad de memoria de bloque incorporada ha aumentado de 2 Mbit a 25 Mbit.La elección también probablemente determinó que el costo de la tarifa se conservara en el sitio de la oficina de representación alemana en el caché de Google, y sabíamos que costaría $ 18K antes de firmar cualquier NDA. Y con el costo de solo un chip FPGA de $ 15 mil, esto eliminó cualquier pregunta sobre el desarrollo de su propia placa. Las tarjetas serie para FPGA tan grandes generalmente cuestan tanto como las FPGA mismas o son un poco más caras.La adquisición de la placa también trajo muchos conocimientos interesantes, por ejemplo, nuestro distribuidor local estaba convencido de que esta placa cuesta $ 40K, incluido el envío, y en general se arriesga mucho con el 100% de prepago de nuestra parte. Finalmente, 3 de estas placas se compraron sin intermediarios, y ahora se utilizan para crear prototipos de nuestros procesadores DSP.

Y aunque el número de puertas equivalentes ha aumentado a solo 8 millones, la cantidad de memoria de bloque incorporada ha aumentado de 2 Mbit a 25 Mbit.La elección también probablemente determinó que el costo de la tarifa se conservara en el sitio de la oficina de representación alemana en el caché de Google, y sabíamos que costaría $ 18K antes de firmar cualquier NDA. Y con el costo de solo un chip FPGA de $ 15 mil, esto eliminó cualquier pregunta sobre el desarrollo de su propia placa. Las tarjetas serie para FPGA tan grandes generalmente cuestan tanto como las FPGA mismas o son un poco más caras.La adquisición de la placa también trajo muchos conocimientos interesantes, por ejemplo, nuestro distribuidor local estaba convencido de que esta placa cuesta $ 40K, incluido el envío, y en general se arriesga mucho con el 100% de prepago de nuestra parte. Finalmente, 3 de estas placas se compraron sin intermediarios, y ahora se utilizan para crear prototipos de nuestros procesadores DSP.Año 2013

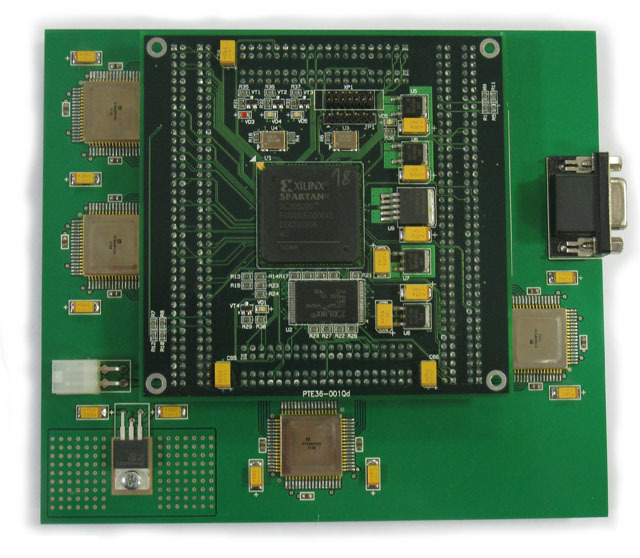

Para el nuevo microcontrolador especializado de 32 bits, se decidió intentar hacer su propia placa. En primer lugar, los desarrolladores de módulos en FPGA deben desarrollar y no tener miedo de usar microcircuitos que son más caros que sus automóviles personales, y en segundo lugar, uno de los distribuidores tenía varios Virtex-6 XC6VLX550T en stock y los ofreció con un gran descuento. El FPGA LX550T es un paso más pequeño que el LX760 (aproximadamente un 30% menos de válvulas), pero el precio final de los tableros, teniendo en cuenta el desarrollo, fue de solo $ 8K. Se ensamblaron 6 tableros. No planeamos distribuirlos a los clientes, sino que organizamos para que los desarrolladores tengan acceso a ellos a través de Internet. La junta ha implementado muchas soluciones interesantes. Por ejemplo, los archivos de firmware se cargaron en la placa como en un dispositivo MassStorage en una tarjeta SD especial, y luego se cargaron en la FPGA.En total, la tarjeta puede tener hasta 10 firmwares diferentes, y a través de un programa de administración especial puede elegir cuál usar en este momento. También se implementaron varias protecciones "del tonto", para no quemar accidentalmente un chip costoso. Todo esto le permite trabajar con estas placas de forma remota, segura y confiar en ellas incluso para los estudiantes. El MK diseñado en FPGA funcionó a una frecuencia de 40 MHz.La placa en sí (prototipo de un microcontrolador especializado de doble núcleo de 32 bits): prototipo de un chip especializado para sensores de conversión de ángulo a código:

prototipo de un chip especializado para sensores de conversión de ángulo a código: desafortunadamente, esta placa tiene varios inconvenientes: se seleccionan conectores defectuosos para conectar módulos adicionales, pero es la mitad del problema, olvidamos arreglarlo agujeros cerca de los conectores, y los módulos se mantienen solo en los conectores. Para obtener acceso a algunos controles en la placa principal, debe averiguar los módulos de expansión.

desafortunadamente, esta placa tiene varios inconvenientes: se seleccionan conectores defectuosos para conectar módulos adicionales, pero es la mitad del problema, olvidamos arreglarlo agujeros cerca de los conectores, y los módulos se mantienen solo en los conectores. Para obtener acceso a algunos controles en la placa principal, debe averiguar los módulos de expansión.Experiencia doméstica

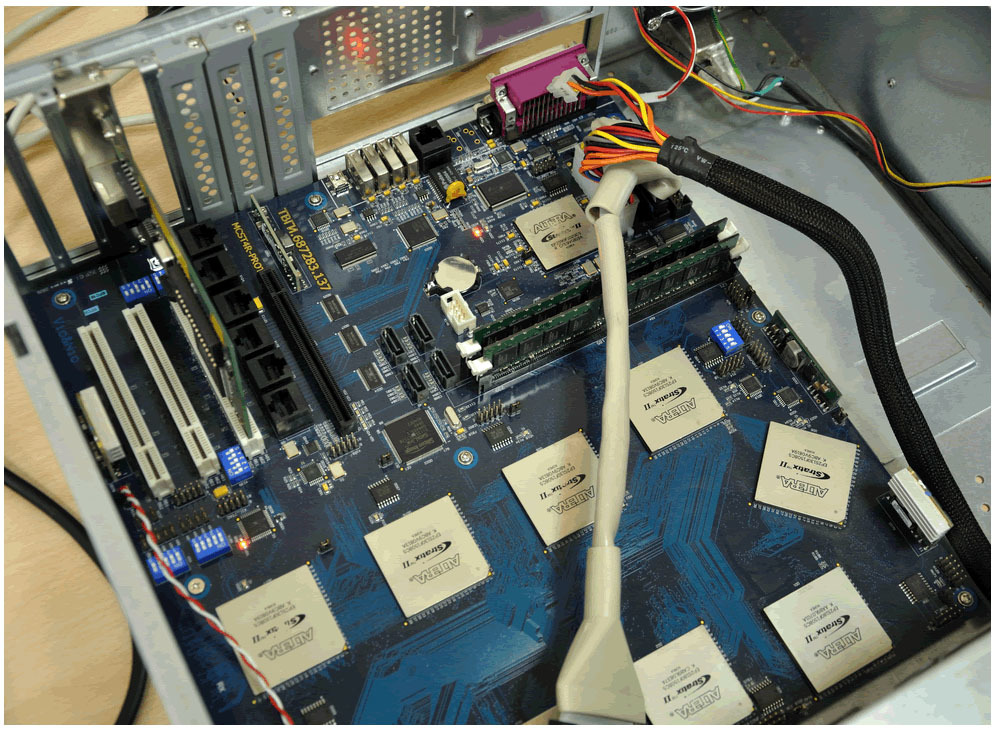

¿Pero qué pasa con otros desarrolladores de chips personalizados? Por ejemplo, el MCST al prototipar VLSI 1891VM6Ya (R-1000, un procesador de cuatro núcleos con arquitectura SPARC v.9 de 64 bits) utilizó una placa especializada con 10 FPGA Altera Stratix II (4 x EP2S180 + 5 x EP2S130 + 1 x EP2S90). El volumen total de puertas lógicas del sistema se puede estimar en 20 millones. Ahora un chip EP2S180 cuesta alrededor de $ 8K. Entonces, el costo de solo chips FPGA en el prototipo excede los $ 50K.Para la creación de prototipos del procesador Elbrus-4C +, ya se requerían 21 microcircuitos Altera Stratix IV EP4SE820 y con un volumen total de 100 millones de válvulas (aunque el MCST en sí cita una cifra de 750 millones) y cuesta alrededor de $ 200K. Al mismo tiempo, la frecuencia de trabajo del prototipo es de 9 MHz.

Ahora un chip EP2S180 cuesta alrededor de $ 8K. Entonces, el costo de solo chips FPGA en el prototipo excede los $ 50K.Para la creación de prototipos del procesador Elbrus-4C +, ya se requerían 21 microcircuitos Altera Stratix IV EP4SE820 y con un volumen total de 100 millones de válvulas (aunque el MCST en sí cita una cifra de 750 millones) y cuesta alrededor de $ 200K. Al mismo tiempo, la frecuencia de trabajo del prototipo es de 9 MHz.Experiencia extranjera

Ahora las empresas especializadas en el desarrollo de herramientas CAD para microelectrónica ofrecen soluciones especializadas para la creación de prototipos FPGA, aunque también se pueden encontrar módulos adecuados para la creación de prototipos en otras empresas. Intel e IBM tienen prototipos FPGA, pero sus características no se anuncian, y se conocen en un círculo amplio solo cuando el prototipo ya está desactualizado.Cadence ofrece una plataforma especial de creación rápida de prototipos construida sobre el FPGA Altera Stratix-4 EP4SE820. En la configuración mínima, la plataforma consta de dos (con un volumen total de 10 millones de puertas), en un máximo de seis FPGA (con un volumen de hasta 30 millones de puertas). El precio de un chip EP4SE820 hoy es de ~ $ 10K. El nuevo sistema de Cadence se llama Protium y se basa en el Xilinx Virtex-7 XC7V2000T y le permite implementar desde 25 millones en dos FPGA hasta 100 millones de válvulas en ocho. El costo de un chip XC7V2000T ahora es de aproximadamente $ 20K. Aquellos. Protium totalmente equipado costará al menos $ 160K.Además de las herramientas de desarrollo, Aldec también ofrece una plataforma para la creación de prototipos FPGA de HES-7.

El nuevo sistema de Cadence se llama Protium y se basa en el Xilinx Virtex-7 XC7V2000T y le permite implementar desde 25 millones en dos FPGA hasta 100 millones de válvulas en ocho. El costo de un chip XC7V2000T ahora es de aproximadamente $ 20K. Aquellos. Protium totalmente equipado costará al menos $ 160K.Además de las herramientas de desarrollo, Aldec también ofrece una plataforma para la creación de prototipos FPGA de HES-7. Hasta seis Xilinx Virtex-7 XC7V2000T o UltraSacle XCVU440 se encuentran en una placa. En el caso de la implementación del módulo basado en el FPGA UltraSacle XCVU440, el número total de puertas alcanza los 158 millones. Con una placa adicional, puede ensamblar 24 chips FPGA en un solo módulo y obtener 633 millones de puertas. El costo de un chip XCVU440 ahora es de $ 49K. Y el costo total máximo de todos los FPGA excede 1M $.Synopsys tiene probablemente la mayor experiencia en el desarrollo de plataformas para la creación de prototipos FPGA. Sus primeros modelos se basaron en el FPGA Virtex-6 (HAPS-60), luego Virtex-7 (HAPS-70). Su último desarrollo, HAPS-80, en un solo módulo contiene de uno a cuatro FPGA Xilinx UltraScale XCVU440.

Hasta seis Xilinx Virtex-7 XC7V2000T o UltraSacle XCVU440 se encuentran en una placa. En el caso de la implementación del módulo basado en el FPGA UltraSacle XCVU440, el número total de puertas alcanza los 158 millones. Con una placa adicional, puede ensamblar 24 chips FPGA en un solo módulo y obtener 633 millones de puertas. El costo de un chip XCVU440 ahora es de $ 49K. Y el costo total máximo de todos los FPGA excede 1M $.Synopsys tiene probablemente la mayor experiencia en el desarrollo de plataformas para la creación de prototipos FPGA. Sus primeros modelos se basaron en el FPGA Virtex-6 (HAPS-60), luego Virtex-7 (HAPS-70). Su último desarrollo, HAPS-80, en un solo módulo contiene de uno a cuatro FPGA Xilinx UltraScale XCVU440. Los módulos listos para usar se pueden combinar en un solo rack. Y en este caso, el volumen total es un récord de 1,6 mil millones de válvulas.Cuando se usa un FPGA, la frecuencia máxima es de hasta 300 MHz, cuando se usan los vecinos en un módulo a 100 MHz, cuando se usan varios módulos, la frecuencia se reduce a 30 MHz.

Los módulos listos para usar se pueden combinar en un solo rack. Y en este caso, el volumen total es un récord de 1,6 mil millones de válvulas.Cuando se usa un FPGA, la frecuencia máxima es de hasta 300 MHz, cuando se usan los vecinos en un módulo a 100 MHz, cuando se usan varios módulos, la frecuencia se reduce a 30 MHz. Por lo tanto, teniendo aproximadamente $ 3.5M para la compra de FPGA, puede ensamblar una plataforma adecuada para la creación de prototipos Intel Xeon E7. Bueno, o espere 20 años, cuando los FPGA de tal volumen caigan en precio a un par de cientos de dólares.

Por lo tanto, teniendo aproximadamente $ 3.5M para la compra de FPGA, puede ensamblar una plataforma adecuada para la creación de prototipos Intel Xeon E7. Bueno, o espere 20 años, cuando los FPGA de tal volumen caigan en precio a un par de cientos de dólares. Source: https://habr.com/ru/post/es387653/

All Articles