Distribución de elefantes: tableros FPGA para proyectos educativos con MIPSfpga

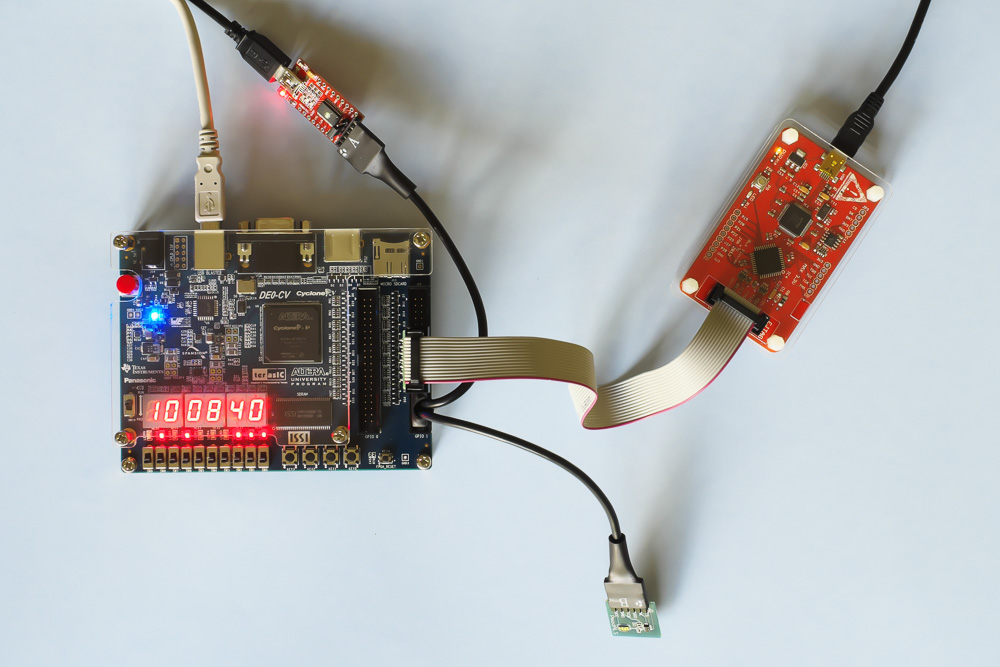

Hace un mes, se realizaron seminarios sobre MIPSfpga ( 1 , 2 , 3 , 4 ) en universidades rusas , y un caballero del NIIIS llamado Anton Pavlov escribió una nota sobre sus propias mejoras MIPSfpga "MIPSfpga: fuera del canon" . Dado que los profesores conocieron positivamente el nuevo producto para enseñar a los estudiantes de electrónica en general, surgió la idea de ayudar a comenzar con las juntas y, al mismo tiempo, para varias personas y organizaciones.En particular, en honor al Año Nuevo, estoy en cooperación con Vitaliy Kravchenko de univeda.ruEstamos planeando una pequeña distribución de elefantes, es decir, tableros Terasic DE0-CV gratuitos con FPGA Altera Cyclone V. Para que pueda repetir la acción de Anton Pavlov. Dado que esta distribución particular se realiza _no_ con el dinero de Imagination Technologies, no con el dinero Altera y no con el dinero del Centro Científico y de Producción de Elvis, sino con el dinero de benefactores privados, incluido yo personalmente, los elefantes se distribuirán con las condiciones bastante específicas que se describen a continuación. Los objetivos del evento: 1. Aumentar el nivel de participación de las universidades rusas en la investigación mundial en el campo de la microarquitectura de procesadores, el diseño de SoC y sistemas heterogéneos multinúcleo 2. Aumentar el número de textos rusos en MIPS Insider para que los visitantes de la industria electrónica internacional y la academia comiencen a comprender que los rusos comienzan a llegar. 3. Hacer, en nombre de la comunidad, un montón de materiales de capacitación sobre MIPSfpga, que podrían ser utilizados tanto por profesores de universidades rusas como por profesores universitarios en otros países: Estados Unidos, Japón, China, etc.Términos:1. Es deseable que el beneficiario sea maestro, estudiante graduado o estudiante de una universidad rusa.2. Es deseable que esta universidad no fuera la Universidad Estatal de Moscú, el Instituto de Física y Tecnología de Moscú, MEPhI, MIET e ITMO, que pueden recibir estas tarifas de otras fuentes.3. Es muy deseable que antes de recibir el tablero, un amigo creativo me envíe no solo una descripción del proyecto, sino también un código en Verilog o VHDL, C y / o ensamblador, con el cual simuló un prototipo de un futuro sistema sintetizado en el entorno ModelSim o Icarus. Los diagramas de tiempos también son bienvenidos.4. El código del proyecto una vez finalizado se carga en http://github.com/MIPSfpga - vea http://github.com/MIPSfpga/mipsfpga-plus5. como ejemplo . También se describe en la sección Wiki:5.1. Qué hay en cada archivo5.2. Jerarquía de los módulos de hardware5.3. Cómo simular: instrucciones con capturas de pantalla5.4. Diagramas de temporización de simulación5.5. Cómo sintetizar: instrucciones con capturas de pantalla5.6. Resultados de síntesis: tamaño y frecuencia máxima5.7. Descripción de la parte del software5.8. Fotos del FPGA de trabajo6. Esto se presenta en http://geektimes.ru en la forma del artículo7. Lo mismo se presenta en http://silicon-russia.com8. Lo mismo se presenta en http://community.imgtec.com / foros / cat / mips-insider / mipsfpga9. El idioma (6), (7), (8) puede ser ruso o inglés10. Si no hace nada con el tablero durante un mes, se lo retira y lo transfiere a otra persona11. Si nosotros (UnivEDA) y nosotros haremos algún evento en Rusia, como competiciones o entrenamientos, también le cobraremos una tarifa tome el tiempo atrásEjemplos de proyectos con placas:1. Interfaz entre MIPSfpga y sensores con interfaces SPI, I2C, UART y otros. Sensores de humedad, temperatura, sonido, brújulas, telémetro, etc.2. La interfaz entre MIPSfpga y externa en relación con la memoria FPGA - SDRAM, DDR, etc. (en los ejemplos actuales, la memoria del sistema está construida a partir de la memoria de bloque dentro del FPGA)3. La interfaz entre MIPSfpga y dispositivos más grandes es una pantalla VGA, mouse, teclado, joystick.4. Visualización de la memoria caché ejecutando el procesador a una frecuencia de 1 reloj por segundo y emitiendo señales relacionadas con la transacción (solicitud, fallo, etc.).5. Visualización del funcionamiento del transportador y los dispositivos aritméticos iniciando el procesador con una frecuencia de 1 reloj por segundo y emitiendo señales de control del transportador, etc.6. Agregar comandos al procesador utilizando la interfaz CorExtend / Instrucciones definidas por el usuario (UDI). Un ejemplo son los comandos especiales de cifrado.7. Trabajo de laboratorio con una demostración de la operación de interrupción en diferentes modos y un controlador de interrupción.8. Puentes entre el bus AHB-Lite y otros buses: AXI, APB, OCP, Wishbone, PLB, etc.9. Sistemas multiprocesador sin la coherencia de cachés de primer nivel y (para los más avanzados) con cachés coherentes e implementación de protocolos como MESI.10. Portar a MIPSfpga varios programas y sistemas operativos: desde RTOS simple a varias variantes de Linux (MIPSfpga es compatible con TLB MMU).Envíe sugerencias a yuri.panchul@imgtec.com con una copia de yuri@panchul.com

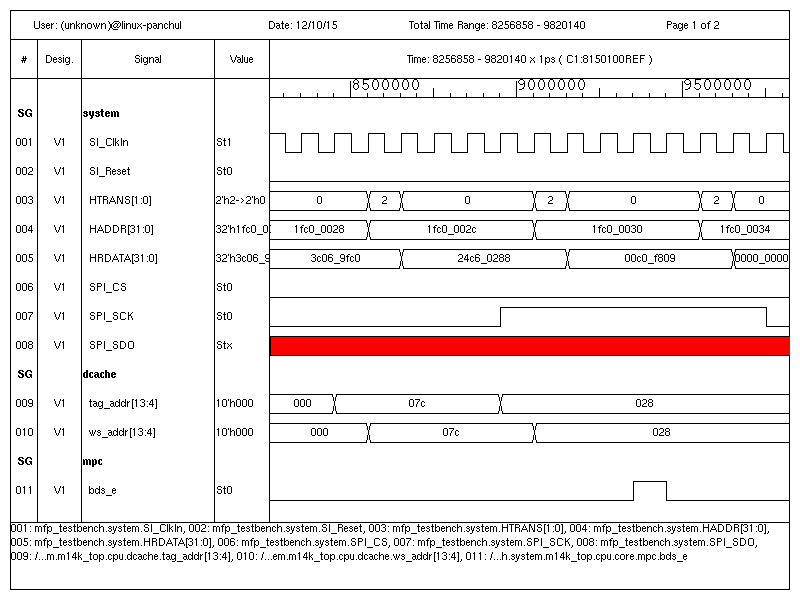

3. Hacer, en nombre de la comunidad, un montón de materiales de capacitación sobre MIPSfpga, que podrían ser utilizados tanto por profesores de universidades rusas como por profesores universitarios en otros países: Estados Unidos, Japón, China, etc.Términos:1. Es deseable que el beneficiario sea maestro, estudiante graduado o estudiante de una universidad rusa.2. Es deseable que esta universidad no fuera la Universidad Estatal de Moscú, el Instituto de Física y Tecnología de Moscú, MEPhI, MIET e ITMO, que pueden recibir estas tarifas de otras fuentes.3. Es muy deseable que antes de recibir el tablero, un amigo creativo me envíe no solo una descripción del proyecto, sino también un código en Verilog o VHDL, C y / o ensamblador, con el cual simuló un prototipo de un futuro sistema sintetizado en el entorno ModelSim o Icarus. Los diagramas de tiempos también son bienvenidos.4. El código del proyecto una vez finalizado se carga en http://github.com/MIPSfpga - vea http://github.com/MIPSfpga/mipsfpga-plus5. como ejemplo . También se describe en la sección Wiki:5.1. Qué hay en cada archivo5.2. Jerarquía de los módulos de hardware5.3. Cómo simular: instrucciones con capturas de pantalla5.4. Diagramas de temporización de simulación5.5. Cómo sintetizar: instrucciones con capturas de pantalla5.6. Resultados de síntesis: tamaño y frecuencia máxima5.7. Descripción de la parte del software5.8. Fotos del FPGA de trabajo6. Esto se presenta en http://geektimes.ru en la forma del artículo7. Lo mismo se presenta en http://silicon-russia.com8. Lo mismo se presenta en http://community.imgtec.com / foros / cat / mips-insider / mipsfpga9. El idioma (6), (7), (8) puede ser ruso o inglés10. Si no hace nada con el tablero durante un mes, se lo retira y lo transfiere a otra persona11. Si nosotros (UnivEDA) y nosotros haremos algún evento en Rusia, como competiciones o entrenamientos, también le cobraremos una tarifa tome el tiempo atrásEjemplos de proyectos con placas:1. Interfaz entre MIPSfpga y sensores con interfaces SPI, I2C, UART y otros. Sensores de humedad, temperatura, sonido, brújulas, telémetro, etc.2. La interfaz entre MIPSfpga y externa en relación con la memoria FPGA - SDRAM, DDR, etc. (en los ejemplos actuales, la memoria del sistema está construida a partir de la memoria de bloque dentro del FPGA)3. La interfaz entre MIPSfpga y dispositivos más grandes es una pantalla VGA, mouse, teclado, joystick.4. Visualización de la memoria caché ejecutando el procesador a una frecuencia de 1 reloj por segundo y emitiendo señales relacionadas con la transacción (solicitud, fallo, etc.).5. Visualización del funcionamiento del transportador y los dispositivos aritméticos iniciando el procesador con una frecuencia de 1 reloj por segundo y emitiendo señales de control del transportador, etc.6. Agregar comandos al procesador utilizando la interfaz CorExtend / Instrucciones definidas por el usuario (UDI). Un ejemplo son los comandos especiales de cifrado.7. Trabajo de laboratorio con una demostración de la operación de interrupción en diferentes modos y un controlador de interrupción.8. Puentes entre el bus AHB-Lite y otros buses: AXI, APB, OCP, Wishbone, PLB, etc.9. Sistemas multiprocesador sin la coherencia de cachés de primer nivel y (para los más avanzados) con cachés coherentes e implementación de protocolos como MESI.10. Portar a MIPSfpga varios programas y sistemas operativos: desde RTOS simple a varias variantes de Linux (MIPSfpga es compatible con TLB MMU).Envíe sugerencias a yuri.panchul@imgtec.com con una copia de yuri@panchul.com

Source: https://habr.com/ru/post/es387803/

All Articles