Tecnología 3D NAND Flash

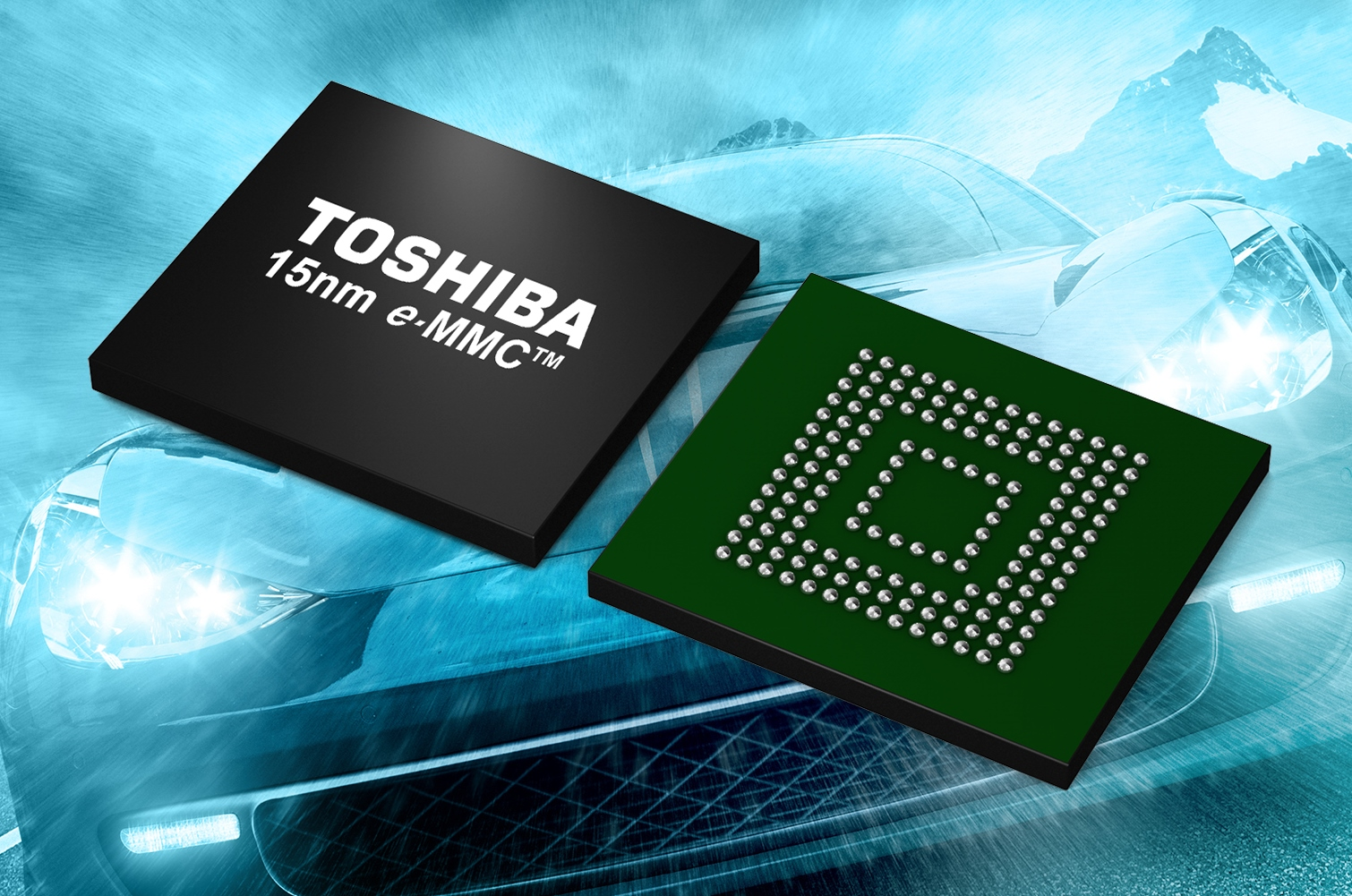

Hola a todos! Como saben, la memoria flash plana NAND moderna casi ha agotado su potencial. Su principal problema es que cada vez es más difícil reducir el tamaño del cristal. Según los expertos, los estándares tecnológicos de 14-15 nm se convertirán en el límite de la memoria flash plana, al menos en el futuro cercano. Y será reemplazado por la tecnología de memoria flash "vertical" - 3D NAND.Es muy importante comprender qué impide la reducción adicional del tamaño del cristal. En primer lugar, el desarrollo de procesos de fabricación más finos requiere equipos costosos, cuya compra puede no estar justificada en el futuro desde un punto de vista económico. Y si la adquisición de nuevas máquinas litográficas es un problema solucionable, entonces el problema del flujo de carga de una celda a otra, debido a los errores que ocurren, no es tan fácil de resolver.

Source: https://habr.com/ru/post/es391899/

All Articles