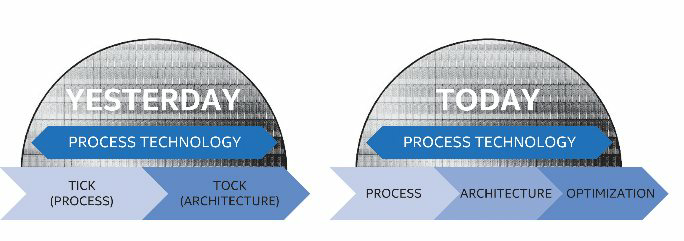

Intel abandona la estrategia tick-to-tack

Ahora los procesadores harán el ciclo "proceso-arquitectura-optimización"

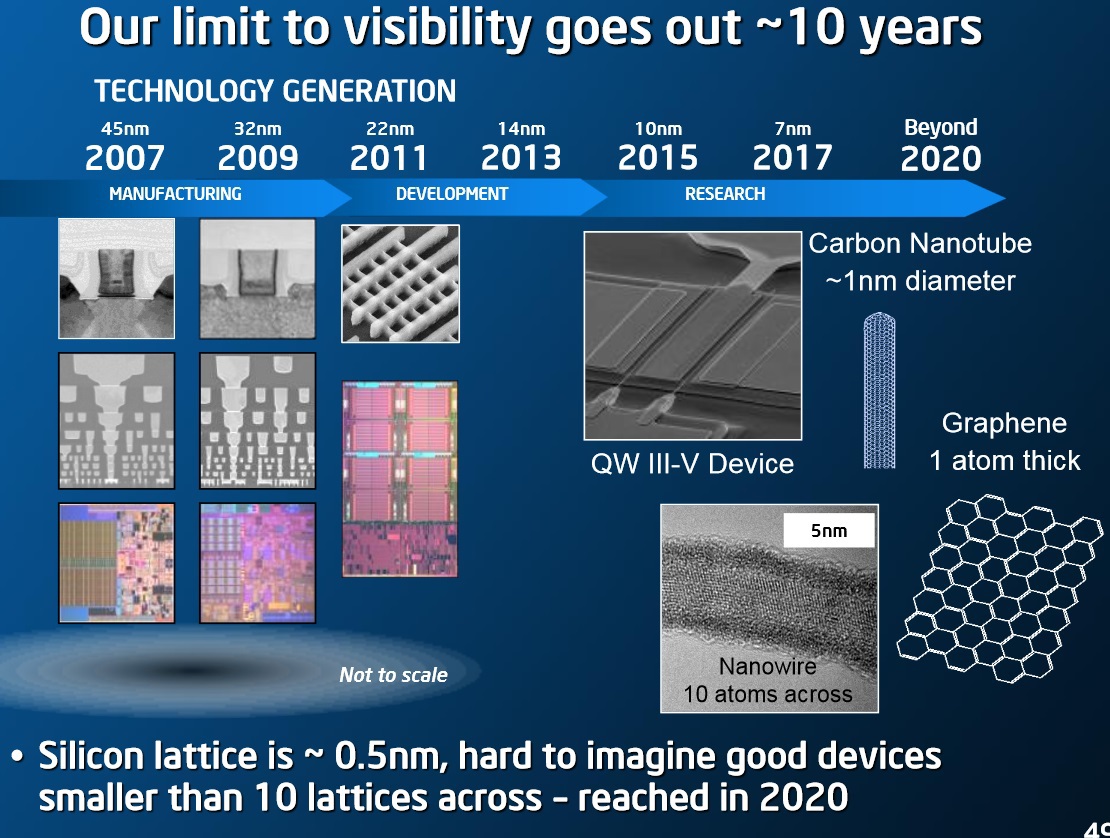

Como empresa pública con más de $ 10 millones en activos propiedad de más de 500 accionistas, Intel ha proporcionado a la Comisión de Bolsa y Valores de EE. UU . Un informe anual 10-K . De particular interés en el documento de 150 páginas es la página 14, en la que Intel reconoce que está abandonando la estrategia tick-to-tack a favor del nuevo concepto de optimización de arquitectura de proceso.Tick-Tock es un modelo de desarrollo de microprocesador que Intel ha estado utilizando desde 2007. En ciertos intervalos, la tecnología le permite reducir el tamaño de los elementos en el tablero, lo que reduce el consumo de energía y ajusta una mayor cantidad de transistores en un chip del mismo tamaño. Si es posible ajustar más elementos, entonces es posible una nueva microarquitectura: se agregan nuevos comandos, mejora la lógica de trabajo, aumenta el número de elementos diferentes.La estrategia tick-to-tack divide los dos procesos. Sobre el "tic" los transistores se vuelven más pequeños. Hay cambios en la microarquitectura, pero son insignificantes. "Entonces" significa la creación de una nueva microarquitectura, es decir, grandes cambios, a veces fundamentales, para lograr grandes ganancias de productividad.Intel ha estado avanzando tales pasos durante casi 10 años. Cada uno de ellos lleva de un año a un año y medio. Pero recientemente, se ha vuelto cada vez más difícil reducir el proceso de fabricación. Al cambiar de 22 a 14 nanómetros , aparecieron retrasos de 6 a 9 meses. En este momento, era necesario aumentar el porcentaje de producción de chips viables de las obleas a un nivel aceptable al costo. La ley de Moore, que describe la duplicación del número de transistores en un chip cada 24 meses, debe ajustarse.En el futuro, se planea la transición a 10, y luego a 7 y 5 nanómetros. Alcanzar nuevas fronteras significa el posible uso de la litografía en ultravioleta profundo, patrón cuádruple autoalineado (SAQP), el rechazo del silicio a favor de los semiconductores III-V, los nanotubos de carbono y el grafeno.

Como empresa pública con más de $ 10 millones en activos propiedad de más de 500 accionistas, Intel ha proporcionado a la Comisión de Bolsa y Valores de EE. UU . Un informe anual 10-K . De particular interés en el documento de 150 páginas es la página 14, en la que Intel reconoce que está abandonando la estrategia tick-to-tack a favor del nuevo concepto de optimización de arquitectura de proceso.Tick-Tock es un modelo de desarrollo de microprocesador que Intel ha estado utilizando desde 2007. En ciertos intervalos, la tecnología le permite reducir el tamaño de los elementos en el tablero, lo que reduce el consumo de energía y ajusta una mayor cantidad de transistores en un chip del mismo tamaño. Si es posible ajustar más elementos, entonces es posible una nueva microarquitectura: se agregan nuevos comandos, mejora la lógica de trabajo, aumenta el número de elementos diferentes.La estrategia tick-to-tack divide los dos procesos. Sobre el "tic" los transistores se vuelven más pequeños. Hay cambios en la microarquitectura, pero son insignificantes. "Entonces" significa la creación de una nueva microarquitectura, es decir, grandes cambios, a veces fundamentales, para lograr grandes ganancias de productividad.Intel ha estado avanzando tales pasos durante casi 10 años. Cada uno de ellos lleva de un año a un año y medio. Pero recientemente, se ha vuelto cada vez más difícil reducir el proceso de fabricación. Al cambiar de 22 a 14 nanómetros , aparecieron retrasos de 6 a 9 meses. En este momento, era necesario aumentar el porcentaje de producción de chips viables de las obleas a un nivel aceptable al costo. La ley de Moore, que describe la duplicación del número de transistores en un chip cada 24 meses, debe ajustarse.En el futuro, se planea la transición a 10, y luego a 7 y 5 nanómetros. Alcanzar nuevas fronteras significa el posible uso de la litografía en ultravioleta profundo, patrón cuádruple autoalineado (SAQP), el rechazo del silicio a favor de los semiconductores III-V, los nanotubos de carbono y el grafeno. Diapositiva de la presentación hace un año .Un documento para la Securities and Exchange Commission aborda el curso de desarrollo general de Intel. La compañía explica que el tiempo total de uso del producto para la tecnología de proceso actual se incrementará a 14 nanómetros y el futuro a 10 nm. Pero el ritmo de mercado de los lanzamientos de nuevos productos continuará. ¿Cómo se logrará esto? Intel da la imagen, que en esta publicación se publica antes del kat. En él, "tick-tock" se llama tecnología de ayer, y el ciclo de tres pasos "proceso-arquitectura-optimización" (PAO) se declara la realidad actual.Broadwell, el seguidor del Haswell de 22 nm, ayudó a calcular 14 nanómetros. La microarquitectura actual de Intel es Skylake, la sexta generación de Core, la "así" tecnología de proceso de 14 nm. Su seguidor, Kaby Lake, también tendrá 14 nm, pero proporcionará "mejoras de rendimiento significativas sobre la familia de procesadores Core de sexta generación".Alcanzar 10 nanómetros puede ser ayudado por la colaboración mencionada en el documento con ASML en el estudio de la fotolitografía en ultravioleta profundo, incluida la aplicable a placas con diámetros de 300 y 450 milímetros. Intel aún mantiene el liderazgo: 14 nm se introdujeron en agosto de 2014, Samsung y TSMC se retiraron más tarde.Se espera que el Kaby Lake de 14nm sea lanzado este año. Según los planes actuales, los productos de la microarquitectura Cannonlake de 10 nanómetros deberían aparecer en 2017. En el ciclo de tres pasos, es fácil ver ventajas obvias para el usuario final: la misma placa base puede ser adecuada para productos de dos o más generaciones.

Diapositiva de la presentación hace un año .Un documento para la Securities and Exchange Commission aborda el curso de desarrollo general de Intel. La compañía explica que el tiempo total de uso del producto para la tecnología de proceso actual se incrementará a 14 nanómetros y el futuro a 10 nm. Pero el ritmo de mercado de los lanzamientos de nuevos productos continuará. ¿Cómo se logrará esto? Intel da la imagen, que en esta publicación se publica antes del kat. En él, "tick-tock" se llama tecnología de ayer, y el ciclo de tres pasos "proceso-arquitectura-optimización" (PAO) se declara la realidad actual.Broadwell, el seguidor del Haswell de 22 nm, ayudó a calcular 14 nanómetros. La microarquitectura actual de Intel es Skylake, la sexta generación de Core, la "así" tecnología de proceso de 14 nm. Su seguidor, Kaby Lake, también tendrá 14 nm, pero proporcionará "mejoras de rendimiento significativas sobre la familia de procesadores Core de sexta generación".Alcanzar 10 nanómetros puede ser ayudado por la colaboración mencionada en el documento con ASML en el estudio de la fotolitografía en ultravioleta profundo, incluida la aplicable a placas con diámetros de 300 y 450 milímetros. Intel aún mantiene el liderazgo: 14 nm se introdujeron en agosto de 2014, Samsung y TSMC se retiraron más tarde.Se espera que el Kaby Lake de 14nm sea lanzado este año. Según los planes actuales, los productos de la microarquitectura Cannonlake de 10 nanómetros deberían aparecer en 2017. En el ciclo de tres pasos, es fácil ver ventajas obvias para el usuario final: la misma placa base puede ser adecuada para productos de dos o más generaciones.Source: https://habr.com/ru/post/es392041/

All Articles