La historia del desarrollo de procesadores: el final de los 80 - el comienzo de los 2000

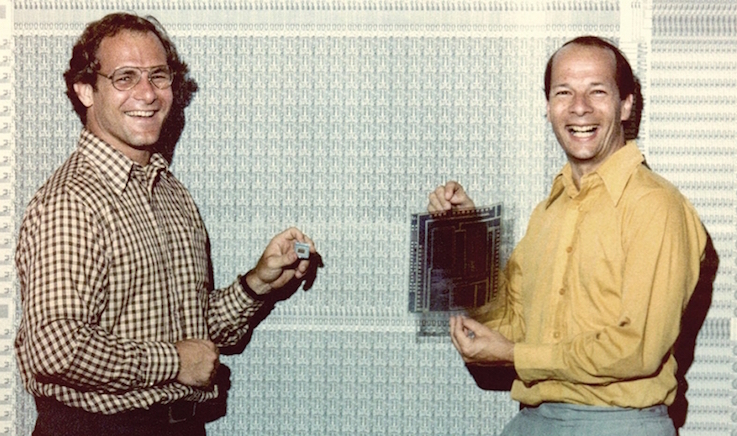

Continuando con el tema del primer artículo está la historia de la evolución de los procesadores desde finales del siglo XX hasta principios del siglo XXI.Muchos procesadores de los años 80 utilizaron la arquitectura CISC (conjunto de instrucciones complejas de computación). Los chips eran bastante complejos y caros, así como no lo suficientemente productivos. Era necesario modernizar la producción y aumentar el número de transistores.Arquitectura RISCEn 1980, se lanzó el proyecto Berkeley RISC, dirigido por los ingenieros estadounidenses David Patterson y Carlo Sequin. RISC (computadora de conjunto de instrucciones restringido): arquitectura de procesador con mayor velocidad debido a instrucciones simplificadas. Gerentes de proyecto Berkeley RISC - David Patterson y Carlo SequinDespués de varios años de fructífero trabajo, aparecieron en el mercado varias muestras de procesadores con un conjunto reducido de instrucciones. Cada instrucción de la plataforma RISC fue simple y se ejecutó en un solo ciclo. También hubo muchos más registros de propósito general. Además, se utilizó la canalización con instrucciones simplificadas, lo que permitió aumentar efectivamente la frecuencia del reloj.RISC I fue lanzado en 1982 y contenía más de 44,420 transistores. Tenía solo 32 instrucciones y trabajaba a una frecuencia de 4 MHz. El siguiente RISC II consistió en 40,760 transistores, usó 39 instrucciones y fue más rápido. Procesadores

Gerentes de proyecto Berkeley RISC - David Patterson y Carlo SequinDespués de varios años de fructífero trabajo, aparecieron en el mercado varias muestras de procesadores con un conjunto reducido de instrucciones. Cada instrucción de la plataforma RISC fue simple y se ejecutó en un solo ciclo. También hubo muchos más registros de propósito general. Además, se utilizó la canalización con instrucciones simplificadas, lo que permitió aumentar efectivamente la frecuencia del reloj.RISC I fue lanzado en 1982 y contenía más de 44,420 transistores. Tenía solo 32 instrucciones y trabajaba a una frecuencia de 4 MHz. El siguiente RISC II consistió en 40,760 transistores, usó 39 instrucciones y fue más rápido. Procesadores RISC IIprocesadores MIPS: R2000, R3000, R4000 y R4400La arquitectura de los procesadores MIPS (microprocesador sin etapas de tubería interconectadas) preveía la presencia de unidades auxiliares en el cristal. MIPS usó un transportador extendido.En 1984, un grupo de investigadores dirigido por el científico estadounidense John Hennessey fundó una empresa que diseña dispositivos microelectrónicos. MIPS ha licenciado arquitectura de microprocesador y núcleos IP para dispositivos domésticos inteligentes, redes y aplicaciones móviles. En 1985, se lanzó el primer producto de la compañía: el R2000 de 32 bits, que en 1988 se finalizó en el R3000. El modelo actualizado tenía soporte para multiprocesamiento, caché de instrucciones y caché de datos. El procesador ha encontrado aplicación en estaciones de trabajo de la serie SG de diferentes compañías. El R3000 también se convirtió en la base de la consola de juegos Sony PlayStation.

RISC IIprocesadores MIPS: R2000, R3000, R4000 y R4400La arquitectura de los procesadores MIPS (microprocesador sin etapas de tubería interconectadas) preveía la presencia de unidades auxiliares en el cristal. MIPS usó un transportador extendido.En 1984, un grupo de investigadores dirigido por el científico estadounidense John Hennessey fundó una empresa que diseña dispositivos microelectrónicos. MIPS ha licenciado arquitectura de microprocesador y núcleos IP para dispositivos domésticos inteligentes, redes y aplicaciones móviles. En 1985, se lanzó el primer producto de la compañía: el R2000 de 32 bits, que en 1988 se finalizó en el R3000. El modelo actualizado tenía soporte para multiprocesamiento, caché de instrucciones y caché de datos. El procesador ha encontrado aplicación en estaciones de trabajo de la serie SG de diferentes compañías. El R3000 también se convirtió en la base de la consola de juegos Sony PlayStation. Procesador R3000En 1991, se lanzó la nueva generación de la línea R4000. Este procesador tenía una arquitectura de 64 bits, un coprocesador integrado y funcionaba a una frecuencia de reloj de 100 MHz. El caché interno era de 16 KB (8 KB de instrucciones de caché y 8 KB de datos de caché).Un año después, se lanzó una versión modificada del procesador, R4400. En este modelo, el caché ha aumentado a 32 KB (16 KB de comandos de caché y 16 KB de datos de caché). El procesador podría funcionar a una frecuencia de 100 MHz - 250 MHz.Procesadores MIPS: R8000 y R10000En 1994, apareció el primer procesador con una implementación superescalar de la arquitectura MIPS, el R8000. La capacidad del caché de datos fue de 16 KB. Esta CPU tenía un ancho de banda de acceso a datos alto (hasta 1.2 Gb / s) en combinación con una alta velocidad de operaciones. La frecuencia alcanzó 75 MHz - 90 MHz. Se utilizaron seis circuitos: un dispositivo para instrucciones enteras, para instrucciones de coma flotante, tres descriptores de caché de RAM secundario y un controlador de caché ASIC.

Procesador R3000En 1991, se lanzó la nueva generación de la línea R4000. Este procesador tenía una arquitectura de 64 bits, un coprocesador integrado y funcionaba a una frecuencia de reloj de 100 MHz. El caché interno era de 16 KB (8 KB de instrucciones de caché y 8 KB de datos de caché).Un año después, se lanzó una versión modificada del procesador, R4400. En este modelo, el caché ha aumentado a 32 KB (16 KB de comandos de caché y 16 KB de datos de caché). El procesador podría funcionar a una frecuencia de 100 MHz - 250 MHz.Procesadores MIPS: R8000 y R10000En 1994, apareció el primer procesador con una implementación superescalar de la arquitectura MIPS, el R8000. La capacidad del caché de datos fue de 16 KB. Esta CPU tenía un ancho de banda de acceso a datos alto (hasta 1.2 Gb / s) en combinación con una alta velocidad de operaciones. La frecuencia alcanzó 75 MHz - 90 MHz. Se utilizaron seis circuitos: un dispositivo para instrucciones enteras, para instrucciones de coma flotante, tres descriptores de caché de RAM secundario y un controlador de caché ASIC. Procesador R8000En 1996, se lanzó una versión revisada: R10000. El procesador incluía 32 KB del caché primario de datos e instrucciones. La CPU funcionaba a una frecuencia de 150 MHz - 250 MHz.A finales de los 90, MIPS comenzó a vender licencias para las arquitecturas MIPS32 y MIPS64 de 32 y 64 bits.Procesadores SPARCSun Microsystems, que ha desarrollado la arquitectura escalable SPARC (Arquitectura de procesador escalable), se unió a las filas de procesadores. El primer procesador del mismo nombre se lanzó a finales de los 80 y se llamó SPARC V7. Su frecuencia alcanzó 14.28 MHz - 40 MHz.En 1992, apareció la siguiente versión de 32 bits llamada SPARC V8, sobre la base de la cual se creó el procesador microSPARC. La frecuencia del reloj era de 40 MHz - 50 MHz.Texas Instruments, Fujitsu, Philips y otros colaboraron en la arquitectura SPARC V9 de próxima generación con Sun Microsystems. La plataforma se expandió a 64 bits y fue superescalar con una tubería de 9 etapas. SPARC V9 proporcionó el uso de la memoria caché de primer nivel, dividida en instrucciones y datos (cada uno con una capacidad de 16 KB), así como el segundo nivel con una capacidad de 512 KB - 1024 KB. Procesador

Procesador R8000En 1996, se lanzó una versión revisada: R10000. El procesador incluía 32 KB del caché primario de datos e instrucciones. La CPU funcionaba a una frecuencia de 150 MHz - 250 MHz.A finales de los 90, MIPS comenzó a vender licencias para las arquitecturas MIPS32 y MIPS64 de 32 y 64 bits.Procesadores SPARCSun Microsystems, que ha desarrollado la arquitectura escalable SPARC (Arquitectura de procesador escalable), se unió a las filas de procesadores. El primer procesador del mismo nombre se lanzó a finales de los 80 y se llamó SPARC V7. Su frecuencia alcanzó 14.28 MHz - 40 MHz.En 1992, apareció la siguiente versión de 32 bits llamada SPARC V8, sobre la base de la cual se creó el procesador microSPARC. La frecuencia del reloj era de 40 MHz - 50 MHz.Texas Instruments, Fujitsu, Philips y otros colaboraron en la arquitectura SPARC V9 de próxima generación con Sun Microsystems. La plataforma se expandió a 64 bits y fue superescalar con una tubería de 9 etapas. SPARC V9 proporcionó el uso de la memoria caché de primer nivel, dividida en instrucciones y datos (cada uno con una capacidad de 16 KB), así como el segundo nivel con una capacidad de 512 KB - 1024 KB. Procesador UltraSPARC IIIProcesadores StrongARMEn 1995, se lanzó un proyecto para desarrollar la familia de microprocesadores StrongARM que implementó el conjunto de instrucciones ARM V4. Estas CPU eran una arquitectura escalar clásica con una tubería de 5 etapas, que incluye unidades de control de memoria y admite un caché de instrucciones y datos de 16 KB cada una.

UltraSPARC IIIProcesadores StrongARMEn 1995, se lanzó un proyecto para desarrollar la familia de microprocesadores StrongARM que implementó el conjunto de instrucciones ARM V4. Estas CPU eran una arquitectura escalar clásica con una tubería de 5 etapas, que incluye unidades de control de memoria y admite un caché de instrucciones y datos de 16 KB cada una. StrongARM SA-110Y ya en 1996, se lanzó el primer procesador basado en StrongARM - SA-110. Trabajó a frecuencias de reloj de 100 MHz, 160 MHz o 200 MHz.Los modelos SA-1100, SA-1110 y SA-1500 también ingresaron al mercado.

StrongARM SA-110Y ya en 1996, se lanzó el primer procesador basado en StrongARM - SA-110. Trabajó a frecuencias de reloj de 100 MHz, 160 MHz o 200 MHz.Los modelos SA-1100, SA-1110 y SA-1500 también ingresaron al mercado. Procesador SA-110 en procesadores Apple MessagePad 2000POWER, POWER2 y PowerPCEn 1985, IBM comenzó a desarrollar la arquitectura RISC de próxima generación como parte del Proyecto América. El desarrollo del procesador POWER (Optimización del rendimiento con RISC mejorado) y el conjunto de instrucciones para el mismo duró 5 años. Fue muy productivo, pero consistió en 11 chips diferentes. Y por lo tanto, en 1992, se lanzó otra versión de procesador que cabía en un chip.

Procesador SA-110 en procesadores Apple MessagePad 2000POWER, POWER2 y PowerPCEn 1985, IBM comenzó a desarrollar la arquitectura RISC de próxima generación como parte del Proyecto América. El desarrollo del procesador POWER (Optimización del rendimiento con RISC mejorado) y el conjunto de instrucciones para el mismo duró 5 años. Fue muy productivo, pero consistió en 11 chips diferentes. Y por lo tanto, en 1992, se lanzó otra versión de procesador que cabía en un chip. Chipset POWEREn 1991, la arquitectura PowerPC (abreviada como PPC) fue desarrollada por IBM, Apple y Motorola Alliance. Consistía en un conjunto básico de funciones de la plataforma POWER, y también soportaba el trabajo en dos modos y era compatible con el modo de operación de 32 bits para la versión de 64 bits. El objetivo principal era las computadoras personales.El procesador PowerPC 601 se utilizó en Macintosh.

Chipset POWEREn 1991, la arquitectura PowerPC (abreviada como PPC) fue desarrollada por IBM, Apple y Motorola Alliance. Consistía en un conjunto básico de funciones de la plataforma POWER, y también soportaba el trabajo en dos modos y era compatible con el modo de operación de 32 bits para la versión de 64 bits. El objetivo principal era las computadoras personales.El procesador PowerPC 601 se utilizó en Macintosh. Procesador PowerPCEn 1993, se introdujo POWER2 con un conjunto ampliado de instrucciones. La velocidad del reloj del procesador varió de 55 MHz a 71.5 MHz, y el caché de datos e instrucciones fue de 128-256 Kb y 32 Kb. Los microcircuitos del procesador (había 8) contenían 23 millones de transistores, y se fabricó utilizando la tecnología CMOS de 0,72 micrómetros.En 1998, IBM lanzó la tercera serie de procesadores POWER3 de 64 bits que son totalmente compatibles con el estándar PowerPC.Entre 2001 y 2010, se lanzaron modelos POWER4 (hasta ocho comandos de ejecución paralela), POWER5 y POWER6 de doble núcleo, y de cuatro a ocho modelos nucleares POWER7.Procesadores Alpha 21064AEn 1992, Digital Equipment Corporation (DEC) lanzó el procesador Alpha 21064 (EV4). Era un cristal superescalar de 64 bits con una arquitectura canalizada y una frecuencia de reloj de 100 MHz - 200 MHz. Fabricado con una tecnología de proceso de 0,75 micras con un bus de procesador externo de 128 bits. Había 16 KB de caché (8 KB de datos y 8 KB de instrucciones).El siguiente modelo de la serie fue el procesador 21164 (EV5), que se lanzó en 1995. Poseía dos bloques enteros y ya contaba tres niveles de memoria caché (dos en el procesador, el tercero - externo). El caché del primer nivel se dividió en un caché de datos y un caché de instrucciones de 8 KB cada uno. La cantidad de caché en el segundo nivel fue de 96 Kb. La velocidad del reloj del procesador varió de 266 MHz a 500 MHz.

Procesador PowerPCEn 1993, se introdujo POWER2 con un conjunto ampliado de instrucciones. La velocidad del reloj del procesador varió de 55 MHz a 71.5 MHz, y el caché de datos e instrucciones fue de 128-256 Kb y 32 Kb. Los microcircuitos del procesador (había 8) contenían 23 millones de transistores, y se fabricó utilizando la tecnología CMOS de 0,72 micrómetros.En 1998, IBM lanzó la tercera serie de procesadores POWER3 de 64 bits que son totalmente compatibles con el estándar PowerPC.Entre 2001 y 2010, se lanzaron modelos POWER4 (hasta ocho comandos de ejecución paralela), POWER5 y POWER6 de doble núcleo, y de cuatro a ocho modelos nucleares POWER7.Procesadores Alpha 21064AEn 1992, Digital Equipment Corporation (DEC) lanzó el procesador Alpha 21064 (EV4). Era un cristal superescalar de 64 bits con una arquitectura canalizada y una frecuencia de reloj de 100 MHz - 200 MHz. Fabricado con una tecnología de proceso de 0,75 micras con un bus de procesador externo de 128 bits. Había 16 KB de caché (8 KB de datos y 8 KB de instrucciones).El siguiente modelo de la serie fue el procesador 21164 (EV5), que se lanzó en 1995. Poseía dos bloques enteros y ya contaba tres niveles de memoria caché (dos en el procesador, el tercero - externo). El caché del primer nivel se dividió en un caché de datos y un caché de instrucciones de 8 KB cada uno. La cantidad de caché en el segundo nivel fue de 96 Kb. La velocidad del reloj del procesador varió de 266 MHz a 500 MHz. DEC Alpha AXP 21064En 1996, los procesadores Alpha 21264 (EV6) salieron con 15,2 millones de transistores, fabricados con la tecnología de proceso de 15,2 micras. Su frecuencia de reloj oscilaba entre 450 MHz y 600 MHz. Los bloques enteros y los bloques de carga / guardado se combinaron en un solo módulo Ebox, y los bloques de punto flotante se combinaron en un módulo Fbox. El caché de primer nivel retuvo una asignación de memoria para instrucciones y datos. El volumen de cada parte fue de 64 Kb. La cantidad de caché en el segundo nivel fue de 2 MB a 8 MB.En 1999, DEC fue comprado por Compaq. Como resultado, la mayor parte de la producción con Alpha se transfirió a API NetWorks, Inc.Procesadores Intel P5 y P54CSegún el diseño de Vinod Dham, se desarrolló el procesador de quinta generación, con nombre en código P5. En 1993, la CPU entró en producción con el nombre de Pentium.Los procesadores centrales P5 se fabricaron utilizando una tecnología de proceso de 800 nanómetros utilizando tecnología bipolar BiCMOS. Contenían 3,1 millones de transistores. Pentium tenía un bus de datos de 64 bits, arquitectura superescalar. Hubo almacenamiento en caché por separado del código del programa y los datos. Se utilizó el caché de primer nivel de 16 KB, dividido en 2 segmentos (8 KB para datos y 8 KB para instrucciones). Los primeros modelos fueron con frecuencias de 60 MHz - 66 MHz.

DEC Alpha AXP 21064En 1996, los procesadores Alpha 21264 (EV6) salieron con 15,2 millones de transistores, fabricados con la tecnología de proceso de 15,2 micras. Su frecuencia de reloj oscilaba entre 450 MHz y 600 MHz. Los bloques enteros y los bloques de carga / guardado se combinaron en un solo módulo Ebox, y los bloques de punto flotante se combinaron en un módulo Fbox. El caché de primer nivel retuvo una asignación de memoria para instrucciones y datos. El volumen de cada parte fue de 64 Kb. La cantidad de caché en el segundo nivel fue de 2 MB a 8 MB.En 1999, DEC fue comprado por Compaq. Como resultado, la mayor parte de la producción con Alpha se transfirió a API NetWorks, Inc.Procesadores Intel P5 y P54CSegún el diseño de Vinod Dham, se desarrolló el procesador de quinta generación, con nombre en código P5. En 1993, la CPU entró en producción con el nombre de Pentium.Los procesadores centrales P5 se fabricaron utilizando una tecnología de proceso de 800 nanómetros utilizando tecnología bipolar BiCMOS. Contenían 3,1 millones de transistores. Pentium tenía un bus de datos de 64 bits, arquitectura superescalar. Hubo almacenamiento en caché por separado del código del programa y los datos. Se utilizó el caché de primer nivel de 16 KB, dividido en 2 segmentos (8 KB para datos y 8 KB para instrucciones). Los primeros modelos fueron con frecuencias de 60 MHz - 66 MHz. Procesador Intel PentiumEn el mismo año, Intel lanzó los procesadores P54C. La producción de nuevos procesadores se transfirió a una tecnología de proceso de 0.6 micrones. La velocidad del procesador fue de 75 MHz, y desde 1994 - 90 MHz y 100 MHz. Un año después, la arquitectura del P54C (P54CS) se transfirió a una tecnología de proceso de 350 nm y la frecuencia del reloj aumentó a 200 MHz.En 1997, el P5 recibió la última actualización: el P55C (Pentium MMX). Ha aparecido la compatibilidad con el conjunto de instrucciones MMX (MultiMedia eXtension). El procesador constaba de 4,5 millones de transistores y está fabricado con tecnología CMOS avanzada de 280 nanómetros. El caché del primer nivel aumentó a 32 Kb (16 Kb para datos y 16 Kb para instrucciones). La frecuencia del procesador alcanzó los 233 MHz.Procesadores AMD K5 y K6En 1995, AMD lanzó el procesador K5. La arquitectura era un núcleo RISC, pero funcionaba con instrucciones complejas de CISC. Los procesadores se fabricaron utilizando tecnología de proceso de 350 o 500 nanómetros, con 4,3 millones de transistores. Todos los K5 tenían cinco bloques enteros y un bloque de coma flotante. El caché de instrucciones era de 16 KB y los datos eran de 8 KB. La velocidad del reloj del procesador varió de 75 MHz a 133 MHz.

Procesador Intel PentiumEn el mismo año, Intel lanzó los procesadores P54C. La producción de nuevos procesadores se transfirió a una tecnología de proceso de 0.6 micrones. La velocidad del procesador fue de 75 MHz, y desde 1994 - 90 MHz y 100 MHz. Un año después, la arquitectura del P54C (P54CS) se transfirió a una tecnología de proceso de 350 nm y la frecuencia del reloj aumentó a 200 MHz.En 1997, el P5 recibió la última actualización: el P55C (Pentium MMX). Ha aparecido la compatibilidad con el conjunto de instrucciones MMX (MultiMedia eXtension). El procesador constaba de 4,5 millones de transistores y está fabricado con tecnología CMOS avanzada de 280 nanómetros. El caché del primer nivel aumentó a 32 Kb (16 Kb para datos y 16 Kb para instrucciones). La frecuencia del procesador alcanzó los 233 MHz.Procesadores AMD K5 y K6En 1995, AMD lanzó el procesador K5. La arquitectura era un núcleo RISC, pero funcionaba con instrucciones complejas de CISC. Los procesadores se fabricaron utilizando tecnología de proceso de 350 o 500 nanómetros, con 4,3 millones de transistores. Todos los K5 tenían cinco bloques enteros y un bloque de coma flotante. El caché de instrucciones era de 16 KB y los datos eran de 8 KB. La velocidad del reloj del procesador varió de 75 MHz a 133 MHz. Procesador AMD K5Bajo la marca K5, se produjeron dos versiones de los procesadores SSA / 5 y 5k86. El primero funcionó a frecuencias de 75 MHz a 100 MHz. El procesador 5k86 funcionaba a frecuencias de 90 MHz a 133 MHz.En 1997, la compañía introdujo el procesador K6, cuya arquitectura era significativamente diferente del K5. Los procesadores se fabricaron utilizando una tecnología de proceso de 350 nanómetros, incluyeron 8,8 millones de transistores, admitieron un cambio en el orden de las instrucciones, un conjunto de instrucciones MMX y un bloque de punto flotante. El área del cristal era de 162 mm². El caché del primer nivel totalizó 64 Kb (32 Kb de datos y 32 Kb de instrucciones). El procesador funcionaba a una frecuencia de 166 MHz, 200 MHz y 233 MHz. La frecuencia del bus del sistema fue de 66 MHz.En 1998, AMD lanzó chips con una arquitectura K6-2 mejorada, con 9.3 millones de transistores fabricados utilizando una tecnología de proceso de 250 nanómetros. La frecuencia máxima del chip fue de 550 MHz.

Procesador AMD K5Bajo la marca K5, se produjeron dos versiones de los procesadores SSA / 5 y 5k86. El primero funcionó a frecuencias de 75 MHz a 100 MHz. El procesador 5k86 funcionaba a frecuencias de 90 MHz a 133 MHz.En 1997, la compañía introdujo el procesador K6, cuya arquitectura era significativamente diferente del K5. Los procesadores se fabricaron utilizando una tecnología de proceso de 350 nanómetros, incluyeron 8,8 millones de transistores, admitieron un cambio en el orden de las instrucciones, un conjunto de instrucciones MMX y un bloque de punto flotante. El área del cristal era de 162 mm². El caché del primer nivel totalizó 64 Kb (32 Kb de datos y 32 Kb de instrucciones). El procesador funcionaba a una frecuencia de 166 MHz, 200 MHz y 233 MHz. La frecuencia del bus del sistema fue de 66 MHz.En 1998, AMD lanzó chips con una arquitectura K6-2 mejorada, con 9.3 millones de transistores fabricados utilizando una tecnología de proceso de 250 nanómetros. La frecuencia máxima del chip fue de 550 MHz. Procesador AMD K6En 1999, se lanzó la tercera generación: la arquitectura K6-III. El cristal retuvo todas las características del K6-2, pero al mismo tiempo apareció un caché incorporado del segundo nivel con una capacidad de 256 KB. El volumen del caché de primer nivel fue de 64 Kb.Procesadores AMD K7En el mismo 1999, K6 fue reemplazado por procesadores K7. Fueron producidos utilizando tecnología de 250 nm con 22 millones de transistores. La CPU tenía una nueva unidad entera (ALU). El bus del sistema EV6 proporcionó la transmisión de datos en ambos bordes de la señal del reloj, lo que permitió obtener una frecuencia efectiva de 200 MHz a una frecuencia física de 100 MHz. El caché del primer nivel fue de 128 Kb (64 Kb de instrucciones y 64 Kb de datos). El segundo nivel de caché alcanzó 512 Kb.

Procesador AMD K6En 1999, se lanzó la tercera generación: la arquitectura K6-III. El cristal retuvo todas las características del K6-2, pero al mismo tiempo apareció un caché incorporado del segundo nivel con una capacidad de 256 KB. El volumen del caché de primer nivel fue de 64 Kb.Procesadores AMD K7En el mismo 1999, K6 fue reemplazado por procesadores K7. Fueron producidos utilizando tecnología de 250 nm con 22 millones de transistores. La CPU tenía una nueva unidad entera (ALU). El bus del sistema EV6 proporcionó la transmisión de datos en ambos bordes de la señal del reloj, lo que permitió obtener una frecuencia efectiva de 200 MHz a una frecuencia física de 100 MHz. El caché del primer nivel fue de 128 Kb (64 Kb de instrucciones y 64 Kb de datos). El segundo nivel de caché alcanzó 512 Kb. Procesador AMD K7Un poco más tarde, aparecieron cristales basados en el núcleo de Orión. Fueron producidos de acuerdo con la tecnología de proceso de 180 nm.La versión del núcleo Thunderbird introdujo cambios inusuales en los procesadores. El caché del segundo nivel se transfirió directamente al núcleo del procesador y funcionó con la misma frecuencia. El caché tenía una capacidad efectiva de 384 KB (128 KB de caché en el primer nivel y 256 KB de caché en el segundo nivel). La frecuencia de reloj del bus del sistema ha aumentado; ahora funcionaba con una frecuencia de 133 MHz.Procesadores Intel P6La arquitectura P6 reemplazó a la P5 en 1995. El procesador era superescalar y admitía cambios en el orden de las operaciones. Los procesadores utilizaron un bus dual independiente, que aumentó significativamente el ancho de banda de la memoria.En el mismo 1995, se introdujeron los procesadores Pentium Pro de próxima generación. Los cristales trabajaron a una frecuencia de 150 MHz - 200 MHz, tenían 16 KB de caché en el primer nivel y hasta 1 MB de caché en el segundo nivel.

Procesador AMD K7Un poco más tarde, aparecieron cristales basados en el núcleo de Orión. Fueron producidos de acuerdo con la tecnología de proceso de 180 nm.La versión del núcleo Thunderbird introdujo cambios inusuales en los procesadores. El caché del segundo nivel se transfirió directamente al núcleo del procesador y funcionó con la misma frecuencia. El caché tenía una capacidad efectiva de 384 KB (128 KB de caché en el primer nivel y 256 KB de caché en el segundo nivel). La frecuencia de reloj del bus del sistema ha aumentado; ahora funcionaba con una frecuencia de 133 MHz.Procesadores Intel P6La arquitectura P6 reemplazó a la P5 en 1995. El procesador era superescalar y admitía cambios en el orden de las operaciones. Los procesadores utilizaron un bus dual independiente, que aumentó significativamente el ancho de banda de la memoria.En el mismo 1995, se introdujeron los procesadores Pentium Pro de próxima generación. Los cristales trabajaron a una frecuencia de 150 MHz - 200 MHz, tenían 16 KB de caché en el primer nivel y hasta 1 MB de caché en el segundo nivel. Procesador Intel Pentium ProEn 1999, se introdujeron los primeros procesadores Pentium III. Se basaron en una nueva generación del núcleo P6 llamada Katmai, que eran versiones modificadas de Deschutes. Se agregó soporte para las instrucciones SSE al núcleo, y se mejoró el mecanismo para trabajar con la memoria. La frecuencia de reloj de los procesadores Katmai alcanzó 600 MHz.En 2000, se lanzaron los primeros procesadores Pentium 4 con un núcleo Willamette. La frecuencia efectiva del bus del sistema fue de 400 MHz (frecuencia física - 100 MHz). El caché del primer nivel alcanzó un volumen de 8 KB, y el caché del segundo nivel alcanzó los 256 KB.El siguiente núcleo de la línea fue Northwood (2002). Los procesadores contenían 55 millones de transistores y se fabricaron utilizando la nueva tecnología CMOS de 130 nm con compuestos de cobre. La frecuencia del bus del sistema era de 400 MHz, 533 MHz u 800 MHz.

Procesador Intel Pentium ProEn 1999, se introdujeron los primeros procesadores Pentium III. Se basaron en una nueva generación del núcleo P6 llamada Katmai, que eran versiones modificadas de Deschutes. Se agregó soporte para las instrucciones SSE al núcleo, y se mejoró el mecanismo para trabajar con la memoria. La frecuencia de reloj de los procesadores Katmai alcanzó 600 MHz.En 2000, se lanzaron los primeros procesadores Pentium 4 con un núcleo Willamette. La frecuencia efectiva del bus del sistema fue de 400 MHz (frecuencia física - 100 MHz). El caché del primer nivel alcanzó un volumen de 8 KB, y el caché del segundo nivel alcanzó los 256 KB.El siguiente núcleo de la línea fue Northwood (2002). Los procesadores contenían 55 millones de transistores y se fabricaron utilizando la nueva tecnología CMOS de 130 nm con compuestos de cobre. La frecuencia del bus del sistema era de 400 MHz, 533 MHz u 800 MHz. Intel Pentium 4En 2004, la producción de procesadores se transfirió nuevamente a estándares tecnológicos más sutiles: 90 nm. Pentium 4 en Prescott core lanzado. El caché de los datos del primer nivel aumentó a 16 Kb, y el caché del segundo nivel alcanzó 1 MB. La frecuencia del reloj era de 2,4 GHz - 3,8 GHz, la frecuencia del bus del sistema - 533 MHz u 800 MHz.El último núcleo utilizado en los procesadores Pentium 4 fue el Cedar Mill de un solo núcleo. Producido por una nueva tecnología de proceso: 65 nm. Había cuatro modelos: 631 (3 GHz), 641 (3,2 GHz), 651 (3,4 GHz), 661 (3,6 GHz).Procesadores Athlon 64 y Athlon 64 X2A finales de 2003, AMD lanzó una nueva arquitectura K8 de 64 bits, basada en la tecnología de proceso de 130 nanómetros. El procesador tenía un controlador de memoria integrado y un bus HyperTransport. Ella trabajó a una frecuencia de 200 MHz. Los nuevos productos AMD se llaman Athlon 64. Los procesadores admitieron muchos conjuntos de instrucciones, como MMX, 3DNow!, SSE, SSE2 y SSE3.

Intel Pentium 4En 2004, la producción de procesadores se transfirió nuevamente a estándares tecnológicos más sutiles: 90 nm. Pentium 4 en Prescott core lanzado. El caché de los datos del primer nivel aumentó a 16 Kb, y el caché del segundo nivel alcanzó 1 MB. La frecuencia del reloj era de 2,4 GHz - 3,8 GHz, la frecuencia del bus del sistema - 533 MHz u 800 MHz.El último núcleo utilizado en los procesadores Pentium 4 fue el Cedar Mill de un solo núcleo. Producido por una nueva tecnología de proceso: 65 nm. Había cuatro modelos: 631 (3 GHz), 641 (3,2 GHz), 651 (3,4 GHz), 661 (3,6 GHz).Procesadores Athlon 64 y Athlon 64 X2A finales de 2003, AMD lanzó una nueva arquitectura K8 de 64 bits, basada en la tecnología de proceso de 130 nanómetros. El procesador tenía un controlador de memoria integrado y un bus HyperTransport. Ella trabajó a una frecuencia de 200 MHz. Los nuevos productos AMD se llaman Athlon 64. Los procesadores admitieron muchos conjuntos de instrucciones, como MMX, 3DNow!, SSE, SSE2 y SSE3. Procesador Athlon 64En 2005, los procesadores AMD llamados Athlon 64 X2 ingresaron al mercado. Estos fueron los primeros procesadores de escritorio de doble núcleo. El modelo se basó en dos núcleos hechos en un solo cristal. Tenían un controlador de memoria común, un bus HyperTransport y una cola de comandos.

Procesador Athlon 64En 2005, los procesadores AMD llamados Athlon 64 X2 ingresaron al mercado. Estos fueron los primeros procesadores de escritorio de doble núcleo. El modelo se basó en dos núcleos hechos en un solo cristal. Tenían un controlador de memoria común, un bus HyperTransport y una cola de comandos. Procesador Athlon 64 X2Durante 2005 y 2006, AMD lanzó cuatro generaciones de chips de doble núcleo: tres núcleos Manchester de 90 nm, Toledo y Windsor, así como un núcleo Brisbane de 65 nm. Los procesadores diferían en el tamaño de caché del segundo nivel y el consumo de energía.Procesadores Intel Core Losprocesadores Pentium M proporcionan más rendimiento que los procesadores de escritorio basados en la microarquitectura NetBurst. Y, por lo tanto, sus decisiones arquitectónicas se convirtieron en la base de la microarquitectura Core, que se lanzó en 2006. El primer procesador de cuatro núcleos de escritorio fue el Intel Core 2 Extreme QX6700 con una frecuencia de reloj de 2,67 GHz y 8 MB de caché en el segundo nivel.El nombre en clave de la primera generación de procesadores móviles de Intel fue Yonah. Fueron fabricados utilizando la tecnología de proceso de 65 nm, basada en la arquitectura Banias / Dothan Pentium M, con la incorporación de la tecnología de protección LaGrande. El procesador podría procesar hasta cuatro instrucciones por ciclo de reloj. Core ha rediseñado el algoritmo para procesar instrucciones de 128 bits SSE, SSE2 y SSE3. Si antes se procesaba cada comando en dos medidas, ahora solo se requería una medida para la operación.

Procesador Athlon 64 X2Durante 2005 y 2006, AMD lanzó cuatro generaciones de chips de doble núcleo: tres núcleos Manchester de 90 nm, Toledo y Windsor, así como un núcleo Brisbane de 65 nm. Los procesadores diferían en el tamaño de caché del segundo nivel y el consumo de energía.Procesadores Intel Core Losprocesadores Pentium M proporcionan más rendimiento que los procesadores de escritorio basados en la microarquitectura NetBurst. Y, por lo tanto, sus decisiones arquitectónicas se convirtieron en la base de la microarquitectura Core, que se lanzó en 2006. El primer procesador de cuatro núcleos de escritorio fue el Intel Core 2 Extreme QX6700 con una frecuencia de reloj de 2,67 GHz y 8 MB de caché en el segundo nivel.El nombre en clave de la primera generación de procesadores móviles de Intel fue Yonah. Fueron fabricados utilizando la tecnología de proceso de 65 nm, basada en la arquitectura Banias / Dothan Pentium M, con la incorporación de la tecnología de protección LaGrande. El procesador podría procesar hasta cuatro instrucciones por ciclo de reloj. Core ha rediseñado el algoritmo para procesar instrucciones de 128 bits SSE, SSE2 y SSE3. Si antes se procesaba cada comando en dos medidas, ahora solo se requería una medida para la operación. Intel Core 2 Extreme QX6700En 2007, salió la microarquitectura Penryn de 45 nm con puertas de metal Hi-k sin plomo. La tecnología se utilizó en la familia de procesadores Intel Core 2 Duo. Se agregó soporte para las instrucciones SSE4 a la arquitectura, y la cantidad máxima de caché en el segundo nivel de procesadores de doble núcleo aumentó de 4 MB a 6 MB.

Intel Core 2 Extreme QX6700En 2007, salió la microarquitectura Penryn de 45 nm con puertas de metal Hi-k sin plomo. La tecnología se utilizó en la familia de procesadores Intel Core 2 Duo. Se agregó soporte para las instrucciones SSE4 a la arquitectura, y la cantidad máxima de caché en el segundo nivel de procesadores de doble núcleo aumentó de 4 MB a 6 MB. Procesador AMD Phenom II X6En 2008, se lanzó la arquitectura de próxima generación, Nehalem. Los procesadores adquirieron un controlador de memoria integrado que admite 2 o 3 canales de DDR3 SDRAM o 4 canales de FB-DIMM. En lugar del bus FSB, llegó un nuevo bus QPI. El caché de nivel 2 se redujo a 256 KB por núcleo.

Procesador AMD Phenom II X6En 2008, se lanzó la arquitectura de próxima generación, Nehalem. Los procesadores adquirieron un controlador de memoria integrado que admite 2 o 3 canales de DDR3 SDRAM o 4 canales de FB-DIMM. En lugar del bus FSB, llegó un nuevo bus QPI. El caché de nivel 2 se redujo a 256 KB por núcleo. Intel Core i7Pronto, Intel trasladó la arquitectura Nehalem a una nueva tecnología de proceso de 32 nm. Esta línea de procesadores se llama Westmere.El primer modelo de la nueva microarquitectura fue Clarkdale, que tiene dos núcleos y un núcleo gráfico integrado, producido por la tecnología de proceso de 45 nm.Procesadores AMD K10 Lacompañía AMD trató de mantenerse al día con Intel. En 2007, lanzó la generación de arquitectura de microprocesador x86 - K10. Se combinaron cuatro núcleos de procesador en un chip. Además del caché de los niveles 1 y 2, los modelos K10 finalmente obtuvieron L3 de 2 MB. El caché de datos e instrucciones del primer nivel fue de 64 Kb cada uno, y el caché del segundo nivel fue de 512 Kb. También hay un prometedor soporte para el controlador de memoria DDR3. K10 usó dos controladores de 64 bits. Cada núcleo del procesador tenía un módulo de coma flotante de 128 bits. Además de eso, los nuevos procesadores funcionaron a través de la interfaz HyperTransport 3.0.En 2007, las CPU multinúcleo Phenom de AMD para PC de escritorio se lanzaron con la arquitectura K10. Las soluciones basadas en K10 se produjeron utilizando tecnología de proceso de 65 y 45 nm. En la nueva versión de la arquitectura (K10.5), el controlador de memoria funcionaba con memoria DDR2 y DDR3.

Intel Core i7Pronto, Intel trasladó la arquitectura Nehalem a una nueva tecnología de proceso de 32 nm. Esta línea de procesadores se llama Westmere.El primer modelo de la nueva microarquitectura fue Clarkdale, que tiene dos núcleos y un núcleo gráfico integrado, producido por la tecnología de proceso de 45 nm.Procesadores AMD K10 Lacompañía AMD trató de mantenerse al día con Intel. En 2007, lanzó la generación de arquitectura de microprocesador x86 - K10. Se combinaron cuatro núcleos de procesador en un chip. Además del caché de los niveles 1 y 2, los modelos K10 finalmente obtuvieron L3 de 2 MB. El caché de datos e instrucciones del primer nivel fue de 64 Kb cada uno, y el caché del segundo nivel fue de 512 Kb. También hay un prometedor soporte para el controlador de memoria DDR3. K10 usó dos controladores de 64 bits. Cada núcleo del procesador tenía un módulo de coma flotante de 128 bits. Además de eso, los nuevos procesadores funcionaron a través de la interfaz HyperTransport 3.0.En 2007, las CPU multinúcleo Phenom de AMD para PC de escritorio se lanzaron con la arquitectura K10. Las soluciones basadas en K10 se produjeron utilizando tecnología de proceso de 65 y 45 nm. En la nueva versión de la arquitectura (K10.5), el controlador de memoria funcionaba con memoria DDR2 y DDR3. Procesador AMD PhenomEn 2011, se lanzó la nueva arquitectura Bulldozer. Cada módulo contenía dos núcleos con su propio bloque de enteros y caché de nivel 1. Memoria caché compatible del 3er nivel de 8 MB, buses HyperTransport 3.1, tecnologías para aumentar la frecuencia de los núcleos Turbo Core de segunda generación y conjuntos de instrucciones AVX, SSE 4.1, SSE 4.2, AES. Los procesadores Bulldozer también estaban dotados de un controlador de memoria DDR3 de doble canal con una frecuencia efectiva de 1866 MHz.

Procesador AMD PhenomEn 2011, se lanzó la nueva arquitectura Bulldozer. Cada módulo contenía dos núcleos con su propio bloque de enteros y caché de nivel 1. Memoria caché compatible del 3er nivel de 8 MB, buses HyperTransport 3.1, tecnologías para aumentar la frecuencia de los núcleos Turbo Core de segunda generación y conjuntos de instrucciones AVX, SSE 4.1, SSE 4.2, AES. Los procesadores Bulldozer también estaban dotados de un controlador de memoria DDR3 de doble canal con una frecuencia efectiva de 1866 MHz. Procesador AMD BulldozerEn 2013, la compañía presentó la próxima generación de procesadores: Piledriver. Este modelo fue una arquitectura mejorada de Bulldozer. Los bloques de predicción de rama se han refinado, y el rendimiento del módulo de computación de punto flotante y entero ha aumentado, así como la velocidad del reloj.Mirando a través de la historia, puede rastrear las etapas de desarrollo de los procesadores, los cambios en su arquitectura, la mejora de las tecnologías de desarrollo y mucho más. Las CPU modernas son diferentes de las que salieron antes, pero al mismo tiempo tienen características comunes.

Procesador AMD BulldozerEn 2013, la compañía presentó la próxima generación de procesadores: Piledriver. Este modelo fue una arquitectura mejorada de Bulldozer. Los bloques de predicción de rama se han refinado, y el rendimiento del módulo de computación de punto flotante y entero ha aumentado, así como la velocidad del reloj.Mirando a través de la historia, puede rastrear las etapas de desarrollo de los procesadores, los cambios en su arquitectura, la mejora de las tecnologías de desarrollo y mucho más. Las CPU modernas son diferentes de las que salieron antes, pero al mismo tiempo tienen características comunes. Source: https://habr.com/ru/post/es392175/

All Articles