Investigadores de Intel y la Universidad de Carolina del Norte aceleran el intercambio de datos entre núcleos de CPU de 2 a 12 veces

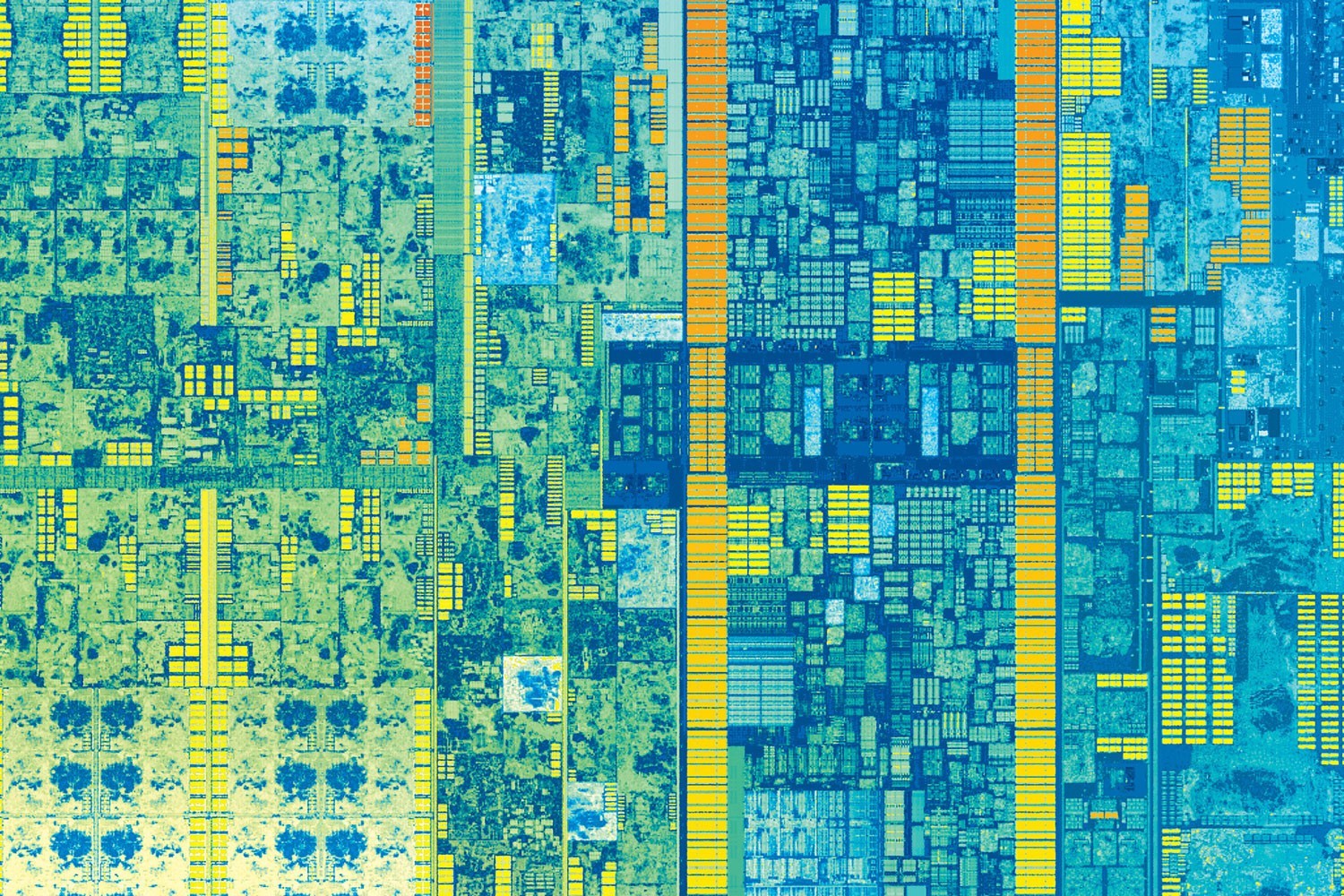

La topología de la séptima generación de procesadores Intel Core (anteriormente con nombre en código Kaby Lake), que estará disponible a finales de 2016. Foto: IntelUn grupo de investigadores de la Universidad de Carolina del Norte e Intel han desarrollado la tecnología CAF (Core to Core Communication Acceleration Framework) , que puede acelerar significativamente el intercambio de datos entre núcleos de procesador. Al eliminar este cuello de botella, los fabricantes finalmente podrán aumentar el número de núcleos en la CPU sin un aumento exponencial en el tráfico de servicio entre ellos.En la implementación de programas paralelos, lo más difícil es garantizar la correcta coordinación de los recursos compartidos entre los procesos. En los procesadores modernos, la sincronización de la interacción paralela entre los núcleos se lleva a cabo mediante dos métodos: el paso de mensajes y la memoria compartida.En el primer caso, se inicia un proceso de subproceso único en cada núcleo, que intercambia datos con otros procesos que se ejecutan en otros núcleos.Al interactuar a través de la memoria compartida en cada procesador de un sistema multiprocesador, se inicia el hilo de ejecución que pertenece a un proceso. Las secuencias intercambian datos a través de una porción de memoria común a este proceso. El número de subprocesos corresponde al número de procesadores.Los investigadores proponen implementar tal coordinación de recursosa nivel de hardware . En un resumen del trabajo científico preparado, señalan que "la interacción a través de la memoria compartida por naturaleza implica discapacidad para mantener la coherencia y las fallas de caché, lo que aumenta en gran medida la sobrecarga y crea una gran cantidad de tráfico de red [en exceso]".Muchas tareas importantes requieren un gran intercambio de tráfico entre los núcleos, por lo que un aumento significativo en los gastos generales supone un gran éxito en el rendimiento. Esto también se aplica al rendimiento de la tubería informática, que se usa ampliamente en soluciones de software para el paralelismo operativo a nivel de comando.La aceleración de hardware coordina el trabajo de los núcleos en la computación paralela. La coordinación de núcleo de hardware propuesta es mucho más eficiente que cualquier método de sincronización de software que esté actualmente en uso."Este enfoque, que llamamos el Marco de CAF para acelerar la comunicación entre núcleos , mejora la transferencia de datos de 2 a 12 veces", dijo Yan Solihin, profesor de ingeniería eléctrica e informática en la Universidad de Carolina del Norte y coautor de la investigación. "En otras palabras, la velocidad de ejecución, de principio a fin, es al menos dos veces más rápida".En el trabajo científico preparado, los autores realizaron un análisis de la sobrecarga (tráfico de red excesivo entre los núcleos), que ocurre al sincronizar cálculos paralelos con métodos de software existentes. Y propusieron una solución alternativa.Un elemento clave del nuevo marco es el módulo de hardware de gestión de colas del Dispositivo de gestión de colas (QMD). Es capaz de realizar funciones computacionales simples y está conectado por hardware al subsistema de comunicación, es decir, a NoC (una red en un chip, una mini Internet dentro del procesador ).

La topología de la séptima generación de procesadores Intel Core (anteriormente con nombre en código Kaby Lake), que estará disponible a finales de 2016. Foto: IntelUn grupo de investigadores de la Universidad de Carolina del Norte e Intel han desarrollado la tecnología CAF (Core to Core Communication Acceleration Framework) , que puede acelerar significativamente el intercambio de datos entre núcleos de procesador. Al eliminar este cuello de botella, los fabricantes finalmente podrán aumentar el número de núcleos en la CPU sin un aumento exponencial en el tráfico de servicio entre ellos.En la implementación de programas paralelos, lo más difícil es garantizar la correcta coordinación de los recursos compartidos entre los procesos. En los procesadores modernos, la sincronización de la interacción paralela entre los núcleos se lleva a cabo mediante dos métodos: el paso de mensajes y la memoria compartida.En el primer caso, se inicia un proceso de subproceso único en cada núcleo, que intercambia datos con otros procesos que se ejecutan en otros núcleos.Al interactuar a través de la memoria compartida en cada procesador de un sistema multiprocesador, se inicia el hilo de ejecución que pertenece a un proceso. Las secuencias intercambian datos a través de una porción de memoria común a este proceso. El número de subprocesos corresponde al número de procesadores.Los investigadores proponen implementar tal coordinación de recursosa nivel de hardware . En un resumen del trabajo científico preparado, señalan que "la interacción a través de la memoria compartida por naturaleza implica discapacidad para mantener la coherencia y las fallas de caché, lo que aumenta en gran medida la sobrecarga y crea una gran cantidad de tráfico de red [en exceso]".Muchas tareas importantes requieren un gran intercambio de tráfico entre los núcleos, por lo que un aumento significativo en los gastos generales supone un gran éxito en el rendimiento. Esto también se aplica al rendimiento de la tubería informática, que se usa ampliamente en soluciones de software para el paralelismo operativo a nivel de comando.La aceleración de hardware coordina el trabajo de los núcleos en la computación paralela. La coordinación de núcleo de hardware propuesta es mucho más eficiente que cualquier método de sincronización de software que esté actualmente en uso."Este enfoque, que llamamos el Marco de CAF para acelerar la comunicación entre núcleos , mejora la transferencia de datos de 2 a 12 veces", dijo Yan Solihin, profesor de ingeniería eléctrica e informática en la Universidad de Carolina del Norte y coautor de la investigación. "En otras palabras, la velocidad de ejecución, de principio a fin, es al menos dos veces más rápida".En el trabajo científico preparado, los autores realizaron un análisis de la sobrecarga (tráfico de red excesivo entre los núcleos), que ocurre al sincronizar cálculos paralelos con métodos de software existentes. Y propusieron una solución alternativa.Un elemento clave del nuevo marco es el módulo de hardware de gestión de colas del Dispositivo de gestión de colas (QMD). Es capaz de realizar funciones computacionales simples y está conectado por hardware al subsistema de comunicación, es decir, a NoC (una red en un chip, una mini Internet dentro del procesador ). Ilustración del artículo " Red en un chip - mini-Internet dentro del procesador "El módulo QMD asume la tarea de administrar la cola y sincronizar la interacción paralela de los núcleos, sin instrucciones de software adicionales en los núcleos de la CPU. Es como un enrutador de hardware en una red.El desarrollo futuro es importante a la luz del aumento constante de núcleos en los procesadores modernos. Este es un proceso completamente natural, ya que la velocidad del reloj casi se ha detenido debido a limitaciones físicas naturales. Los fabricantes no tienen más remedio que paralelizar los cálculos.En tales condiciones, la sincronización de la interacción paralela entre los núcleos se convierte en el cuello de botella que limita el rendimiento del sistema. Con un enrutamiento de tráfico eficiente entre los núcleos del procesador, puede continuar escalando la arquitectura de la CPU y crear procesadores con decenas o cientos de núcleos con una escala de rendimiento casi lineal. El enrutamiento eficiente del tráfico entre núcleos es una tecnología clave que se necesita para escalar aún más la arquitectura de CPU de múltiples núcleos.Además de acelerar repetidamente el intercambio de datos entre núcleos mientras se sincroniza la computación paralela, el módulo QMD puede ser útil para agregar datos de múltiples núcleos. Los investigadores creen que acelerará el procesamiento de algunas operaciones informáticas básicas hasta en un 15%.El trabajo científico " CAF: Core to Core Communication Acceleration Framework " se presentará en la 25ª conferencia sobre arquitecturas paralelas y métodos de compilación PACT '16 , que se celebrará del 11 al 15 de septiembre de 2016 en Haifa (Israel).Los inventores son Yipeng Wang (Universidad de Carolina del Norte), Ren Wang, Andrew Herdrich y James Tsai (todos Intel Corp.), y el autor principal del artículo es el mencionado anteriormente. Yan Solihin de la Universidad de Carolina del Norte y la Fundación Nacional de Ciencias de EE. UU.El artículo se incluyó en las Actas de la Conferencia Internacional de 2016 sobre arquitecturas paralelas y compilación, p. 351-362, doi: 10.1145 / 2967938.2967954. Es probable que la recopilación de informes se distribuya a los participantes de la conferencia y se publique en Internet.

Ilustración del artículo " Red en un chip - mini-Internet dentro del procesador "El módulo QMD asume la tarea de administrar la cola y sincronizar la interacción paralela de los núcleos, sin instrucciones de software adicionales en los núcleos de la CPU. Es como un enrutador de hardware en una red.El desarrollo futuro es importante a la luz del aumento constante de núcleos en los procesadores modernos. Este es un proceso completamente natural, ya que la velocidad del reloj casi se ha detenido debido a limitaciones físicas naturales. Los fabricantes no tienen más remedio que paralelizar los cálculos.En tales condiciones, la sincronización de la interacción paralela entre los núcleos se convierte en el cuello de botella que limita el rendimiento del sistema. Con un enrutamiento de tráfico eficiente entre los núcleos del procesador, puede continuar escalando la arquitectura de la CPU y crear procesadores con decenas o cientos de núcleos con una escala de rendimiento casi lineal. El enrutamiento eficiente del tráfico entre núcleos es una tecnología clave que se necesita para escalar aún más la arquitectura de CPU de múltiples núcleos.Además de acelerar repetidamente el intercambio de datos entre núcleos mientras se sincroniza la computación paralela, el módulo QMD puede ser útil para agregar datos de múltiples núcleos. Los investigadores creen que acelerará el procesamiento de algunas operaciones informáticas básicas hasta en un 15%.El trabajo científico " CAF: Core to Core Communication Acceleration Framework " se presentará en la 25ª conferencia sobre arquitecturas paralelas y métodos de compilación PACT '16 , que se celebrará del 11 al 15 de septiembre de 2016 en Haifa (Israel).Los inventores son Yipeng Wang (Universidad de Carolina del Norte), Ren Wang, Andrew Herdrich y James Tsai (todos Intel Corp.), y el autor principal del artículo es el mencionado anteriormente. Yan Solihin de la Universidad de Carolina del Norte y la Fundación Nacional de Ciencias de EE. UU.El artículo se incluyó en las Actas de la Conferencia Internacional de 2016 sobre arquitecturas paralelas y compilación, p. 351-362, doi: 10.1145 / 2967938.2967954. Es probable que la recopilación de informes se distribuya a los participantes de la conferencia y se publique en Internet.Source: https://habr.com/ru/post/es397275/

All Articles