En cada artículo sobre Habré dedicado a los microprocesadores domésticos, de una forma u otra, se plantea el tema de los bloques de IP con licencia y cuánto se reduce su presencia y ausencia en el valor, la seguridad doméstica o la seguridad del desarrollo. Al mismo tiempo, muchos comentaristas no entienden muy bien el tema de discusión, así que tratemos de averiguar cómo funcionan las licencias en la industria microelectrónica, qué son los bloques con licencia buenos y malos, y cuál es el proceso de desarrollo de un microcircuito si la mayoría de los bloques se compran en él.

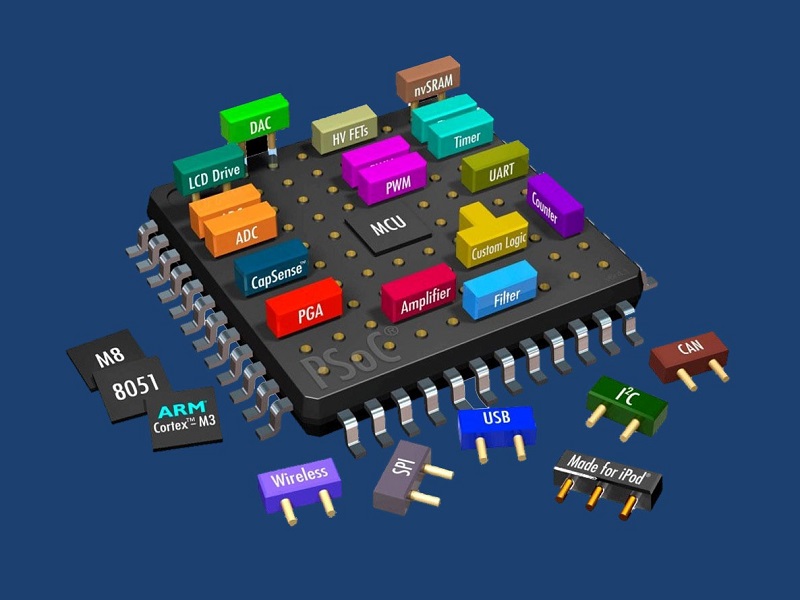

Cualquier microcircuito moderno es lo que orgullosamente se llamó "un sistema en un chip" hace algún tiempo: incluso los reguladores lineales de tres patas y las fuentes de voltaje tienen un ajuste digital oculto para el usuario, ¿qué podemos decir sobre los microprocesadores y microcontroladores que contienen docenas de bloques diferentes, el desarrollo de cada uno? de los cuales requiere habilidades específicas y una amplia experiencia para sortear las trampas que no se escriben en libros y artículos. Además, cualquier proyecto, por regla general, tiene su propia característica asesina, debido a que los desarrolladores esperan obtener una ventaja sobre sus competidores, y es esta característica asesina la que se debe hacer lo mejor posible, y todos los demás bloques simplemente no deberían ser peores que otros.

Atención, la pregunta es: ¿es necesario mantener un equipo de desarrollo costoso que pueda hacer de forma independiente todos los bloques necesarios por sí solo?

Una pregunta aún más interesante: si usted mismo ha desarrollado un sistema de instrucciones de microprocesador, ¿necesita contar con un equipo de programadores que

escribirá un compilador para él , portará nuevos núcleos de sistemas operativos populares, hará mucho trabajo duro y probablemente no pondrá su creación en uno? nivel con arquitecturas populares, ¿en qué trabaja mucha más gente?

Y lo más importante: ¿las respuestas positivas a las dos preguntas anteriores le darán ventajas competitivas a su producto?

Digresión líricaEl 5 de junio, Morris Chang se retiró, un hombre del que nunca había oído hablar, pero sin el cual no habría electrónica moderna. Morris Chang nació en China, en el apogeo de la guerra civil que dejó para los Estados Unidos, se graduó del MIT y luego trabajó durante muchos años en Texas Instruments e General Instruments. En esos años, una parte integral de cualquier empresa microelectrónica era su propia producción, cuyo equipo era de varios órdenes de magnitud más barato que ahora, pero no obstante, era muy costoso. Así es como el mismo Chang escribió al respecto:

Cuando estaba en TI e Instrumento General, vi a muchos diseñadores de circuitos integrados que querían irse y establecer su propio negocio, pero lo único, o lo más importante que les impidió abandonar esas compañías fue que no podían recaudar suficiente dinero. para formar su propia empresa. Porque en ese momento se pensaba que todas las empresas necesitaban fabricación, fabricación de obleas, y esa era la parte más intensiva en capital de una empresa de semiconductores, de una empresa de CI. Y vi a todas esas personas que querían irse, pero detenidas por la falta de capacidad para recaudar mucho dinero para construir una oblea fabulosa.

En 1985, Morris Chang estaba a punto de retirarse, pero en su lugar aceptó la oferta del gobierno taiwanés de trabajar en el Instituto de Investigación de Tecnología Industrial, un instituto de investigación que se suponía que ayudaría a provocar una revolución industrial en Taiwán y cerrar la brecha entre la economía desarrollada y los países desarrollados. En 1987, en paralelo con su trabajo en ITRI, Chang creó TSMC, una compañía que se convirtió en el mayor fabricante de circuitos integrados del mundo. El modelo de negocio TSMC se basó originalmente en el hecho de que la empresa no desarrolla nada, sino que solo produce desarrollos de otras personas, y este fue uno de los primeros pasos para crear un ecosistema moderno para el desarrollo y la producción de microcircuitos, conocido como el modelo Fabless.

El fin de la digresión lírica¿Qué es Fabless?

Fabless es un modelo para el desarrollo y la producción de microcircuitos en el que la empresa desarrolladora no tiene su propia producción y utiliza los servicios de una fábrica de terceros que también colabora con otros desarrolladores (y a veces tiene sus propios productos).

La presencia de fábricas de terceros puede reducir radicalmente el umbral para ingresar al mercado de microelectrónica (que Morris Chang había soñado alguna vez), de cientos a millones de dólares, debido a la ausencia de la necesidad de comprar y mantener equipos para la producción. También le permite reducir este umbral aún más debido a la formación de un mercado para proveedores de bloques funcionales complejos (también son Silicon IP). Si produce chips en su propia fábrica, solo puede confiar en sus propias fortalezas y debe contener un equipo que pueda crear todos los bloques necesarios. Si la fábrica es utilizada no solo por usted, sino también por otras empresas, entonces alguien ya ha resuelto la mayoría de las tareas típicas antes que usted, y puede usar los resultados del trabajo de otra persona, o revender su propia solución a otra persona, habiendo acordado previamente el precio y las condiciones para que nadie se quedó en el perdedor. Por supuesto, es poco probable que vendas tus conocimientos para dirigir a los competidores, pero hay muchas situaciones en las que puedes ganar sin involucrarte en un conflicto de intereses. Estaba fuera de la posibilidad y el deseo de reutilizar los resultados de la solución de los problemas típicos que surgió el mercado de bloques de IP, cuyo tamaño a partir de 2017 era cercano a los cuatro mil millones de dólares y continúa creciendo rápidamente.

¿Cómo es rentable?

IP del comprador : principalmente ahorro. Según diversas estimaciones, la compra de bloques de IP suele ser de dos a cinco veces más barata que el autodesarrollo. Además, la compra generalmente le permite reducir significativamente el tiempo de desarrollo, ya que no necesita producir chips de prueba de forma independiente y corregir errores.

Para el desarrollador de IP : la oportunidad de construir un negocio que funcione en una solución de nicho y reducir significativamente el costo de hacer negocios. Una parte importante del costo del microcircuito es el costo de comercialización, empaque, pruebas, soporte técnico, software de aplicación y, finalmente, plantillas de fotos para producción en masa, etc. etc. Si no produce productos terminados, pero solo vende bloques, entonces no tiene todos estos gastos.

Fábrica : una oportunidad para atraer a más clientes. Las grandes fábricas se esfuerzan por crear un ecosistema de proveedores de bloques de IP a su alrededor, porque su uso puede acelerar significativamente el diseño y, lo que es más importante, automatizarlo tanto como sea posible. Una amplia cartera de componentes listos para usar es una gran ayuda en el diseño del producto final, ya que le permite hacer solo lo que sabe por su cuenta y no gastar recursos valiosos en desarrollar todo en general, especialmente en una situación en la que ya existe una solución preparada desarrollada por personas quien invirtió en su desarrollo significativamente más tiempo y experiencia de lo que puede pagar. En consecuencia, una amplia selección de IP preparadas puede ser un factor importante en la elección de una fábrica en particular para la producción de su proyecto.

Como funciona

Veamos la licencia de núcleos utilizando el ejemplo de un sistema esférico personalizado en un chip. El sistema contendrá un núcleo de procesador, buses para combinar el núcleo y los periféricos, una cierta cantidad de memoria caché, interfaces para comunicarse con el mundo exterior (por ejemplo, CAN e I2C), PLL, DAC y ADC. Para la pureza del experimento, supongamos que todo se comprará, sin un desarrollo independiente. "Estúpida suposición", dices, y no tendrás toda la razón. En realidad, por supuesto, tales situaciones son extremadamente raras, pero aún es posible imaginar que la característica asesina del producto no será un bloque en sí mismo, sino una combinación específica de bloques existentes. Por ejemplo, usted es el primer comprador de un bloque (por lo tanto, los competidores aún no lo tienen) o se le ocurrió un bloque existente para usar en un segmento que no es característico para él (por lo tanto, los competidores en este segmento no tienen nada similar).

Entonces, comencemos con ...

... no, no desde el núcleo del procesador, sino desde el enlace analógico. Por ejemplo, tome el convertidor analógico a digital (ADC), una unidad típica de la mayoría de los microcontroladores y cualquier otro sistema que maneje datos del mundo exterior.

El ADC es un bloque analógico, lo que significa que sus parámetros dependen seriamente no solo de su circuito, sino también de cómo se implementa exactamente este circuito en un chip. Si tomamos el archivo terminado con la topología de un proceso técnico y lo producimos en otra fábrica con los mismos estándares de diseño, podemos obtener parámetros completamente diferentes (sin mencionar la transferencia a otros estándares de diseño). Sin embargo, la cultura de los "segundos proveedores", conocida desde mediados de siglo, todavía existe; Por ejemplo, la fábrica de Towerjazz ofrece copias de algunos procesos de fabricación de TSMC.

El ADC es un gran ejemplo de un bloqueo de IP duro que está vinculado a un proceso específico. Para comprar una unidad de este tipo, debe saber exactamente en qué tecnología se fabricará su producto final y, como se mencionó anteriormente, la disponibilidad de la Hard IP necesaria puede ser una gran ventaja competitiva para la fábrica.

¿Cómo se entrega Hard IP? Esta es una pregunta interesante, y para responderla es necesario discutir en qué forma se está desarrollando dicho bloque. En el caso de la mayoría de los bloques analógicos, el desarrollo de los circuitos se lleva a cabo a nivel de transistores individuales, es decir, los archivos de salida serán el archivo del circuito eléctrico y el archivo con la topología. Además, las características tanto del esquema como de la topología pueden tener un valor comercial serio, que, por supuesto, no quiero dejar de lado. Y para que el cliente no pueda realizar ingeniería inversa del esquema por topología, la topología generalmente tampoco se transmite, por lo tanto, en el caso habitual, los archivos entregados se ven así:

- En lugar de un circuito eléctrico, el cliente recibe un modelo de comportamiento de alto nivel que no revela las características de implementación. Tal modelo se puede escribir en Verilog-A. Una alternativa es que algunos sistemas CAD (por ejemplo, Cadence Virtuoso) admiten el cifrado de circuitos eléctricos, es decir, el cliente podrá usar su circuito (o el archivo verilog-A), pero no podrá abrir y ver el contenido.

- Diseño dimensional de la topología, con marcadas conclusiones externas y una descripción de cuántos niveles de metalización ocupa un bloque.

- Entorno de prueba para la verificación de los parámetros principales.

- Documentación

En este caso, por supuesto, es necesaria la participación de un tercero, al que puede transferir la topología sin temor a la competencia y la ingeniería inversa. Este tercero es la fábrica, y su papel de intermediario entre clientes y contratistas es una parte importante del ecosistema de desarrollo de chips sin defectos. La fábrica, por supuesto, debe tener una reputación cristalina (se trata de marcadores) e, idealmente, no debe producir nada similar por sí sola, porque trabajar en la fábrica de una empresa competidora es, en cualquier caso, un placer dudoso. Samsung logra producir procesadores al mismo tiempo para Apple y para sí mismo, pero otras grandes fábricas generalmente se concentran en su propia producción (como Intel) o abandonan por completo el autodesarrollo (como TSMC). El deseo de deshacerse de este conflicto de intereses, por cierto, fue uno de los impulsores para asignar Globalfoundries (el segundo jugador más grande en el mercado de fábricas) de AMD.

Digresión líricaPor cierto, en Rusia, no hay fábricas de puro juego en Rusia. Además, para absolutamente todos los actores del mercado, la producción de sus propios productos es una prioridad, y todos los chips totalmente nacionales producidos por desarrolladores sin fábula se fabrican en las instalaciones de sus competidores potenciales, o en fábricas de juego puro en el extranjero.

El fin de la digresión líricaAdemás, hay otro detalle importante de la interacción proveedor-fábrica: la fábrica ingresa su bloque de IP en su propia base de datos y verifica aún más todos los proyectos entrantes por la presencia de su topología (que alguien podría obtener de usted, así como ilegalmente), y Verifique con usted si la persona que solicita la producción tiene una licencia (ya que muchas licencias baratas implican el uso de la unidad en un solo proyecto). La presencia de un cheque por parte de la fábrica permite al desarrollador de Hard IP elegir cualquier opción de licencia conveniente, vinculada a la cantidad de proyectos, la cantidad de chips vendidos, el momento de lanzamiento de los chips en producción, etc. etc. Pero más sobre los tipos de licencias en la siguiente parte.

Al igual que Hard IP en un sistema típico en un chip, necesitará ADC, PLL, capas físicas de interfaces de E / S.

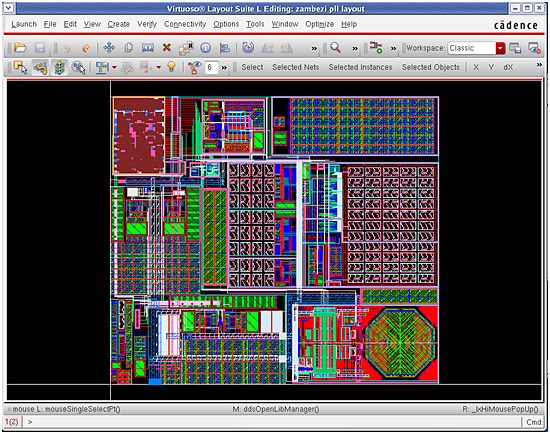

Ventana CAD Cadence Virtuoso Layout Suite con la topología del bloque analógico Hard IP (esto es PLL, si alguien está interesado). Los límites entre las subunidades individuales (que generalmente están hechas por diferentes personas) y, por ejemplo, un elemento muy raro para circuitos integrados: el inductor en la esquina inferior derecha, son claramente visibles. Y en la parte superior izquierda hay un bloque digital (probablemente control) y su interfaz de múltiples bits para el resto.

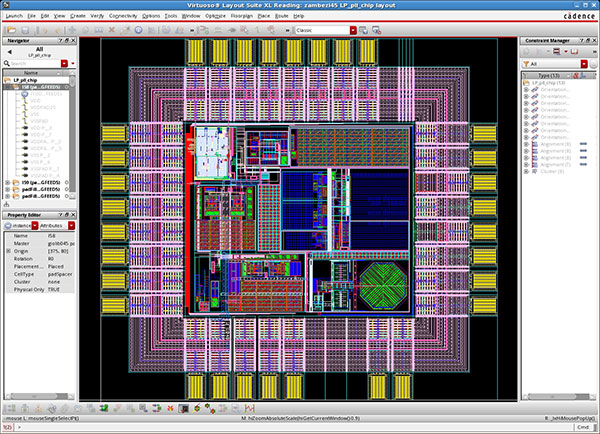

Es lo mismo, pero ya en forma de chip terminado (por ejemplo, para pruebas). Las almohadillas de E / S y los anillos que los conectan desde las tierras y los suministros son claramente visibles.

El término "IP dura" también se utiliza en relación con los bloques de IP para FPGA. En este caso, se entiende que el código de bloque se ha optimizado para su uso en un modelo FPGA particular y se ha sintetizado para su colocación en él.

IP suave

El siguiente bloque que consideraremos es el núcleo del procesador. En realidad, casi cualquier circuito digital puede estar en su lugar, por ejemplo, una unidad de codificación de señal con un código Reed-Solomon, pero los núcleos de los procesadores son más escuchados y representan una buena mitad de todo el mercado (incluso debido a la complejidad y el alto costo).

La principal diferencia entre el desarrollo de circuitos digitales y el desarrollo de circuitos analógicos es que los circuitos digitales generalmente se escriben en lenguajes especiales de alto nivel: Verilog o VHDL, y luego un sistema CAD especial sintetiza el circuito eléctrico y la topología a partir de este código. Entonces, hasta el momento de la síntesis, el código no está vinculado a una tecnología específica, y el mismo bloque se puede producir en diferentes fábricas (o cosido en el FPGA) o en diferentes versiones de la misma tecnología (por ejemplo, optimizado para alta velocidad o bajo consumo de energía) . Esto, de hecho, es utilizado por empresas de desarrollo, como, por ejemplo, ARM. Dichos bloques digitales que no están vinculados a una tecnología específica se denominan Soft IP.

Aquí está el esquema de un bit sumador:

Y así es como se ve realmente un sumador de ocho bits en un diseño de chip:

module adder(

input wire [7:0]a,

input wire [7:0]b,

output wire [7:0]out,

output wire carry

);

assign {carry, out} = a + b;

endmodule

, , , . , IP- .

Soft IP? :

• Clean, readable, synthesizable Verilog HDL, VHDL

• Cadence Encounter RTL Compiler synthesis scripts

• Documentation – integration and user guide, release notes

• Sample verification testbench

Encrypted source along with a complete certification data package (CDP) including all artifacts required for chip-level compliance.

, — , ( IP ). , . , - -, , .

, LEON3:

- , Cobham Gaisler, LEON3 GPL

- LEON3FT ( ): The LEON3FT core is distributed together with a special FT version of the GRLIP IP library, distributed as encrypted RTL.

- ( ) , LEON2FT, .

, , Verilog-, . Verilog- , , , , . digital watermarks, , IP.

, “Clean, readable, synthesizable” , , IP . , , , ( , hardware trojans) , , , .

, : soft IP , , ? , Soft IP, , .. .… :

ARM, , , , , ( ), IP , - , , . . (, , , ). Apple Imagination Technology in-house , Apple , Imagination ( ).

, — ( IP ) ( ).

soft IP FPGA, , . , Xilinx IP, ( ) , , ( , ).

, , .

— IP- . , -, . , IP, , IP , , IP ( , ); , - .

— . , ( IP).

— . , , , . — . , , .

— , , (, ARM Cortex). — , .

— . (, , ) , — ( , , ). ? , ( - , , ) . , , , , , — .

? : , , , . , Apple, ARM - , , (, ARM ) — .

: , , , , , , ( — ). , , . , , Apple, , , ! ARM, , Apple . , ARM . , , Apple — PowerPC, , PowerPC x86, Apple Intel.

Soft IP , - , IP . :

- , “ — ”, .

- - IP ( ), IP, IP ( IP hardening) . ? , , , .

soft IP ( ), , , .. ..

Configurable IP

IP, hard soft — , . - , - . ? , IP-? ?

( , FPGA) , , , . , , IP- Hard IP, Soft IP ( , ).

— -.

Foundation IP

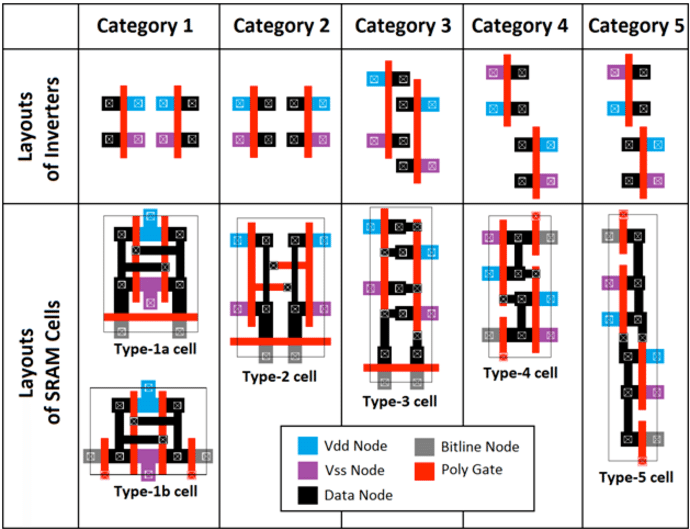

«-hard» IP- — foundation IP, . — , . , , , , , . , , ( ) , (, ) . «generic» , , , , , .

Foundation IP -, , , .

BarsMonster .

Verification IP

, , — , . , , , . , , . , - . “”. .

, — Verification IP. — , , ( ). Synopsys , , Synopsys — IP-. IP Design&Reuse Synopsys 828 Silicon IP ( ARC — ARM) 116 Verification IP .

verification IP CAN, ( APB AHB ARM) - . , , , .

?

, , , , ? .

:

- , ( verification IP ).

- — .

- ( , ).

- Soft IP , .

- , , .

- , , .

- , .

- , ( ).

, , ( ). , - , « - BGA 400-700 ». , Hard IP- 400-700 , , , 4-8 (, Soft IP). — ? , . , «-» .

— Synopsys IC Compiler , .

, — , , , , , , .

, , fabless- IP- , , , . , , ( “”) , , : , , , , , , - . , , — .

: Open Source?/ Open Source . , - ( ) , - . , , - . , , .

—

Opencores.org, — OpenRISC, ( FPGA), ASIC ( Samsung). Opencores, , - , ( ARM), FPGA. FPGA Proven, — ASIC Proven.

—

RISC-V. ( OpenPOWER OpenSPARC) , - , , ( ).

RISC-V — , MIPS, , , , ( , MIPS). RISC-V Foundation Google, Samsung, NXP, NVIDIA . , , , , OpenPOWER, , , ARM , ARM, , , ( Intel). - . RISC-V (

RISC-V), - , . , ,

RISC-V — Falcon NVIDIA.

: ?OpenCores, IP- ( ) . :

TSMC IP Alliance, IP .

Design&Reuse, IP-, ( ).

ChipEstimate, D&R, .

— ?, , , - .

— “” (), “” ( ), “” “” (211), “Neuromatrix” ( “”), RISC-V (Syntacore), ARM, MIPS, SPARC, MCS96, MCS51, C166, AVR, MSP430.

,

“ ” ( ):

IP-:

: ARM Cortex-M4F, ARM Cortex-M0, ARM946E-S c AMBA, ARM VFP9-S, SPARC v.8 c AMBA. 8- RISC .

IP- (PLL) TSMC, KeyASIC AnalogBits, Sidense Memory, - (eFuse) TSMC, IP- , ROM RAM ..

“ ” , IP- - (-, IP-).

IP? IP- (

“ ”,

“”,

211), . Design&Reuse ChipEstimate “ ” ( ) NTLab. , .