Comenzaré desde lejos. El invierno pasado hice un dispositivo USB con un núcleo alojado en la FPGA. Por supuesto, realmente quería comprobar el ancho de banda real de este bus. Después de todo, en el controlador, hay mucho que hacer. Siempre se puede decir que hay un retraso, o por allá. En el caso de los FPGA, veo un bloque que bombea datos, por lo que me dijo que hay datos en él. Pero configuré que todo se procesó y estoy listo para aceptar una nueva porción (al mismo tiempo, ya recibe datos en el segundo búfer del mismo punto final). Genial, configure la preparación desde la primera medida y vea qué sucede cuando el USB puede "martillar" sin detenerse.

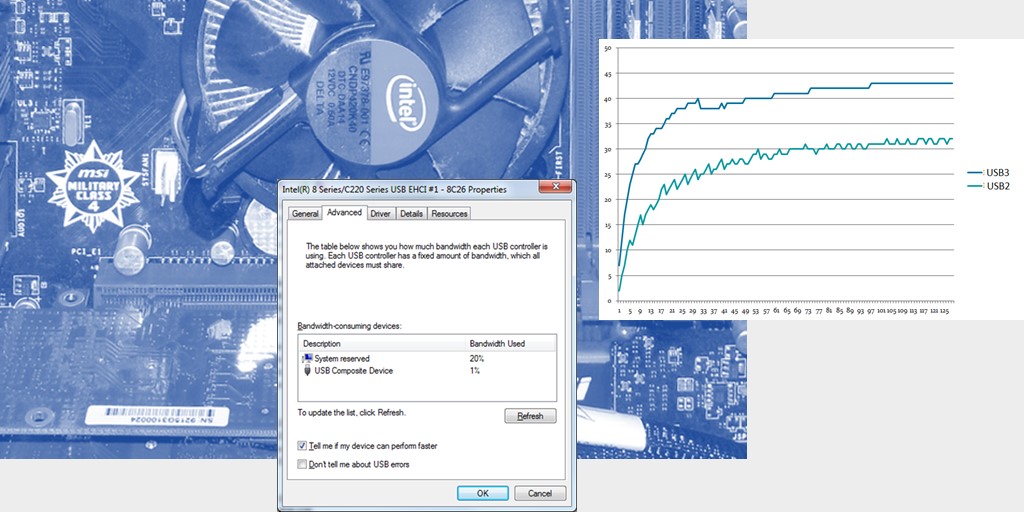

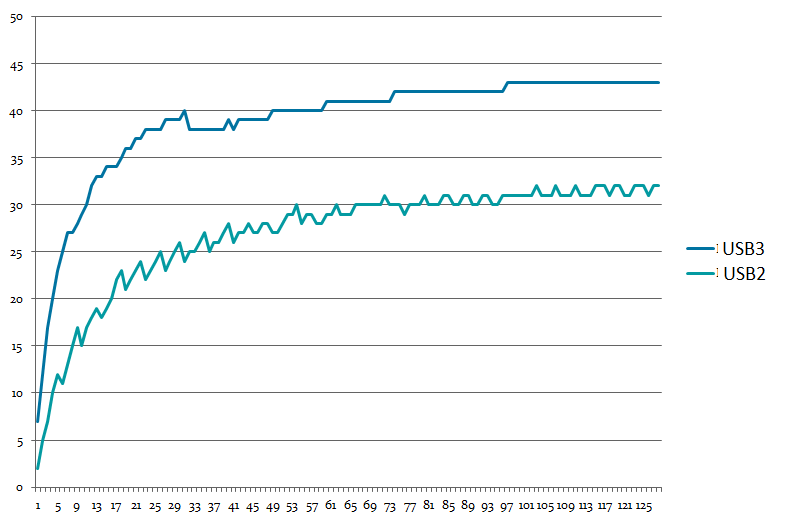

Pero resulta una cosa asombrosa. Si el dispositivo USB 2.0 está atascado en el conector "azul" (que es USB 3.0), entonces la velocidad es una. Si en "negro" - otro. Aquí está mi gráfico de velocidad de grabación USB versus longitud de datos. USB3 y USB2 son el tipo de conector; el dispositivo siempre es USB 2.0 HS.

Lo intenté en diferentes máquinas. El resultado está cerca. Nadie podría explicarme este fenómeno. Más tarde, encontré la razón más probable. Y la razón es muy simple. Estas son las propiedades del controlador USB 2.0:

Los controladores que controlan el conector "azul" no lo hacen. Y la diferencia es solo un 20 por ciento.

De esto concluimos que las limitaciones de ancho de banda no siempre están determinadas por las propiedades físicas del bus. A veces se superponen algunas otras cosas. Pasamos con este conocimiento en estos días.

Experimento primario

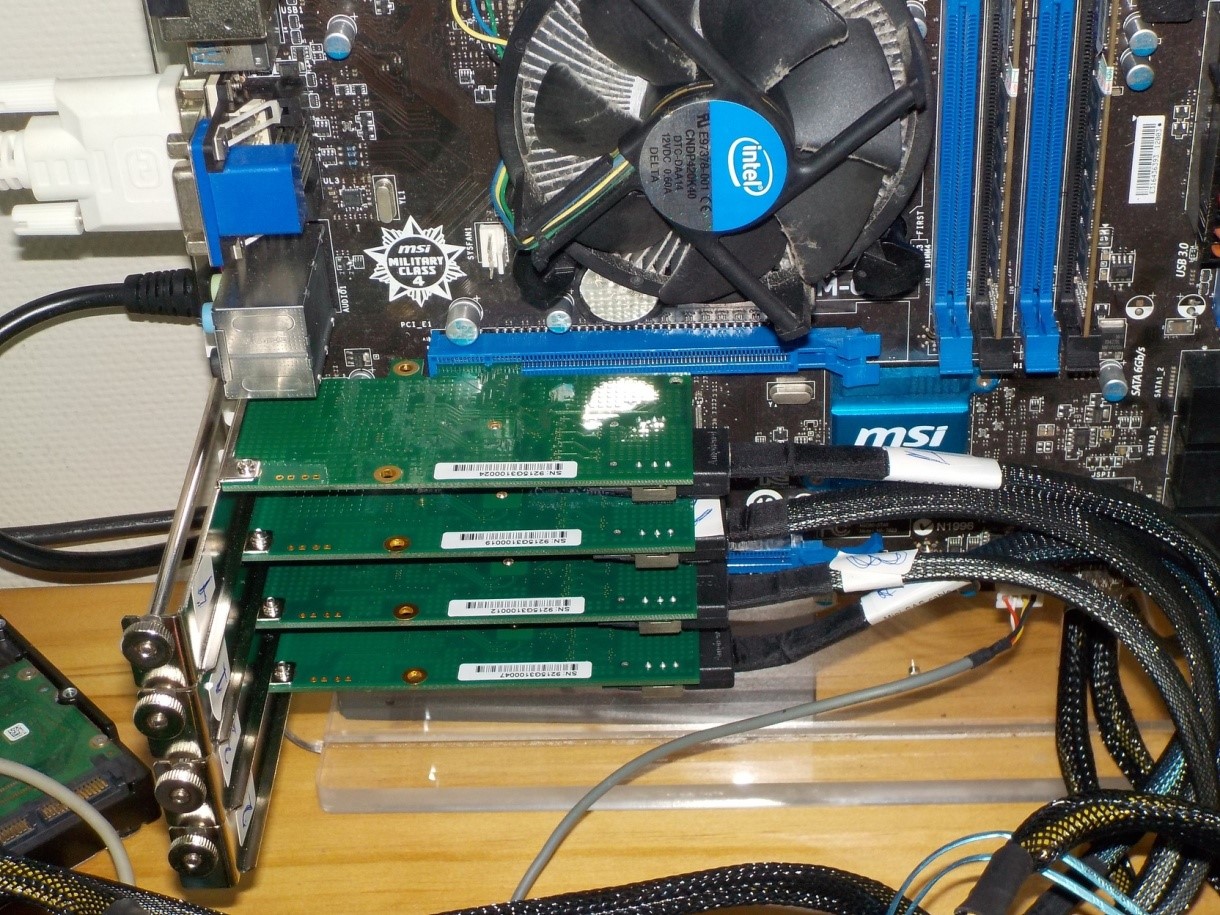

Entonces Todo comenzó bastante mundano. Hubo un chequeo de un programa. Se verificó el proceso de escribir datos en varios discos simultáneamente. El hardware es simple: hay una placa base con cuatro ranuras PCIe. Se insertan tarjetas absolutamente idénticas con controladores AHCI en todas las ranuras, cada una de las cuales admite exclusivamente PCIe x1.

Cada tarjeta sirve 4 unidades.

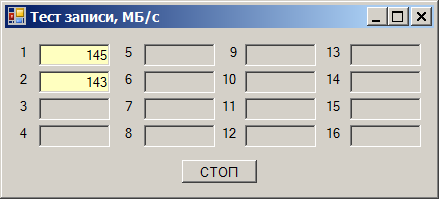

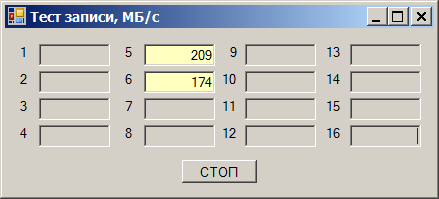

Y luego se revela el siguiente efecto. Tomamos un disco y comenzamos a escribirle datos. Obtenemos una velocidad de 180 a 220 megabytes por segundo (en adelante, los megabytes son 1024 * 1024 bytes):

Tomamos el segundo disco. La velocidad de escritura es de 170 a 190 MB / s:

Escribimos inmediatamente a ambos: obtenemos una reducción de velocidad:

La velocidad total es de alrededor de 290 MB / s. Pero lo sorprendente es que depuramos (por lo que resultó) este programa en las mismas unidades, pero en otros canales. Y todo estuvo bien allí. Nos transferimos rápidamente a esos canales (pasarán por otra tarjeta), obtenemos un excelente trabajo:

Compraré una ranura en una buena zona

Debo decir de inmediato que no vale la pena culpar de todo a los componentes de otra persona. Todo aquí lo escribimos nosotros, comenzando desde el programa en sí, terminando con los controladores. Por lo tanto, se puede monitorear toda la ruta de datos. Lo desconocido se produce solo cuando la solicitud se envió al hardware.

Después del análisis inicial, resultó que la velocidad no está limitada en las ranuras PCIe "largas" y está limitada en las "cortas". Las largas son donde puedes insertar tarjetas x16 (aunque una de ellas funciona en modo no superior a x4), y las cortas son solo para tarjetas x1.

Todo estaría bien, pero los controladores en las tarjetas actuales, en principio, no pueden funcionar en un modo que no sea PCIex1. Es decir, todos los controladores deben estar en condiciones absolutamente idénticas, independientemente de la longitud de la ranura. Pero no Quien vive en el "largo" - trabaja rápido, quien en el "corto" - lentamente. Bueno Y rápido, ¿qué tan rápido? Agregue un tercer disco, escriba en los tres.

En las ranuras "cortas", el límite sigue siendo de alrededor de 290 MB / s:

En el "largo" - en la región de 400 MB / s:

Busqué en todo Internet. En primer lugar, después de un tiempo, ya me reí de los artículos en los que dice que el rendimiento de PCIe gen 1 y gen 2 para x1 es de 250 y 500 MB / s. Estos son megabytes sin procesar. Debido a la sobrecarga (uso esta palabra no rusa para denotar un intercambio de servicios que va en la misma línea que los datos principales) para la generación 2 obtenemos exactamente 400 megabytes por segundo de flujo útil. En segundo lugar, tercamente no pude encontrar nada sobre el número mágico 290 (mirando hacia el futuro, todavía no lo he encontrado).

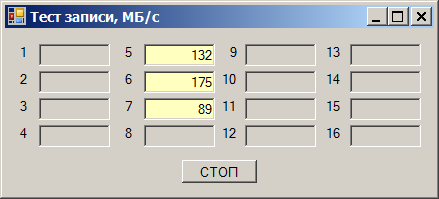

Genial Tratando de ver la topología de la inclusión de nuestros controladores. Aquí está (013-015: estos son los sufijos de los nombres de dispositivos con los que los combiné para distinguirlos de alguna manera). El verde es rápido, el rojo es lento.

El controlador "015" ni siquiera lo consideramos. Vive en una ranura privilegiada diseñada para una tarjeta de video. Pero el 013 está conectado al mismo interruptor que el 012 del 014. ¿Cómo es él diferente?

Algunos artículos dicen que las diferentes tarjetas pueden diferir en la configuración de Max Payload. Estudié el espacio de configuración de todas las tarjetas: este parámetro es para todos en el mismo valor mínimo posible. Además, la documentación para el conjunto de chips de esta placa base dice que no puede haber otro significado.

En general, rebusqué en todo el espacio de configuración: todo está configurado de manera idéntica. ¡Y la velocidad es diferente! Vuelva a leer repetidamente la documentación del conjunto de chips, sin configuraciones de ancho de banda. Prioridades: sí, se ha escrito algo sobre ellos, ¡pero las pruebas se realizan en ausencia total de carga en otros canales! Es decir, no está en ellos.

Por si acaso, incluso apagué el programa de interrupción. La carga del procesador ha aumentado a cantidades increíbles, porque ahora lee constantemente el bit de preparación, pero las lecturas de velocidad no han cambiado. Por lo tanto, es imposible culpar a este subsistema por los problemas.

¿Y qué hay de otras tablas?

Intentamos cambiar la placa base exactamente a la misma. No hay cambio Intentaron reemplazar el procesador (había razones para creer que era basura). Además, no hay cambios en la velocidad (pero el antiguo procesador realmente basura). Instalamos una placa base de nueva generación: todo vuela en todas las ranuras. Además, la velocidad máxima ya no es 400, sino 418 megabytes por segundo, incluso en ranuras "largas", incluso en ranuras "cortas":

Pero aquí, no hay milagros. Con el movimiento habitual de la mano (ya acostumbrado a estos días), leemos el espacio de configuración y vemos que el parámetro Max Payload no está configurado en 128, sino en 256 bytes.

Tamaño de paquete más grande: menos paquetes. Menos gastos generales para enviarlos: más datos útiles logran ejecutarse al mismo tiempo. Eso es correcto

Entonces, ¿quién tiene la culpa?

No daré una respuesta exacta a la pregunta del título, con referencia a los documentos. Pero mi pensamiento siguió el siguiente camino: digamos que la restricción de flujo se establece dentro del conjunto de chips. No se puede programar, está ajustado firmemente, pero lo está. Por ejemplo, es igual a 290 megabytes por segundo para cada diferencia. una pareja Más: ya está cortado en algún lugar dentro del chipset en sus mecanismos internos. Por lo tanto, en la ranura "larga" (donde puede pegar tarjetas de hasta x4), no se corta nada para nuestra tarjeta dentro del chipset, y descansamos contra el límite físico del bus x1. En el conector "corto", nos encontramos con esta limitación.

De hecho, verificar esto no es fácil, pero sí muy simple. Nos quedamos en la ranura 013, no AHCI, sino en el controlador SAS, que sirve 8 unidades a la vez y puede funcionar en modos PCIe hasta x4. Le conectamos 4 unidades SSD inteligentes. Observamos la velocidad de grabación, tanto como el alma se regocija:

Ahora agregamos esos 4 discos que aparecieron en las primeras pruebas. Rendimiento SSD previsiblemente bajado:

Calculamos la velocidad total que pasa a través del controlador SAS, obtenemos 1175 megabytes por segundo. Dividir por 4 (tantas líneas van a la ranura "larga"), obtenemos ... Rollo de batería ... 293 megabytes por segundo. ¡En algún lugar ya vi este número!

Por lo tanto, en el marco de este proyecto, se demostró que el problema no está en nuestro programa o controlador, sino en las extrañas limitaciones del conjunto de chips, que probablemente estén "cableados". Se desarrolló la metodología para seleccionar placas base que se pueden utilizar en el proyecto. Pero en general, sacamos las siguientes conclusiones.

Conclusión

- A menudo, en la vida real, el equipo tiene menos rendimiento de lo teóricamente posible. Los controladores pueden incluso imponer restricciones, como se muestra en el caso de USB. A veces es posible recoger equipos que (o cuyos conductores) no tienen tales restricciones.

- Las limitaciones pueden incluso ser indocumentadas, pero claramente expresadas.

- Una gran cantidad de artículos que dicen que un par diferencial de gen PCIe. 1 y gen 2 da aproximadamente 250 y 500 megabytes por segundo, son erróneos. Copian el mismo error entre sí: un megabyte de datos sin procesar por segundo. La sobrecarga se acumula en varios niveles de la interfaz. Con una carga útil máxima de 128 bytes, PCIe gen2 en realidad obtiene alrededor de 400 megabytes por segundo. En las nuevas generaciones de PCIe, todo debería ser un poco mejor, ya que la codificación física no es 8b / 10b, sino más económica, pero hasta ahora no se ha encontrado un controlador de unidad para verificar esto en la práctica.