El tamaño de los transistores en los microcircuitos modernos está disminuyendo inexorablemente, a pesar del hecho de que han estado hablando sobre la muerte de la ley de Moore durante varios años, y el límite físico de la miniaturización ya está cerca (más precisamente, ya se ha eludido con éxito en algunos lugares). Sin embargo, esta disminución no es en vano, y el apetito de los usuarios está creciendo más rápido que las capacidades de los desarrolladores de chips. Por lo tanto, además de la miniaturización de los transistores, se utilizan otras tecnologías, a menudo no menos avanzadas, para crear productos microelectrónicos modernos.

En mi última oración, utilicé deliberadamente la frase "producto microelectrónico" en lugar de la palabra "microcircuito", porque este artículo se centrará en el hecho de que dentro del estuche de la CPU o GPU puede haber no solo un cristal, sino un sistema completo de varios chips, por lo que y llamado: un sistema en un paquete o sistema en paquete.

El término "sistema en un caso" es mucho menos conocido que el término relacionado "sistema en un chip", que a los desarrolladores les gusta triunfar con cualquier cosa. Además, ahora casi cualquier chip (excepto los más simples) es de alguna manera un sistema en un chip, y los tiempos de conjuntos de microprocesadores e incluso chips individuales de los puentes sur y norte son cosa del pasado. Las ventajas de los sistemas en un chip son bastante obvias: menos casos en el tablero, menos área (y, por lo tanto, más barata), menos inductancias y capacidades extraviadas (lo que significa que el producto funcionará mejor y más rápido), más fácil para el usuario (más conveniente de implementar y menos espacio para errores), más barato en producción (en lugar de varios microcircuitos especializados, se puede producir uno más universal).

Pero los sistemas en un chip también tienen sus dificultades.

En primer lugar, cuando intentas colocar todo en un cristal a la vez, corres el riesgo de obtener un chip de tal tamaño (y con tantas patas) que no cabe en ningún caso. Además (como sugiere un tecnólogo profesional en los comentarios), un chip muy grande corre el riesgo de no alcanzar el tamaño del campo del escáner fotolitográfico. Puede sortear esta limitación, pero es muy difícil técnicamente y, en consecuencia, muy costoso.

En segundo lugar, cuanto mayor sea el tamaño del chip, menor será el porcentaje de rendimiento, especialmente si para la producción necesita unir varias ventanas en una máscara fotográfica. Y esto, por supuesto, también afecta el costo.

En tercer lugar, si su sistema consta de componentes heterogéneos, combinarlos todos en un chip puede ser demasiado difícil, demasiado costoso o demasiado malo para la calidad del sistema. Por ejemplo, DRAM requiere condensadores especiales, agregarlos a un proceso de fabricación "normal" puede ser irrazonablemente costoso para la fábrica (que debido a esto se verá obligado a aumentar los precios para los clientes). Los componentes de radiofrecuencia o potencia en el silicio pueden tener parámetros significativamente peores que en los materiales A3B5 (arseniuro de galio y sus análogos), y la conexión de las partes digital y analógica en el mismo cristal crea un problema de ruido.

La combinación de todos los factores mencionados anteriormente ha llevado al hecho de que la tendencia de "colocar todo en un solo cristal" ha sido reemplazada por un enfoque más equilibrado, así como el rápido desarrollo de tecnologías para el empaque de cristales en un caso.

Rendimiento y rendimiento

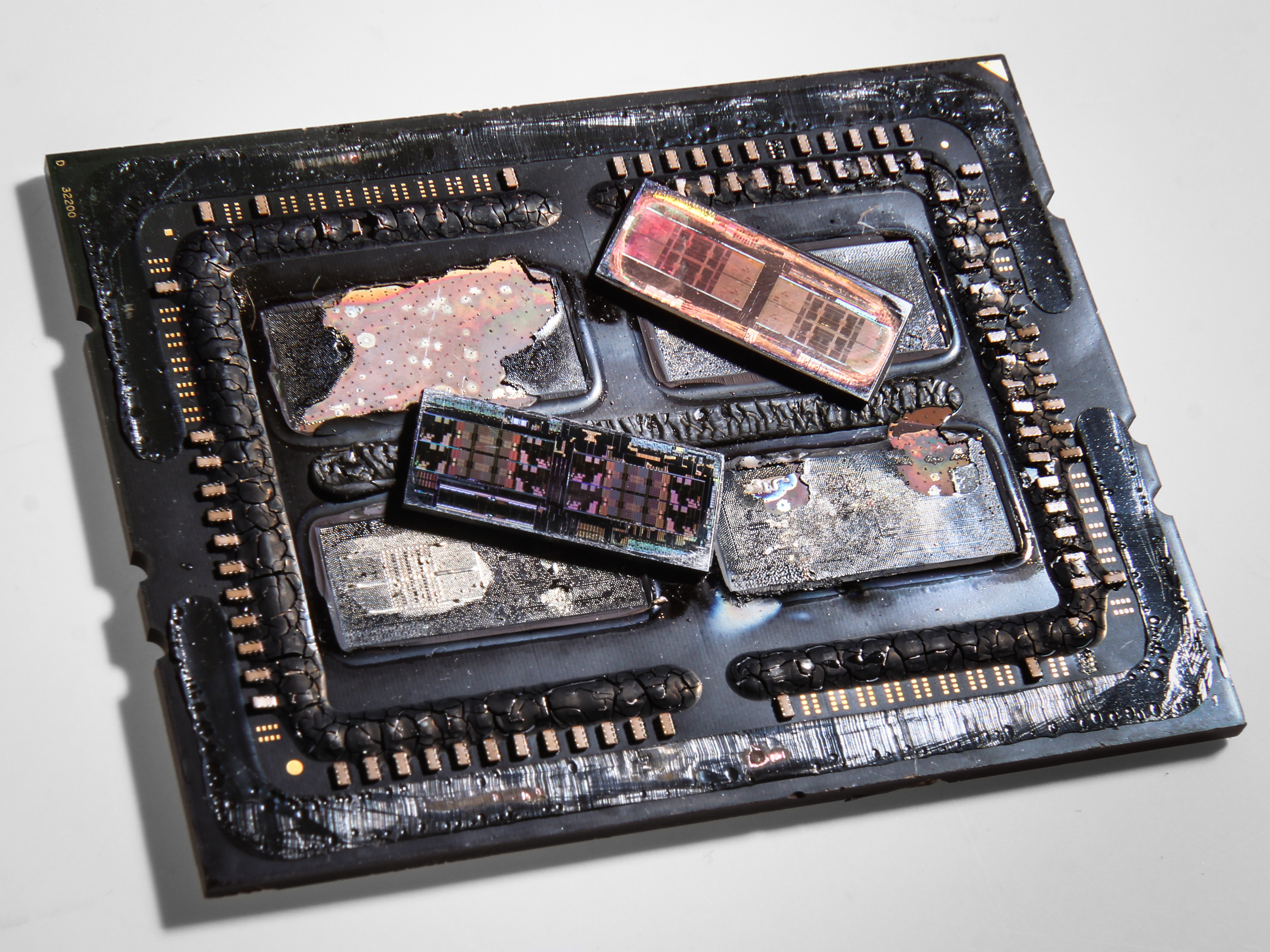

El primer ejemplo que viene a la mente es, por supuesto, los microprocesadores AMD (ver KDPV). Los sistemas en el caso de los productos de múltiples núcleos se consideran una de las razones importantes del reciente crecimiento de la compañía, que tiene lugar en el contexto de los problemas de Intel con el lanzamiento de un nuevo proceso técnico debido al bajo rendimiento en chips enormes.

La figura muestra un chip Intel Xeon de 28 núcleos. El tamaño de estos procesadores alcanza los locos 456 milímetros cuadrados, mientras que el tamaño máximo de los chips AMD es de aproximadamente 200 milímetros cuadrados para un chip de ocho núcleos, y los productos con más núcleos se ensamblan a partir de varios cristales idénticos en una placa de circuito impreso de dos capas ubicada en la caja del procesador.

En esta figura, puede ver el diseño de la placa dentro de la carcasa de los procesadores EPYC y Threadripper (también conocido como KDPV). Cuatro cristales de ocho núcleos se encuentran en un tablero de dos capas. En el caso de Threadripper, con la mitad de los núcleos deshabilitados. ¿Por qué los cristales se usan tan irracionalmente?

Primero, producir un tipo de cristal puede ser más barato que varios diferentes.

En segundo lugar, lo mismo se aplica al resto del arnés: la desactivación innecesaria puede ser más barata y más tecnológica que desarrollar y producir varios modelos diferentes.

En tercer lugar, el porcentaje de rendimiento adecuado para un chip de 200 milímetros, muy probablemente, tampoco es el ideal, y dicho diseño del producto final permite el uso de cristales en los que no todos los núcleos funcionan. Intel hace exactamente lo mismo, pero sus problemas de salida son mucho más fuertes debido a los cristales más grandes.

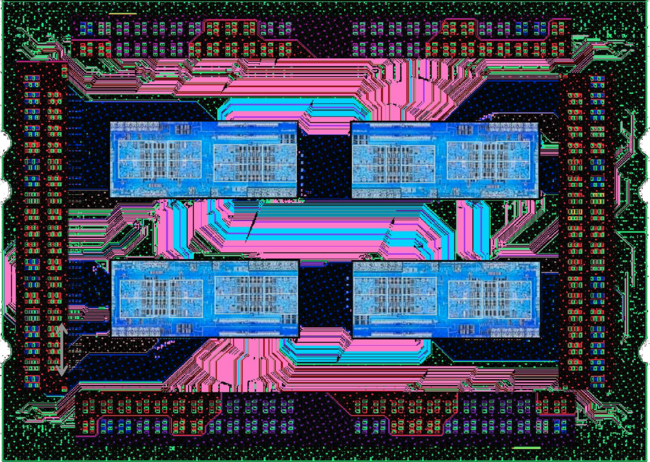

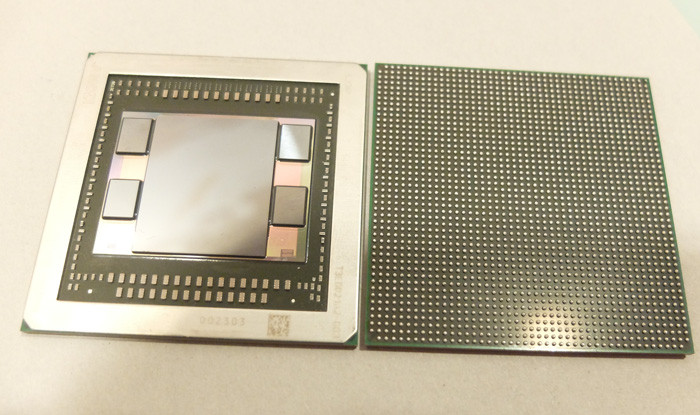

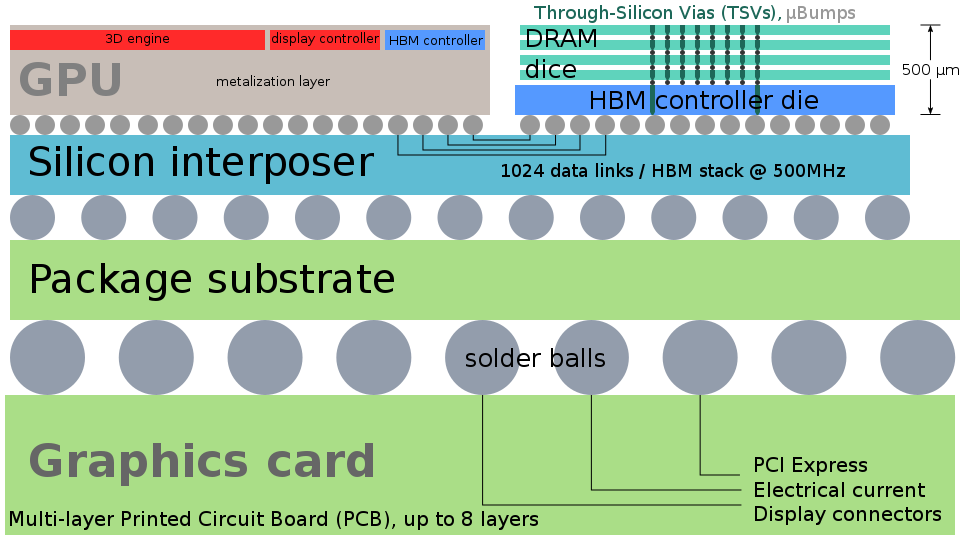

Y aquí hay un ejemplo aún más interesante, también de AMD. AMD Fiji es una GPU con memoria integrada de alta velocidad ubicada en el chasis. ¿Por qué es esto importante? Debido a que las líneas mucho más cortas desde el procesador hasta la memoria permiten alcanzar altas velocidades y, por lo tanto, un mayor rendimiento. A diferencia del ejemplo anterior, los cristales dentro de la caja son diferentes. Además, no hay cinco, como podría parecer a primera vista, sino mucho más: veintidós. Aquí hay una sección de la estructura:

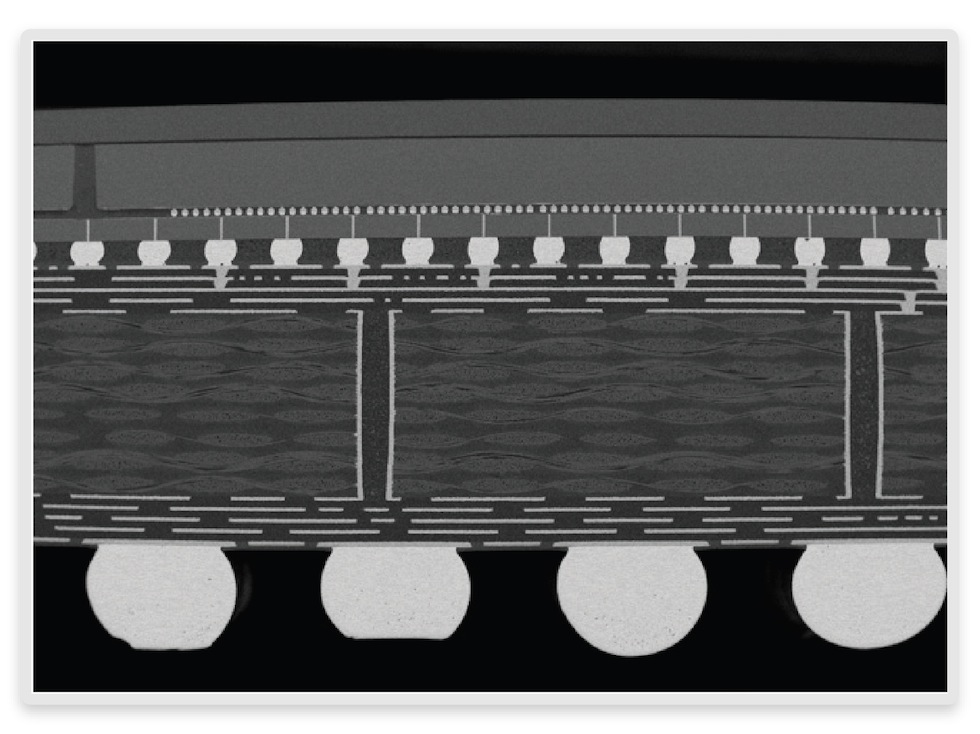

La capa superior es el chip de la GPU y el "estante" de varios (en este caso, cuatro) chips de memoria conectados mediante TSV (a través del silicio), columnas conductoras que atraviesan el cristal a todo el grosor.

Los TSV se parecen a esto, esquemáticamente y en escala real.

La tecnología TSV, que originalmente apareció solo para arreglos de memoria (después de todo, nunca hay demasiada memoria, ¿verdad?), Ahora se está extendiendo cada vez más, incluso gracias al próximo chip ubicado debajo de la GPU y la memoria.

Silicon Interposer es un sustituto de una placa de circuito impreso multicapa hecha de un cristal de silicio y que contiene varias capas de metalización y TSV para conectar los chips en la parte superior y la carcasa. El uso de silicio permite obtener tamaños de elementos (unidades de micras) significativamente más pequeños que una placa de circuito impreso, pero al mismo tiempo los estándares de diseño pueden ser lo suficientemente duros como para que este chip de conexión tenga un alto rendimiento y un precio asequible. Las dimensiones más pequeñas de los elementos significan menos influencia de los parámetros parásitos de las conexiones, y los TSV ya mencionados son mucho más compactos que las vías en la placa de circuito impreso y permiten transportar cientos o incluso miles de contactos a través del intercalador a la caja. Junto con MEMS, tales chips de interconexión son un nuevo mercado importante para fábricas obsoletas con obleas de 100-150 milímetros de diámetro.

Otro pionero de la integración 3D es Xilinx. Tecnológicamente, sus FPGA están cerca de los productos AMD (especialmente aquellos con memoria integrada), y los motivos también son similares: los FPGA son un nicho de mercado donde una transición temprana a un nuevo proceso de fabricación puede brindar una seria ventaja sobre los competidores. Según diversas estimaciones, en una etapa temprana de la vida de una tecnología, reducir el tamaño del cristal de tres a cuatro veces puede aumentar el rendimiento de dos a tres veces, de un par de decenas por ciento a más de la mitad. Además, los FPGA son una estructura regular en la que es conveniente rastrear defectos tecnológicos. Por lo tanto, los fabricantes de FPGA son los "primeros clientes" típicos para los nuevos procesos de fabricación, y Xilinx, debido a que sus productos contienen varios cristales pequeños en lugar de uno de tamaño completo, puede lanzar nuevos modelos varios meses más rápido que sus competidores.

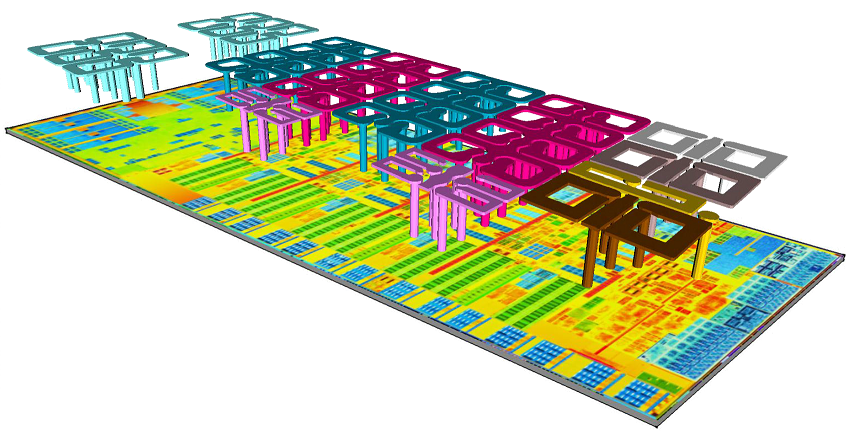

Aquí hay una sección transversal del interior del FPGA Xilinx. El chip superior es en realidad una parte de la FPGA con contactos muy pequeños (40-45 micras) al intercalador que conecta varios chips juntos, y en la parte inferior está la base de la carcasa, que tiene una docena de capas de sus propias interconexiones metálicas.

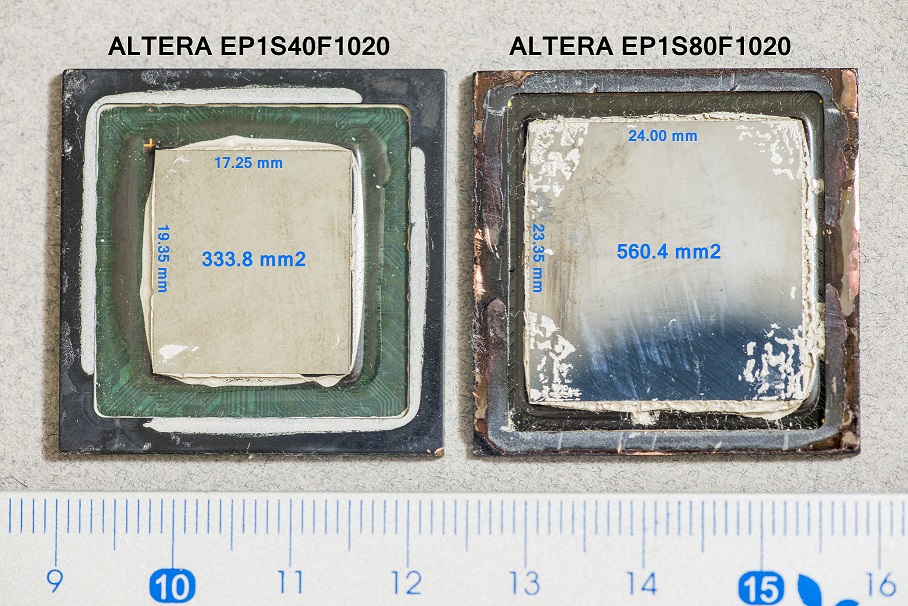

A modo de comparación: FPGA Altera en un gran cristal. Quinientos sesenta milímetros cuadrados, Carl! Si de repente esta publicación es leída por tecnólogos de producción microelectrónica, asegúrese de que no tengan un ataque cardíaco.

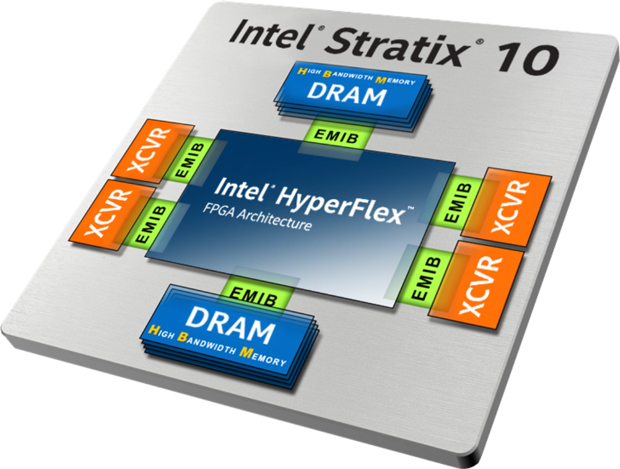

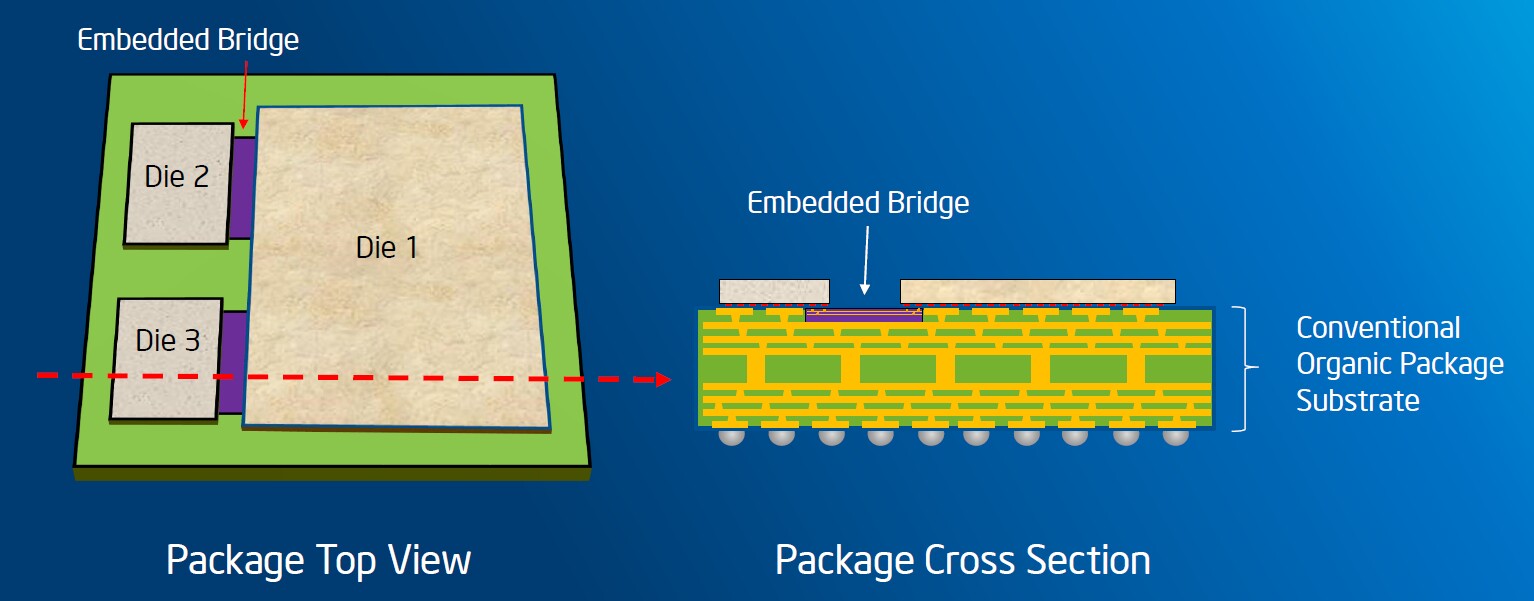

Sin embargo, Intel / Altera, por supuesto, no se queda quieto, observando el éxito de los competidores. Su último desarrollo en sistemas cerrados es el Embedded Multi-Chip Interconnect Bridge (EMIB). Es conveniente mirarlo con el Intel Stratix 10 FPGA.

Como puede ver, EMIB interconecta (¡uno!) Chip FPGA, memoria (y aquí estructuras de varios pisos) y cristales periféricos. Entonces, ¿qué es este EMIB? Un poco más alto escribí sobre el intercalador de silicio que, debido a un proceso técnico más duro, tiene un precio mucho más bajo que un chip de tamaño similar fabricado con tecnología delgada. Sin embargo, el intercalador es enorme. ¿Es posible hacerlo más pequeño?

La respuesta de Intel es sí. La idea de EMIB es utilizar varios pequeños en lugar de un gran intercalador y, a su vez, integrarlos directamente en el sustrato del cuerpo.

Aquí hay una pequeña selección de productos creados con intercaladores de silicio. Presta atención a sus dimensiones colosales según los estándares microelectrónicos y al hecho de que, como discutimos anteriormente, los chips de combate de Xilinx se dividen en varias piezas pequeñas.

Más que solo rendimiento.

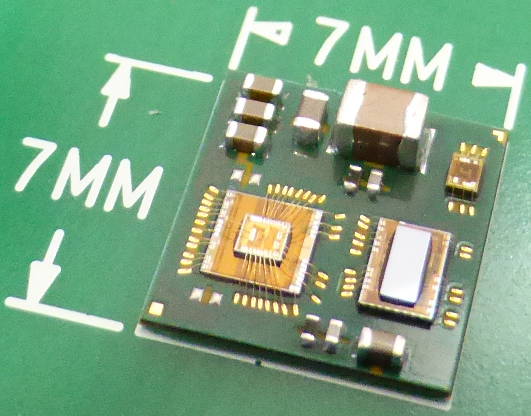

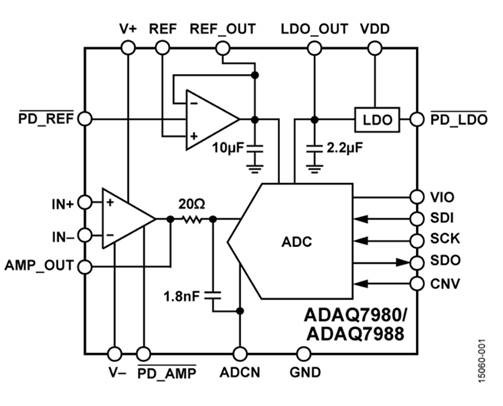

La figura a continuación muestra el interior de un diagrama de circuito y carcasa de ADC de Analog Devices. Parece una placa de circuito impreso completamente normal para el ADC, solo que más pequeña, ¿verdad? Así es, solo debido al uso de componentes de marco abierto, los errores asociados con elementos espurios se han reducido, y el hecho de que la placa se desarrolle en Analog Devices les permite ahorrar mucho tiempo al cliente y al mismo tiempo asegurarse de que el usuario no se equivoque al elegir los incorrectos. componentes o tablero mal cableado.

Sin embargo, hay un pequeño truco en la figura de arriba: ¿ves cristales colocados en dos pisos? El cristal superior es un chip con los componentes activos del ADC y (aparentemente) un amplificador operacional dual, y el cristal inferior son los componentes pasivos (condensadores y resistencias). La ejecución en un cristal separado le permite hacerlos mucho más grandes (y, por lo tanto, reducir los errores) sin aumentar (y por lo tanto, aumentar el costo de) el cristal principal.

Lo mismo se puede hacer en un chip (que, de hecho, no es raro, especialmente para los ADC integrados en microcontroladores), pero dicho chip será mucho más grande (lo que significa que, como descubrimos, existe el riesgo de disminuir el porcentaje de uso), y la tecnología para él tendrá que soportar todas las opciones adicionales necesarias. Además, la combinación de diferentes bloques en el mismo cristal dará lugar a la necesidad de asegurarse de que no se afecten entre sí (por ejemplo, de alguna manera eliminen el ruido en el sustrato de cristal).

Características adicionales de la vivienda

Como ya hemos descubierto, empaquetar elementos diferentes (incluidos los componentes SMD pasivos) en una carcasa le permite reducir significativamente las dimensiones del producto final e incluso aumentar su velocidad. Pero, ¿qué pasa si usamos el caso mismo como un elemento funcional del dispositivo?

En 2013, los procesadores Intel (microarquitectura Haswell) implementaron un regulador de voltaje integrado (FIVR - regulador de voltaje completamente integrado), en el que la parte activa del regulador se implementó en el chip del procesador, y la parte pasiva (condensadores e inductores) se integró en la carcasa.

La inductancia integral es un dolor de cabeza para todos los desarrolladores de chips, porque las bobinas en el chip se obtienen no solo con los mejores parámetros, sino también con los enormes (lo que significa que son muy caros, especialmente con tecnologías delgadas). Y esto se trata de bobinas de señal sin núcleo, no se habla de ninguna transmisión de potencia. Intel evitó con éxito este problema integrando docenas de pequeñas bobinas paralelas que funcionan a una frecuencia de 160 MHz en la carcasa del microprocesador. Por lo tanto, pudieron simplificar significativamente los requisitos de energía del microprocesador.

Sin embargo, algo salió mal con este desarrollo, y ya no había procesadores Intel FIVR en la próxima generación de procesadores Haswell. Desde entonces, ha habido rumores de que regresarán a la FIVR, pero hasta ahora han seguido siendo rumores.

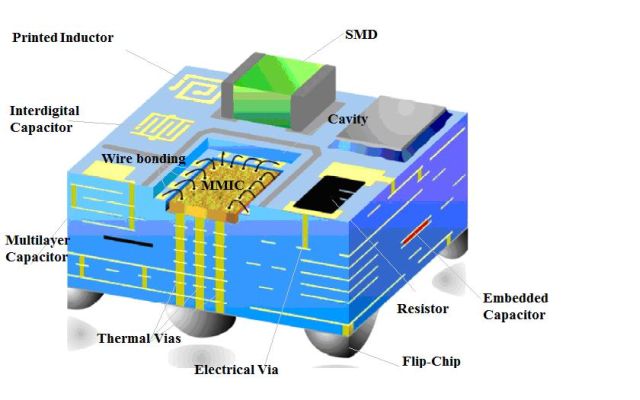

Sin embargo, incluso sin Intel, la dirección de integración de componentes pasivos en el caso se está desarrollando activamente, por ejemplo, en casos de tipo LTCC (cerámica de baja temperatura). Allí, por supuesto, existen limitaciones y dificultades (asociadas, por ejemplo, con la precisión de las calificaciones), pero esta tecnología está en demanda y se está desarrollando activamente. El caso LTCC en capas se ve así:

La figura muestra todos los tipos de elementos pasivos hechos en cerámica multicapa e incluso un disipador de calor de metal (este es el caso de un potente circuito de microondas). De hecho, es una mezcla de la caja con una placa de circuito impreso de cerámica. Estas piezas son muy populares para los módulos de RF, y también son relativamente baratas en la producción a pequeña escala.

Que mas

Hay muchas aplicaciones potenciales para sistemas en el caso, y es casi imposible enumerarlas todas; Además, constantemente aparece algo nuevo, incluso debido al hecho de que estas tecnologías son mucho más asequibles que los transistores de 10-7-5-3 nanómetros.

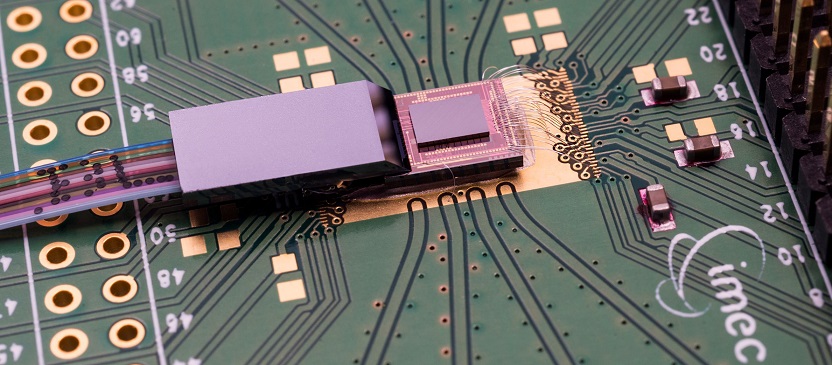

Un buen ejemplo de las nuevas aplicaciones y propiedades que abre la integración de chips heterogéneos en un paquete es una variedad de sistemas ópticos en los que SiP le permite ensamblar un receptor o emisor (generalmente no fabricado en silicio) y sus circuitos de alimentación y control. En la siguiente ilustración, un prototipo de enlace óptico a 400 Gb / s (y prometedor antes de terabit), montado en el instituto de investigación belga IMEC.

Además, las aplicaciones de perspectiva como los sistemas en el caso consideran cosas como interpozers con capilares incorporados para refrigeración líquida (no solo procesadores de juegos, sino también teclas de encendido y láser), unidades MEMS integradas en el caso, y mucho más. no caer dentro del marco estrecho de la ley de Moore. Además, la ubicua Internet de las cosas se considera un mercado importante para los sistemas en el caso, donde los tamaños pequeños, la ausencia de pérdidas (principalmente energía, no tiempo) en elementos espurios y la capacidad de integrar componentes pasivos, por ejemplo, partes de la ruta de radio, en el microcircuito son importantes.