La semana pasada, Intel anunció la adquisición de eASIC, que está desarrollando herramientas de desarrollo basadas en FPGA para "ASIC estructurales". Los ASIC estructurales son un cruce entre los FPGA convencionales y los ASIC convencionales; le permiten reducir el tiempo de comercialización del producto y reducir su costo.

Intel ha estado utilizando la tecnología eASIC

desde 2015 en versiones personalizadas de procesadores Xeon; eASIC (120 personas) ahora formará parte del Grupo de Soluciones Programables Intel (PSG).

Incluso aquellos que hace mucho tiempo y se "hicieron amigos" mutuamente de FPGA y ASIC no se negarán a explicar qué son los "ASIC estructurales". La potencia informática de la computadora no se limita a la CPU o GPU, hay otras clases de procesadores, como, por ejemplo, FPGA, desarrollados por Altera, adquiridos por Intel. En los FPGA, se pueden programar de forma flexible millones de puertas para implementar la funcionalidad requerida. De hecho, la mayoría de las CPU y GPU se simulan inicialmente en FPGA para probar el rendimiento. Los FPGA son una forma simple de modelar circuitos de interconexión, y su alcance es amplio. Los FPGA también pueden contener unidades de hardware estándar, como núcleos ARM o transceptores para comunicaciones externas.

Otro ejemplo es ASIC (Application Integrated Integrated Circuit), un chip diseñado para realizar un conjunto bien definido de tareas. ASIC está optimizado al máximo para sus tareas, y la lógica de su trabajo no se puede cambiar. A menudo, la CPU y la GPU se clasifican como ASIC en el sentido de que su microarquitectura también es fija, pero están diseñadas para resolver una variedad de problemas y son universales, mientras que los ASIC se crean para tipos de cálculos claramente definidos. Características de ASIC: son rápidas, económicas, pero relativamente caras y difíciles de fabricar.

Los ASIC estructurales de EASIC se pueden llamar una solución poco entusiasta. Los ingenieros crean un prototipo usando FPGA, pero no pierden el tiempo optimizando sus circuitos, sino que fabrican un chip con una arquitectura fija sobre la base. Debido a esto, funciona más rápido que una muestra con bloques personalizados, aunque pierde los beneficios de la eficiencia energética. Sin embargo, el tiempo para su desarrollo es comparable al FPGA, no al ASIC: ahorra hasta 6 meses. La contribución de eASIC es que la optimización de capa de capa única se usa para reemplazar el enrutamiento SRAM con un extremo a otro, lo que reduce significativamente los costos de producción. eASIC también proporciona bibliotecas de células fijas, también de una sola capa, lo que reduce aún más el consumo, el tamaño del cristal y el tiempo de comercialización. Además, los diseñadores pueden omitir los procedimientos estándar al crear ASIC, como sincronización de equilibrio, análisis de integridad de señal, prueba de atenuación de potencia y otros. Por lo tanto, los "ASIC estructurales" pueden describirse como FPGA que no pueden programarse más, que tienen las mejores cualidades tanto de FPGA como de ASIC.

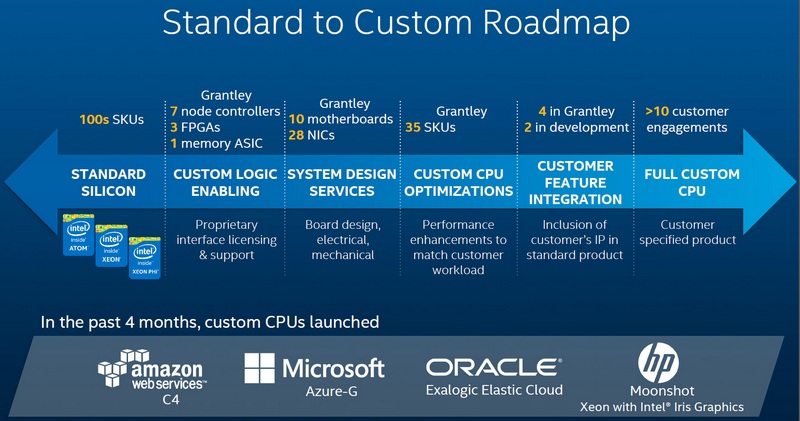

El gráfico muestra el estado actual de las cosas y las perspectivas en el campo de los procesadores Intel Xeon personalizados.

El gráfico muestra el estado actual de las cosas y las perspectivas en el campo de los procesadores Intel Xeon personalizados.Intel necesita la tecnología eASIC para integrar la lógica programable en los procesadores Xeon para mejorar el rendimiento, el consumo de energía y el precio. Junto con el Xeon estándar, Intel ahora está lanzando opciones personalizadas para sus clientes más grandes. Como podemos ver en el diagrama, aumentará la profundidad de la personalización. Con la adquisición de eASIC, este proceso se acelerará y expandirá. Parece que el enfoque de "CPU como ASIC" puede traernos muchas cosas interesantes.