1. Introducción

Todos conocemos el problema de la gallina y los huevos: los empleadores no quieren contratar graduados sin experiencia laboral, pero ¿dónde, entonces, pueden los graduados obtener experiencia laboral? En microelectrónica, este problema es especialmente agudo en vista de la enorme cantidad de experiencia específica requerida. Desde la época soviética, nuestras universidades son famosas por la formación teórica más amplia, que debería ayudar al graduado en cualquier situación difícil de la vida. Sin embargo, la industria moderna requiere experiencia práctica. Agregamos aquí la falta de motivación, lo que lleva al hecho de que el 15% de los graduados trabajan en la especialidad, y tenemos la escasez de personal más severa en la industria, que es muy exigente en la calidad del personal. Pero si cada estudiante pudiera "parpadear una bombilla" de su propio cristal, la situación podría desarrollarse de una manera completamente diferente.

Figura 1. KDPV

¿Qué impide que tales gigantes de capacitación en microelectrónica doméstica, como MEPhI y MIET, actúen de manera similar a sus colegas extranjeros (por ejemplo, MIT o UZH), es decir, al darles a los estudiantes graduados la oportunidad de producir sus propios cristales? Por supuesto, se puede suponer que la producción del propio cristal es una tarea extremadamente larga, complicada y costosa, y por lo tanto es costosa para un instituto e imposible para un estudiante. Sin embargo, esto no es así. Echemos un vistazo a una de las tecnologías disponibles en el mercado nacional de microelectrónica, un conocimiento que permitirá que el estudiante sea mucho más atractivo en términos de empleo futuro, y la oferta de la cual para el estudiante permitirá que la universidad aumente significativamente su calificación a los ojos de los solicitantes y empleadores.

2. ¿Qué es BMK?

BMK es un cristal matricial básico. ¿No se hizo más claro? Luego, dé un paso al costado y observe el ciclo de producción de fabricación de chips personalizados (ASIC) muy simplificado:

- Desarrollo de Descripción de Esquema

- Creación de topología

- Transferir archivos de tecnología a la planta y esperar que los cristales estén listos

- Mediciones de los cristales obtenidos.

- Carcasa

- Para la venta

Aquí hay dos puntos muy "largos": el desarrollo del esquema y la expectativa de los resultados de la planta. Se utilizan diversas metodologías para reducir el tiempo de desarrollo, y en un entorno estudiantil la mejor solución es el trabajo en equipo, pero estamos interesados en el segundo punto: las horas de trabajo de la planta. Debido a que la planta microelectrónica es una producción muy inerte, todo debe estar de acuerdo con el plan. ¿No está a tiempo para la fecha de lanzamiento de la producción? El siguiente intento es durante el trimestre. La producción en sí, dependiendo de la complejidad del producto, puede durar hasta seis meses. Además, estos seis meses son el ciclo de producción aprobado en máquinas altamente automatizadas, y no el descuido del personal. ¿Cómo se pueden reducir estos términos? Al introducir una cierta base común en todos los esquemas producidos, de modo que la etapa de introducir diferencias sea rápida.

Esta base común es el BMK, un cristal con transistores predispuestos, cuyo propósito funcional está determinado por las capas de metalización, que permiten que los transistores se interconecten. Estas interconexiones forman la funcionalidad única del cristal.

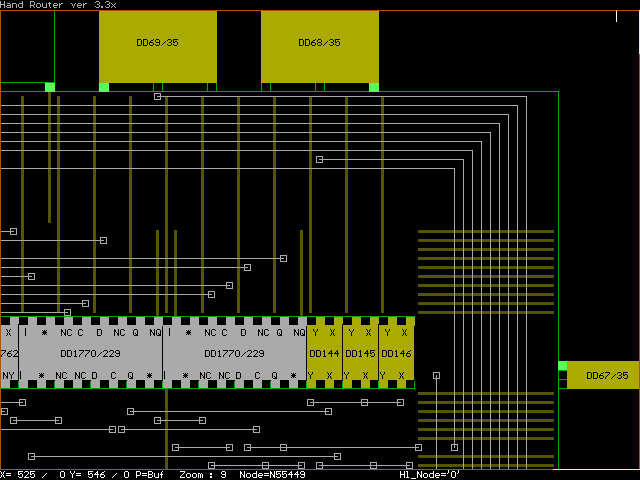

Figura 2. Hand Router v3.3, originalmente de las entrañas de NICEVT, creado en las décadas de 1980 y 1990.

En un BMK, usando diferentes esquemas de metalización, es posible producir cientos de microcircuitos diferentes para varias organizaciones. En este caso, BMK se convierte en un producto de producción en masa para la planta, y las etapas de acabado (capas de metalización) se pueden cambiar rápidamente de acuerdo con los requisitos del cliente. Por lo tanto, tenemos "lanzamientos" más frecuentes de nuevos productos en producción y precios más bajos. Para el desarrollo del estudiante, ambos puntos son extremadamente relevantes.

3. ¿Por qué BMK?

Comparemos los beneficios de usar diferentes métodos de entrenamiento y veamos qué produce el mayor efecto al menor costo.

Tabla 1. Comparación del efecto educativo del aprendizaje utilizando varios métodos.

Codificación de encabezado de lo contrario, no cabe en el ancho del diseño.

A - Desarrollo orientado a FPGA

B - BMK sin el uso de FPGA y con un lanzamiento real

C - BMK usando FPGA y con lanzamiento real

D - ASIC sin FPGA y sin lanzamiento real

E - ASIC con FPGA y sin lanzamiento real

F - ASIC con FPGA y lanzamiento real

G - Programa de entrenamiento actual en MEPhI, kaf. 27

| Componente de ruta | Un | B | C | D | E | F | G |

|---|

| Declaración del problema. | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| Programación RTL | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| Programación RTL basada en ASIC | □ | ■ | ■ | ■ | ■ | ■ | □ |

| Trabaja con CAD moderno | ○ | ■ | ■ | ■ | ■ | ■ | ○ |

| Comprender el código específico de FPGA | ■ | □ | ■ | □ | ■ | ■ | ○ |

| Comprender el sintetizador | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| Comprender los requisitos de restricción | ○ | ■ | ■ | □ | □ | ■ | □ |

| Comprender la importancia de la ubicación y el rastreo | ○ | ■ | ■ | □ | □ | ■ | □ |

| Prueba | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| Creación del entorno de verificación. | ■ | ■ | ■ | □ | ■ | ■ | □ |

| Simulación de múltiples esquinas | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| Modelado de extracción | □ | ■ | ■ | ■ | ■ | ■ | □ |

| Carcasa | □ | ■ | ■ | □ | □ | ■ | □ |

| Circuitería analógica | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| Trabajar con instalaciones de medición. | □ | ■ | ■ | □ | □ | ■ | ○ |

| Trabajo en el laboratorio | ■ | ■ | ■ | □ | □ | ■ | ○ |

| Costo | 1 | 2 | 3 | 0 0 | 1 | 4 4 | 0 0 |

■ - está presente en el programa;

□ - ausente en el programa;

○: las opciones son posibles.

Esta tabla se llena únicamente desde mi visión de cómo la presencia de una etapa particular en un proyecto de graduación esférica en el vacío afecta la diligencia de los estudiantes. En realidad, alguien puede dominar toda la ruta sin ayuda de enseñanza, mientras que alguien no puede escribir un multiplexor en Verilog. La línea "costo" refleja el posicionamiento en la parte superior, pero en ningún caso multiplicadores. Además, el "costo" no tiene en cuenta el costo real de CAD, por diferentes razones.

Ahora queda claro que a un costo adicional más bajo, la ruta destinada al lanzamiento de BMK, utilizando FPGA y con lanzamiento real cubre exactamente el mismo conjunto de habilidades que es necesario para el lanzamiento de ASIC. El resto de las rutas, aunque nominalmente cubren una amplia gama de habilidades, en la práctica, no son realizadas concienzudamente por los estudiantes debido a la falta de motivación para aplicar una gran cantidad de esfuerzo sin ningún resultado visible.

4. Vigilancia del mercado

Hasta la fecha, el diseño de microcircuitos de nivel de entrada se ha convertido en una tarea bastante simple: todos han oído hablar de FPGA (circuitos integrados lógicos programables), sintetizadores de código, programas para organizar componentes y el seguimiento posterior del microcircuito. Al mismo tiempo, muchos desarrolladores novatos tienen dificultades para imaginar qué es BMK, cómo trabajar con él y qué ventajas ofrece. Desafortunadamente para los fabricantes de BMK, esta situación lleva a los siguientes resultados:

"El análisis de 2009 muestra la salida de algunos consumidores debido a la expansión del ámbito de aplicación de los FPGA importados sobre la base de los permisos emitidos". (C) el informe anual de Anstrem OJSC para 2009.

Hay muchos fabricantes de BMK en el mercado moderno de microelectrónica: tanto nacionales como extranjeros. En particular, en el Estado de la Unión de Rusia y Bielorrusia hay al menos seis fabricantes de microcircuitos que ofrecen sus BMC para el desarrollo: Angstrem OJSC, IEC NN, Progress NIIMA JSC, Centro Tecnológico Centro Científico y de Producción, Física Física OJSC e Integral Minsk ".

Por lo general, los sistemas CAD especializados de compañías conocidas como Cadence, Synopsis o Mentor Graphics se utilizan para el desarrollo de microcircuitos, pero en el caso de BMC, todo es algo más complicado. Este software no proporciona soporte oficial para BMK, como un tipo separado de microcircuito, pero es posible hacerlo funcionar en el modo correcto usando varios trucos. En esta situación, los desarrolladores de BMK tienen que desarrollar sus propias rutas de diseño únicas, que a veces usan el software OpenSource, por ejemplo, Yosis, junto con software desarrollado independientemente.

- En el caso de Angstrom OJSC, es muy difícil encontrar la información exacta y el CAD utilizado. Sin embargo, existen requisitos previos para creer que su CAD "Nevod" ya no se usa y la transición al uso de los productos Cadence se ha completado.

- IEC NN, OJSC NPO Fizika, JSC NIIMA Progress e Integral no proporcionan información sobre el CAD utilizado, sin embargo, Integral tiene PDK bajo Cadencia, por lo que podemos concluir que el resto de la ruta también está allí.

- El "Centro Tecnológico" de NPK utiliza su "Arca" CAD, que implementa casi toda la ruta de diseño. En cualquier caso, esto está aprobado en su sitio web.

5. ¿Cuántas válvulas son suficientes para todos?

Una razón popular por la que no está dispuesto a trabajar con BMK es la incertidumbre acerca de si el esquema desarrollado se ajustará a este BMK y a qué velocidad funcionará todo esto. Por supuesto, es bueno cuando hay una serie BMK con una sola biblioteca de diseño, y puede saltar a un cristal más amplio o más rápido si es necesario, pero esto no siempre es posible. Aquí, por ejemplo, todo está claro sobre TSMC: hay muchas compañías que declaran abiertamente la velocidad de sus circuitos en uno u otro de esos. proceso ¿Qué hay de nuestro BMK? ¿Dónde puedo obtener una lista de productos creados en base a BMK y ver su rendimiento?

Algunos ejemplos

- BMK digital a analógico. Alrededor de 300 puertas + 8 transistores de potencia. Se implementa un esquema de temporizador durante 2 minutos con dos niveles de protección. Monitoreo de carga en espejos de corriente, transistores de potencia para controlar la carga. Consumo de energía reducido, trabajo con cuarzo 32.768 kHz, el rango de voltajes de alimentación de 1.8V a 9V.

- Me alegro digital. BMK persistente. 100,000 válvulas. Especiales de lógica. destino + NCO (oscilador controlado numéricamente). Fase de batería 40 bits, seno - 12 bits. Dos registros controlan la frecuencia sinusoidal, el control en paralelo y en serie. La salida es paralela.

- BMK digital a analógico. Cerca de 400 puertas + DAC de 10 categorías. Generador sinusoidal de 7 bits con salida de corriente.

- BMK digital. De 1500 a 3000 válvulas. Varios terminales del canal multiplex GOST 26765.52-87.

- BMK digital. Cerca de 500 puertas. Un generador de ocho canales para controlar los devanados primarios de los transformadores.

- BMK digital. Cerca de 3000 puertas. Circuito mayoritario para bus de 8 bits.

Desafortunadamente, los detalles del mercado conducen al hecho de que la gran mayoría de los desarrollos en BMK siguen siendo desconocidos para el público en general. Los datos públicos no dan una idea clara de la velocidad, y las cifras indicadas en los folletos parecen ambiguas. Sin embargo, para las tareas de conocer la tecnología, no se requiere mucho, y ya tener algo de experiencia detrás es mucho más fácil dar una estimación aproximada de la complejidad de un esquema particular.

6. Proceso de desarrollo

Pasemos a lo más interesante. Tenemos: BMK para ~ 3k válvulas (1 válvula = 2 transistores CMOS) con arquitectura de canal, cableado en una capa de metal y una subcapa de polisilicio; entusiasmo aprobación de la gestión empresarial para la capacitación personal de los empleados.

La idea del futuro cristal nació de la ociosidad, es decir, de la lectura de un foro, donde, en particular, hubo una conversación sobre soluciones compactas de circuito para calcular códigos sinusoidales. Este tema me pareció interesante y decidí ver qué se puede hacer en esta dirección.

Ahora veamos qué se hizo, qué no se hizo, qué errores y qué conclusiones se hicieron.

6.1 Diseño

Los estudios de superficie han demostrado que existe un algoritmo para calcular valores sinusoidales, que a partir de operaciones matemáticas solo requiere suma, resta y desplazamiento hacia la derecha. Resultó que esto no es solo un algoritmo, sino toda una familia llamada CORDIC (Coordinate Rotation Digital Computer). Aquellos que estén interesados en los detalles del algoritmo pueden consultar la lista de referencias al final del artículo, pero solo aclararé que usando este algoritmo puede calcular no solo el seno, sino también el coseno, la tangente del arco, multiplicar y dividir los argumentos, y contar algunas funciones hiperbólicas.

Después de estudiar muchas publicaciones sobre este algoritmo y sistematizar este conocimiento en mi cabeza, pensé que puede intentar implementar este algoritmo en un BMK con una capacidad de aproximadamente 3k válvulas.

Entonces, ¿con qué terminamos en la arquitectura de circuitos?

- Algoritmo CORDIC canalizado expandido para calcular el seno.

- 4 bits adicionales en buses de datos internos para compensar los errores de redondeo.

- Totalizador acumulativo de 11 bits para el valor de fase.

- El incremento de fase lo establece el bus paralelo.

- Formato de datos de salida: 7 bits + signo, bus paralelo.

Todo parece estar bien, pero ¿qué sucede si no compensa los errores de redondeo? Y esto es lo que (comparando el bus interno de 11 bits y 8 bits):

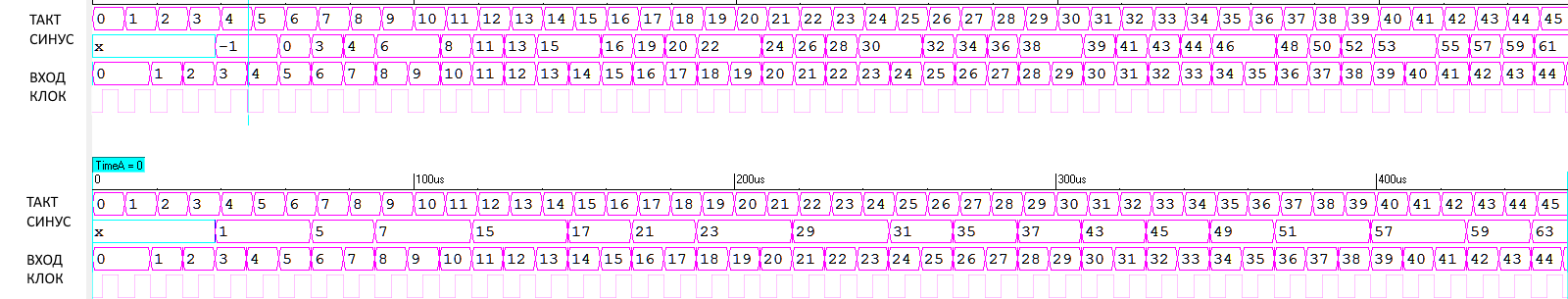

Figura 3. Comparación de la salida del algoritmo CORDIC cuando se utilizan buses internos de 11 bits y 8 bits, respectivamente.

Si presta atención a las segundas líneas de datos, puede ver que los errores de redondeo pueden reducir efectivamente la calidad de sus cálculos.

Si en el futuro conectamos este chip al DAC de 7 bits, obtendremos un generador de seno completamente adecuado (DDS, en nuestra opinión, síntesis digital directa). En este caso, tendremos la oportunidad de modulación de frecuencia del seno, pero no habrá posibilidad de modulación de fase.

En general, la ruta para trabajar con BMC pequeños es algo diferente de la ruta de diseño actual. Si lo piensa, las diferencias se vuelven obvias: con un volumen de válvula tan pequeño, es necesario usar cada válvula de manera extremadamente eficiente, y el paradigma principal del diseño moderno no es en absoluto eso. Ella dice que el producto debe ser arquitectónicamente compatible en cada etapa con los sistemas modernos de pruebas, verificación y medición automatizadas. En este caso, la cuestión de la eficiencia de la válvula permanece fuera de los soportes, como la sobrecarga necesaria. De hecho, en los años de desarrollo dinámico de las tecnologías de producción, pensar en la eficiencia era superfluo. Entonces, cuando (y si) todavía alcanzamos el límite físico y nos detenemos para aumentar la densidad de los transistores en el cristal, entonces los problemas de la eficiencia del uso del área se nos presentarán en pleno crecimiento. Bueno, con los BMK pequeños ya están parados a toda altura, y por lo tanto, la conclusión: en el BMK de los tanques pequeños, puede y debe usar diseños complejos usando varios esquemas de generación de bloques difíciles, varios pestillos, retroalimentaciones y otras cosas, para el uso de los cuales en la ruta moderna un ingeniero superior se habría desgarrado las manos.

El principal problema con el uso de tales cosas es que, para usarlas, el ingeniero debe ser claramente consciente de lo que está haciendo y por qué. Sin embargo, si hay comprensión, la ganancia puede ser fantástica. Si no hay comprensión ... bueno, puedes disparar en la pierna con un millón de formas efectivas diferentes.

¿Cómo se veía la ruta de diseño en mi caso?

- Gráficos manuales como un gráfico de elementos de la biblioteca.

- Estimación del volumen del circuito resultante.

- Procesando el circuito hasta que el volumen del circuito exceda el 80% de la capacidad de BMK

- Esto también incluye el trabajo en la creación de nuevos elementos de biblioteca, su prueba e integración en la ruta de diseño

- Elaboración de pruebas para el circuito.

- Trazado de circuito manual

Los diseñadores experimentados aquí pueden objetar de inmediato que se han omitido varios pasos importantes, pero realmente olvidé mencionar cualquier cosa.

El diseño manual muestra muy bien lo importante que es una biblioteca de componentes de calidad. Las primeras variantes del circuito no encajaban en el cristal simplemente por el volumen de la lógica, sino que en el caso de un canal BMC, uno donde el cableado pasa a través de los canales colocados entre las "filas" de transistores, aproximadamente el 30% del volumen del circuito está ocupado por interconexiones. Por lo tanto, tuve que expandir un poco la biblioteca, según la topología que se obtuvo en este proyecto en particular. Este enfoque permitió salvar un número significativo de puertas e incluso colocar más o menos libremente todas las rutas.

El relleno final del cristal es del 72%, otro tercio del cristal fue al cableado. Luego los archivos fueron transferidos a la fábrica, y volví a mis proyectos de trabajo actuales.

Con el método de diseño "manual", deben recordarse los siguientes puntos:

- No puede usar elementos de la biblioteca sin pensar en función de su función. Es necesario estudiar de qué está compuesto este elemento a nivel de transistor, ya sea digital o analógico. ¿Cuáles son sus capacidades de carga en términos de entradas y salidas, ya sea puramente CMOS lógica, o TG, o alguna otra cosa?

- Es necesario tener en cuenta y coordinar el poder de los elementos y su carga.

- Si tiene un disparador síncrono, entonces necesita cronometrarlo con señales de igual potencia.

- Si usa algún tipo de señal sin amplificación intermedia, y se carga en muchos consumidores, entonces la señal puede fallar mucho. Esto puede ser insignificante en condiciones normales, pero es crítico cuando se realiza una prueba de WWF (factores externos).

Ningún sistema de modelado puede reemplazar sus propios cerebros. En general, no puede ejecutar una simulación si usted mismo no comprende cómo funciona el circuito.

6.2 Mediciones

Una etapa extremadamente importante en el trabajo con un cristal son sus medidas. Se pueden distinguir tres tipos de mediciones: tecnológicas, funcionales, eléctricas. Los primeros verifican que la planta no se ha detenido y que el cristal está tecnológicamente fabricado correctamente. Estos últimos verifican que la teoría (es decir, el modelado) converge con la práctica (cristal real). , : , , . , , . , - . , . — , — . , … , , . .

, . , Fairchild 80- USB, . FORMULA "", . HP - Unix' . National Instruments , , , (). Agilent, . , ?) .

, -, , . , , , , Fairchild, , NI. , . - , , .

, , :

- , .

- . , .

- "" .

- , , , .

- .

- :

- /, , . /.

- , .

- , – . .

- , «» , .

- , .

, , .

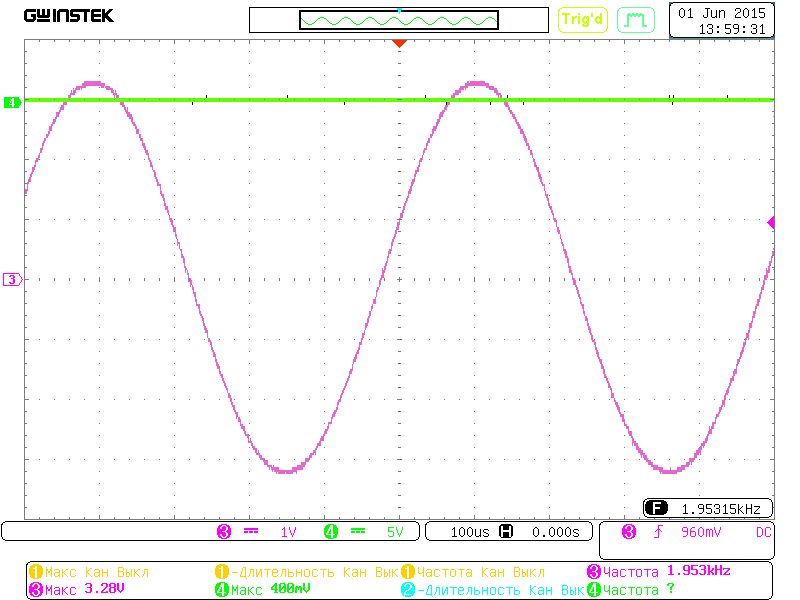

. 4 (!) . , , . , ?) " ".

4. .

, . , , . 80 , , , , 8- .

, . :

5.

6.

, , .

, — . , . 8- . .

6.3

?

- ;

- NCO(numerically controlles oscillator);

- , , NCO ROM(cROM);

- ;

- :

- , ;

- ;

7. , HRT.

:

- — 83%.

- 14

- 11

- (sin & cos, 12 )

- 16

, , ? , . , - .

, . , . , — . .

7. ?

.

.

30 000 100 2. , " " . , , Setup&Hold, , Verilog' , , , — , , . , — , , , … . — , .

. .

-

MIT Massachusetts Institute of Technology

UZH Universität Zürich

ASIC Application specific integrated circuit

-- []

CORDIC Coordinate Rotation Digital Computer

-

NCO Numerically controlled oscillator

ROM Read-only memory

cROM Compressed ROM

Literatura

- CORDIC IP Block Design, Vitaliy Kuhar, Stockholm, Sweden 2008

- CORDIC. , . . , . .

- Comparison of parallel and pipelined CORDIC algorithm using RCA and CSA, Guerrero, Meloni

- CORDIC for dummies.pdf

- Sine/Cosine using CORDIC Algorithm, Prof. Kris Gaj

- Lecture_cordic.pdf