Usar la arquitectura von Neumann para aplicaciones con inteligencia artificial es ineficiente. ¿Qué la reemplazará?

El uso de arquitecturas existentes para resolver los problemas del aprendizaje automático (MO) y la inteligencia artificial (IA) se ha vuelto poco práctico. La energía consumida por la IA ha crecido significativamente, y la CPU, junto con la GPU, parecen ser cada vez más herramientas inapropiadas para este trabajo.

Los participantes en varios simposios acordaron que las mejores oportunidades para un cambio significativo surgen en ausencia de características heredadas que deben ser arrastradas. La mayoría de los sistemas evolucionaron gradualmente con el tiempo, e incluso si esto garantiza un progreso seguro, dicho esquema no proporciona soluciones óptimas. Cuando aparece algo nuevo, es posible echar un nuevo vistazo a las cosas y elegir una mejor dirección que la que ofrecerán las tecnologías convencionales. Esto es exactamente lo que se discutió en una conferencia reciente, donde se estudió la cuestión de si la estructura complementaria de semiconductores de óxido de metal (

CMOS ) es la mejor tecnología básica sobre la que vale la pena construir aplicaciones de inteligencia artificial.

Un Chen, designado por IBM como Director Ejecutivo de Nanoelectronics Research Initiative (NRI), preparó el escenario para la discusión. “Durante muchos años hemos estado investigando tecnologías nuevas y modernas, incluida la búsqueda de una alternativa al CMOS, especialmente debido a sus problemas relacionados con el consumo de energía y la escala. Después de todos estos años, se ha desarrollado una opinión de que no hemos encontrado nada mejor como base para crear circuitos lógicos. Hoy, muchos investigadores se están centrando en la IA, y realmente ofrece nuevas formas de pensar y nuevos patrones, y tienen nuevos productos tecnológicos. ¿Los nuevos dispositivos de IA tendrán la capacidad de reemplazar CMOS? ”

AI hoy

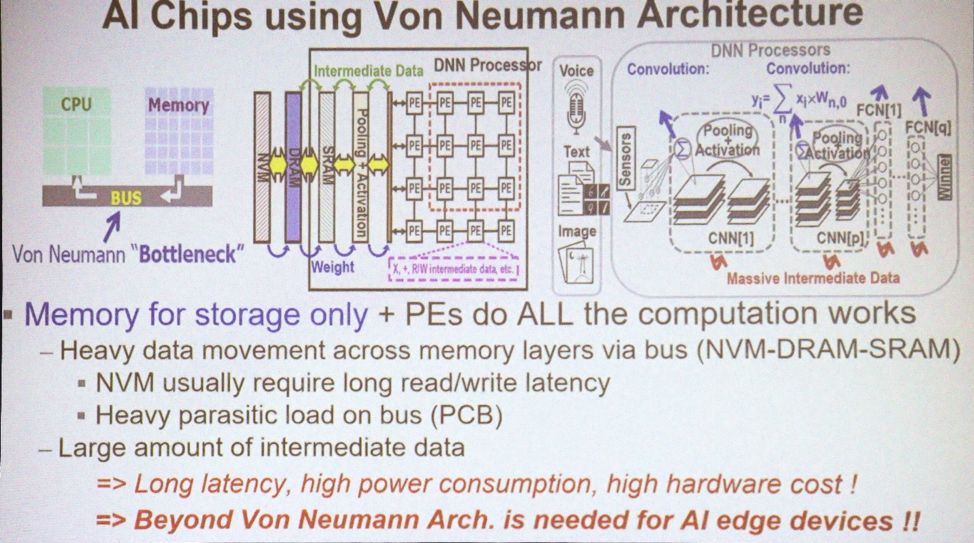

La mayoría de las aplicaciones para MO e IA usan la arquitectura von Neumann. "Utiliza la memoria para almacenar matrices de datos y la CPU realiza todos los cálculos", explica Marvin Chen, profesor de ingeniería eléctrica en la Universidad Nacional de Xinhua. “Grandes cantidades de datos se mueven a través del bus. Hoy en día, las GPU también se usan a menudo para entrenamiento en profundidad, incluidas las redes neuronales convolucionales. Uno de los principales problemas es la aparición de datos intermedios necesarios para sacar conclusiones. Mover datos, especialmente más allá del chip, da como resultado pérdidas de energía y demoras. Este es un cuello de botella tecnológico ”.

Arquitecturas utilizadas para IA

Arquitecturas utilizadas para IALo que necesita hoy es combinar el procesamiento de datos y la memoria. "El concepto de computación en memoria ha sido propuesto por expertos en arquitectura de computadoras durante muchos años", dice Chen. - Existen varios esquemas para SRAM y memoria no volátil, con los cuales trataron de usar e implementar dicho concepto. Idealmente, si esto tiene éxito, puede ahorrar una gran cantidad de energía eliminando el movimiento de datos entre la CPU y la memoria. Pero esto es ideal ".

Pero por hoy, no tenemos cálculos en mente. "Todavía tenemos AI 1.0 usando la arquitectura von Neumann, porque los dispositivos de silicio que implementan el procesamiento en la memoria nunca aparecieron", se queja. Chen "La única forma de usar 3D TSV de alguna manera es usar memoria de alta velocidad con la GPU para resolver el problema del ancho de banda". Pero sigue siendo un cuello de botella para la energía y el tiempo ".

¿Habrá suficiente procesamiento de datos en la memoria para resolver el problema de la pérdida de energía? "El cerebro humano contiene cien mil millones de neuronas y 10

15 sinapsis", dijo Sean Lee, director asistente de Taiwan Semiconductor Manufacturing Company. "Ahora mire IBM TrueNorth". TrueNorth es un procesador multinúcleo desarrollado por IBM en 2014. Tiene 4.096 núcleos y cada uno tiene 256 neuronas artificiales programables. “Supongamos que queremos escalarlo y reproducir el tamaño del cerebro. La diferencia es de 5 órdenes de magnitud. Pero si solo aumentamos directamente los números y multiplicamos TrueNorth, consumiendo 65 mW, entonces obtenemos una máquina con un consumo de 65 kW contra el cerebro de una persona que consume 25 vatios. El consumo debe reducirse en varios órdenes de magnitud ".

Lee ofrece otra forma de imaginar esta oportunidad. "La supercomputadora más eficiente hasta la fecha es la Green500 de Japón, que emite 17 Gflops por vatio, o 1

flop a 59 pJ". El sitio web de Green500 dice que el sistema ZettaScaler-2.2 instalado en el Centro de Informática y Comunicaciones Avanzadas de Japón (RIKEN) midió 18.4 Gflops / W durante la prueba de Linpack, que requirió 858 TFlops. “Compare esto con

el principio de Landauer , según el cual a temperatura ambiente la energía de conmutación mínima del transistor es del orden de 2.75 zJ [10

-21 J]. Nuevamente, la diferencia es de varios órdenes de magnitud. 59 pJ es aproximadamente 10-11 contra el mínimo teórico de aproximadamente

10-21 . Tenemos un gran campo para la investigación ".

¿Es justo comparar tales computadoras con el cerebro? "Después de examinar los éxitos recientes de la capacitación en profundidad, veremos que en la mayoría de los casos las personas y las máquinas compiten durante los últimos siete años seguidos", dice Kaushik Roy, profesor emérito de ingeniería eléctrica y ciencias de la computación en la Universidad de Purdue. "En 1997, Deep Blue derrotó a Kasparov, en 2011 IBM Watson ganó el juego Jeopardy!, Y en 2016 Alpha Go derrotó a Lee Sedola. Estos son los mayores logros. ¿Pero a qué costo? Estas máquinas consumieron 200 a 300 kW. El cerebro humano consume alrededor de 20 vatios. Enorme brecha. ¿De dónde vendrá la innovación?

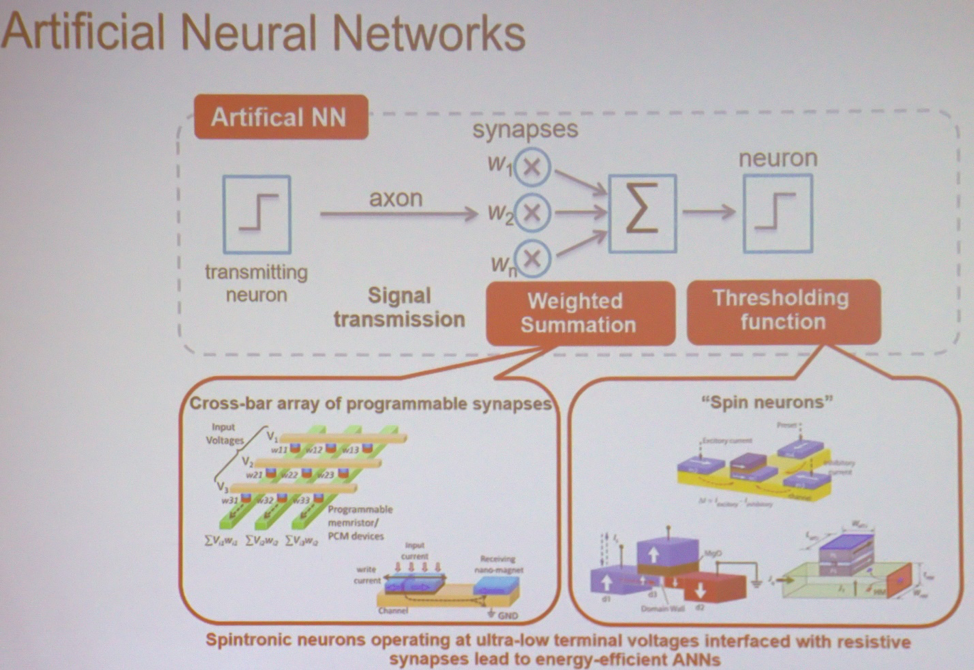

En el corazón de la mayoría de las aplicaciones, MO y AI son los cálculos más simples realizados a gran escala. "Si toma la red neuronal más simple, entonces realiza una suma ponderada, seguida de una operación de umbral", explica Roy. - Esto se puede hacer en varios tipos de matrices. Puede ser un dispositivo de spintronics o memoria resistiva. En este caso, el voltaje de entrada y la conductividad resultante se asociarán con cada punto de intersección. En la salida, obtienes la suma de los voltajes multiplicados por la conductividad. Esta es la corriente. Entonces puede tomar dispositivos similares que realizan una operación de umbral. La arquitectura se puede imaginar como un grupo de estos nodos conectados entre sí para realizar cálculos ".

Los principales componentes de la red neuronal.

Los principales componentes de la red neuronal.Nuevos tipos de memoria.

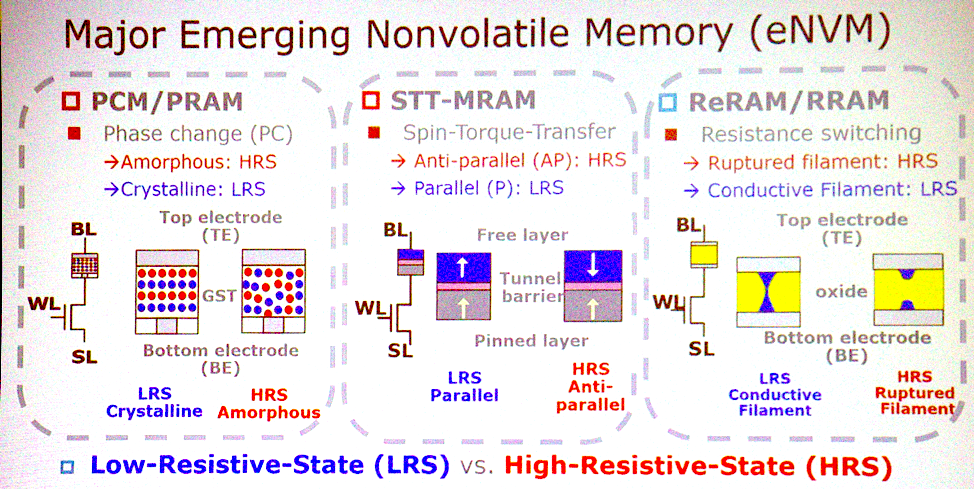

La mayoría de las arquitecturas potenciales están asociadas con tipos emergentes de memoria no volátil. "¿Cuáles son las características más importantes?" “Pregunta Jeffrey Barr, investigador de IBM Research. “Yo pondría memoria resistiva analógica no volátil, como memoria con cambio de fase, memristors, etc. La idea es que estos dispositivos puedan hacer todas las multiplicaciones para capas completamente conectadas de redes neuronales en un ciclo. En un conjunto de procesadores, esto puede llevar un millón de ciclos de reloj, y en un dispositivo analógico, esto se puede hacer utilizando la física que trabaja en la ubicación de los datos. Hay suficientes aspectos muy interesantes en términos de tiempo y energía para que esta idea se convierta en algo más ".

Nuevas tecnologías de memoria.

Nuevas tecnologías de memoria.Chen está de acuerdo con esto. “PCM, STT tiene serias ofertas para ganar. Estos tres tipos de memoria son buenos candidatos para implementar la computación en memoria. Son capaces de operaciones lógicas básicas. Algunas especies tienen problemas de confiabilidad y no pueden usarse para entrenamiento, pero es posible llegar a una conclusión ".

Pero puede resultar que no es necesario cambiar a esta memoria. "La gente habla de usar SRAM exactamente para el mismo propósito", agrega Lee. "Hacen computación analógica con SRAM". Lo único negativo es que la SRAM es demasiado grande: 6 u 8 transistores por bit. Por lo tanto, no es un hecho que usaremos estas nuevas tecnologías en computación analógica ”.

La transición a la computación analógica también implica que la precisión de los cálculos ya no será una necesidad. "La IA se especializa, clasifica y predice", dice. "Toma decisiones que pueden ser groseras". En términos de precisión, podemos renunciar a algo. Necesitamos determinar qué cálculos son resistentes a errores. Luego, se pueden aplicar algunas tecnologías para reducir el consumo de energía o acelerar la informática. El CMOS probabilístico ha estado trabajando desde 2003. Esto incluye bajar el voltaje hasta la aparición de varios errores, cuyo número sigue siendo tolerable. Hoy, las personas ya están utilizando técnicas de cálculo aproximado, como la cuantización. En lugar de un número de coma flotante de 32 bits, tendrá enteros de 8 bits. Las computadoras analógicas son otra característica ya mencionada.

Sal del laboratorio

Mover la tecnología del laboratorio al público puede ser un desafío. "A veces hay que buscar alternativas", dice Barr. - Cuando la memoria flash bidimensional no despegó, la memoria flash tridimensional comenzó a no parecer una tarea tan difícil. Si continuamos mejorando las tecnologías existentes, duplicando las características aquí, duplicando allí, entonces los cálculos analógicos dentro de la memoria serán abandonados. Pero si las siguientes mejoras resultan insignificantes, la memoria analógica se verá más atractiva. Como investigadores, debemos estar preparados para nuevas oportunidades ".

La economía a menudo desacelera el desarrollo, especialmente en el área de la memoria, pero Barr dice que esto no sucederá en este caso. “Una de nuestras ventajas es que este producto no estará relacionado con la memoria. No será algo con mejoras menores. Este no es un producto de consumo. Esto es algo que compite con la GPU. Se venden a un precio 70 veces el costo de la DRAM que se les coloca, por lo que este es claramente un producto sin memoria. Y el costo del producto no diferirá mucho de la memoria. Suena bien, pero cuando toma decisiones por valor de miles de millones de dólares, todos los costos y el plan de desarrollo del producto deben ser claros. Para superar esta barrera, necesitamos entregar prototipos impresionantes ”.

Reemplazo CMOS

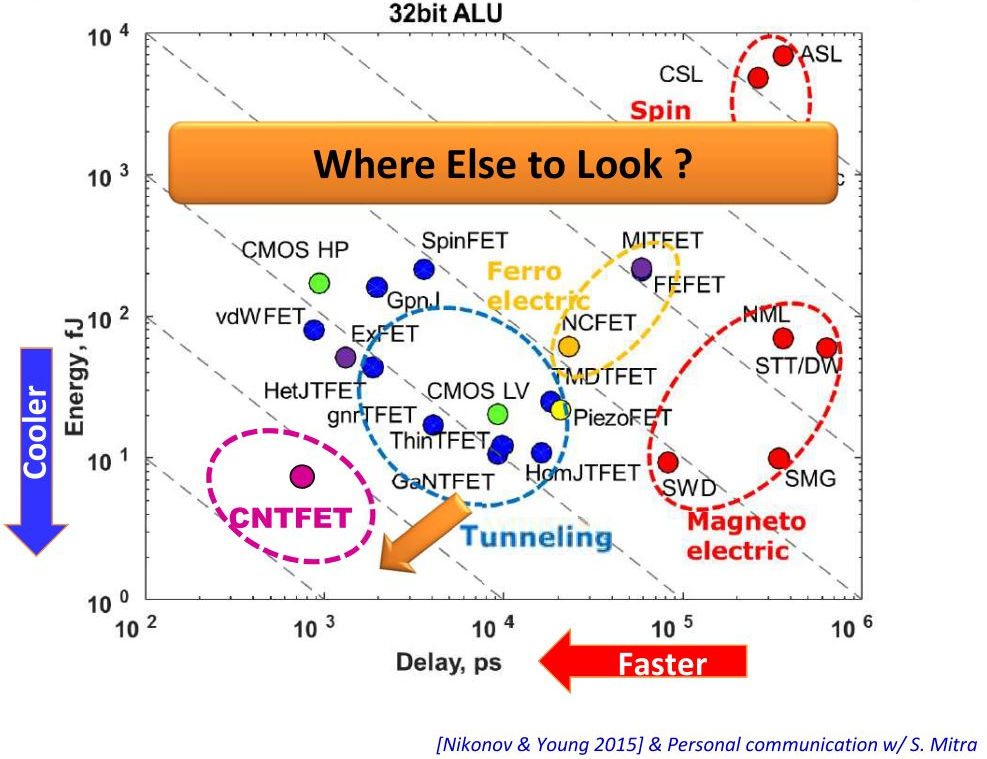

El procesamiento de datos en memoria puede proporcionar beneficios impresionantes, pero se necesita más para implementar la tecnología. ¿Puede algún otro material además de CMOS ayudar en esto? "Al observar la transición de CMOS de bajo consumo a FET de túnel, estamos hablando de una reducción del consumo de 1-2 veces", dice Lee. - Otra posibilidad son los circuitos integrados tridimensionales. Reducen la longitud del cableado con TSV. Esto reduce tanto el consumo de energía como la latencia. Mire los centros de datos, todos quitan el cableado de metal y conectan la óptica ".

Vertical - consumo de energía, horizontal - retrasos del dispositivo

Vertical - consumo de energía, horizontal - retrasos del dispositivoAunque puede lograr algunos beneficios al cambiar a una tecnología diferente, puede que no valga la pena. "Será muy difícil reemplazar CMOS, pero algunos de los dispositivos discutidos pueden complementar la tecnología CMOS para que realice cálculos en la memoria", dice Roy. - CMOS puede admitir cálculos en memoria en forma analógica, posiblemente en la celda 8T. ¿Es posible crear una arquitectura con una clara ventaja sobre CMOS? Si todo se hace correctamente, CMOS me dará miles de veces más eficiencia energética. Pero lleva tiempo.

Claramente, CMOS no reemplazará. "Las nuevas tecnologías no rechazarán las antiguas y no se realizarán en ningún sustrato que no sea CMOS", concluye Barr.