Hola

El artículo revisa la arquitectura del sistema de memoria virtual ARMv7.

Encabezado de spoilerLas sutilezas del almacenamiento en caché, DMA, LPAE y similares no se consideran aquí. Para una descripción más detallada, consulte la literatura al final del artículo.

Introduccion

El sistema de memoria virtual realiza varias tareas. En primer lugar, le permite ubicar los procesos del usuario en espacios de memoria separados y aislados entre sí. Esto le permite aumentar la confiabilidad del sistema, los errores de un proceso no afectan la operación de otros procesos. En segundo lugar, el sistema operativo puede proporcionar al proceso más memoria que la que tiene el sistema. Las páginas de memoria no utilizadas se guardan en un almacenamiento permanente, y las necesarias se cargan desde allí, formando la ilusión de una mayor cantidad de memoria de lo que realmente es. En tercer lugar, el espacio virtual continuo facilita la escritura de software personalizado. Todos los procesos se ejecutan en el mismo espacio, el sistema operativo les oculta la configuración de memoria real en el sistema.

Definiciones

Las siguientes definiciones se utilizan en el artículo:

Dirección virtual: la dirección utilizada por el núcleo del procesador. El puntero de la pila, el contador de instrucciones, el registro de retorno usan una dirección virtual.

Dirección física: la dirección de salida en el bus del procesador.

Una página es una unidad de direccionamiento de memoria virtual.

Sección: un análogo de la página, tiene un tamaño más grande.

Un marco es una unidad de direccionamiento de memoria física.

Tabla de páginas: una matriz de registros para traducir direcciones.

ASID es el identificador de espacio de direcciones.

TLB - búfer de traducción rápida de direcciones.

MMU es una unidad de gestión de memoria.

TLB

TLB es un búfer de hardware muy rápido que contiene los resultados de las últimas traducciones de direcciones. La solicitud del núcleo para traducir la dirección de la página y el ASID actual llegan al TLB. Si hay una entrada válida allí, se verifican los permisos para acceder a esta memoria, el método de acceso y la dirección de trama correspondiente se devuelven a la MMU. Si se deniega el acceso a la memoria, se genera una excepción de hardware. Si se produjo un error de TLB (no se encontró ningún registro), TTBCR distingue entre mayúsculas y minúsculas. Se puede realizar una búsqueda en las tablas de páginas o se genera una excepción.

Es importante tener en cuenta que al manipular tablas de páginas, debe restablecer correctamente el TLB, porque la información irrelevante puede almacenarse allí.

La actualización de entradas en el TLB es transparente para el programador round-robin.

También es posible cargar y asegurar algunas entradas en el TLB para evitar su desplazamiento.

Figura 1. TLB

Figura 1. TLBTablas de página

ARMv7 es una arquitectura de 32 bits, por lo que tenemos 4 GB de memoria virtual direccionable.

Las tablas de páginas se dividen en 2 niveles: L1 y L2.

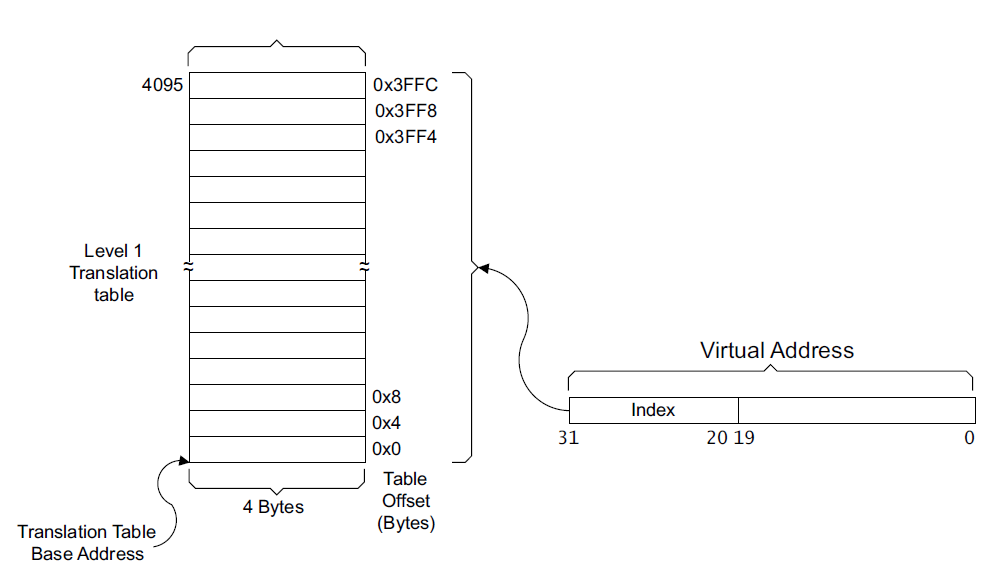

La Tabla L1 describe los 4 GB de espacio de direcciones. Se compone de 4096 registros de 32 bits, cada uno de los cuales describe 1 Mb. Las entradas en la tabla son seleccionadas por los 12 bits altos de la dirección virtual.

Fig. 2 Buscar entradas en la tabla L1

Fig. 2 Buscar entradas en la tabla L1La tabla L1 se encuentra en la memoria física y está alineada con un borde de 16 KB. Hay 4 opciones para estas entradas: para describir páginas, secciones y supersecciones. Bueno, un registro vacío, para la memoria que aún no está asignada.

Fig. 3 tipos de entradas en L1

Fig. 3 tipos de entradas en L1Los bits 0 y 1 indican el tipo de registro 00b-Fault, 01b es el descriptor de página, 10b es el descriptor de sección (y la supersección).

Si la memoria física está paginada, entonces la tabla L1 almacena la dirección de la tabla L2 (física, alineada a 1Kb). El fabricante determina el bit 9 (implementación definida), bits [8: 5] - para el mecanismo de dominio (obsoleto en ARMv7), SBZ - ceros.

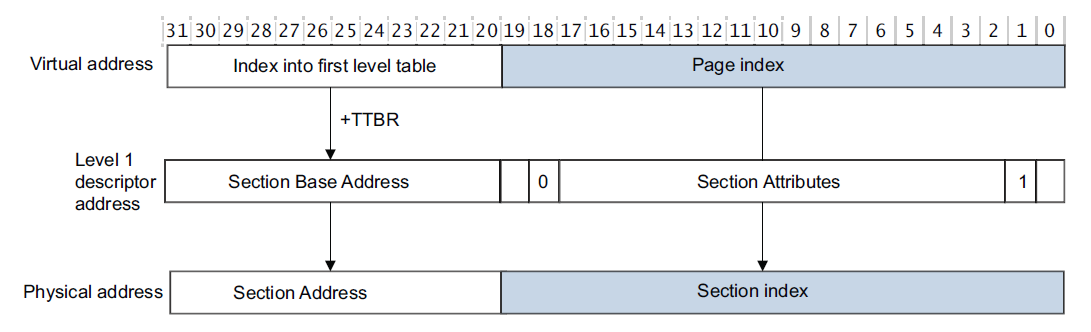

Si decidimos dividir la memoria en secciones, entonces en L1 es necesario escribir la dirección física correspondiente. La sección se refiere directamente al área de memoria física alineada de 1 MB. No hay necesidad de la tabla L2. La sustitución es un caso especial de particionamiento, la entrada en la tabla L1 debe repetirse 16 veces, la alineación de los bloques asignados de memoria física y virtual también es de 16 MB.

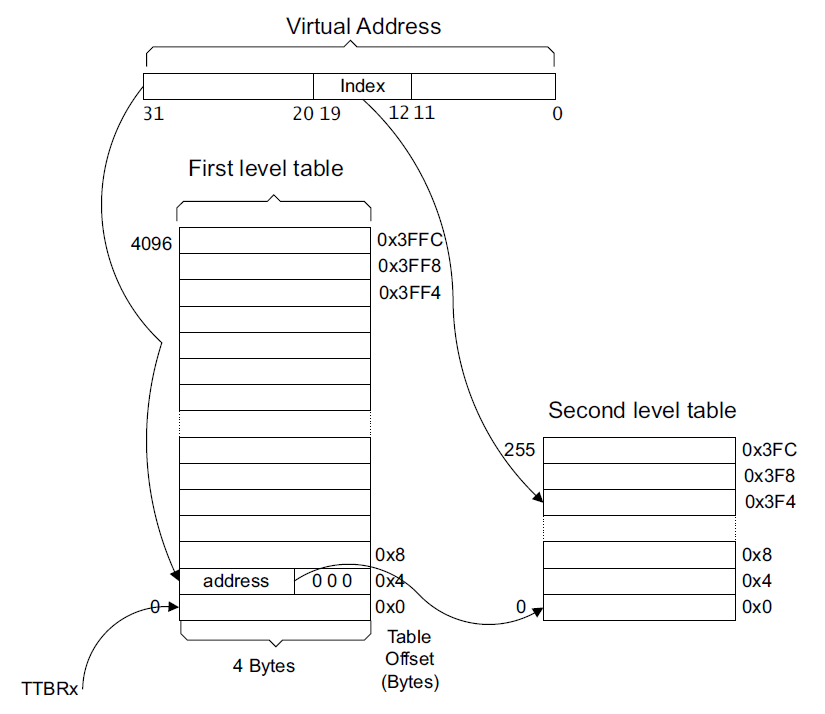

La tabla L2 consta de 256 entradas de 32 bits. Debe estar alineado a 1Kb.

Fig. 4 Buscar entradas en la tabla L2

Fig. 4 Buscar entradas en la tabla L2Los índices en la tabla L2 se forman a partir del promedio de 8 bits [19:12] de la dirección virtual. Cada entrada de la tabla contiene la dirección del marco.

Fig. 5 tipos de entradas en L2

Fig. 5 tipos de entradas en L2Las páginas pueden ser de dos tamaños: 64 Kb (página grande) y 4Kb (página pequeña).

Los bits AP y APX establecen permisos de lectura / escritura en modo privilegiado / no privilegiado (kernel / usuario). Los bits TEX, C, B, S son responsables del tipo de memoria, su almacenamiento en caché y el almacenamiento en búfer de lectura y escritura. El bit nG - no Global permite el acceso a la página para todos los procesos o solo para un ASID específico.

El uso de páginas grandes reduce el número de entradas en el TLB. En lugar de 16 entradas (4Kb * 16 = 64Kb), solo una se almacenará allí. Sin embargo, se deben ingresar 16 entradas idénticas en la tabla L2.

La capacidad de abordar diferentes tamaños de bloques permite, por un lado, asignar memoria con la granularidad deseada, por otro lado, reducir el número de llamadas a tablas de páginas en una memoria relativamente lenta.

Registros

Para controlar el sistema (incluida la MMU) en la arquitectura ARM, se diseña un coprocesador CP15 especial. Para la gestión de memoria hay una docena y media de sus registros. Estamos interesados en varios de ellos: Control, TTBR0 / 1, TTBCR, ContextID.

En el registro de Control, el bit menos significativo es responsable de encender / apagar la MMU, todo es simple.

El par de registros TTBR0 / 1 contiene las direcciones físicas de las tablas del primer nivel. En estas direcciones, la MMU comienza a buscar la página deseada.

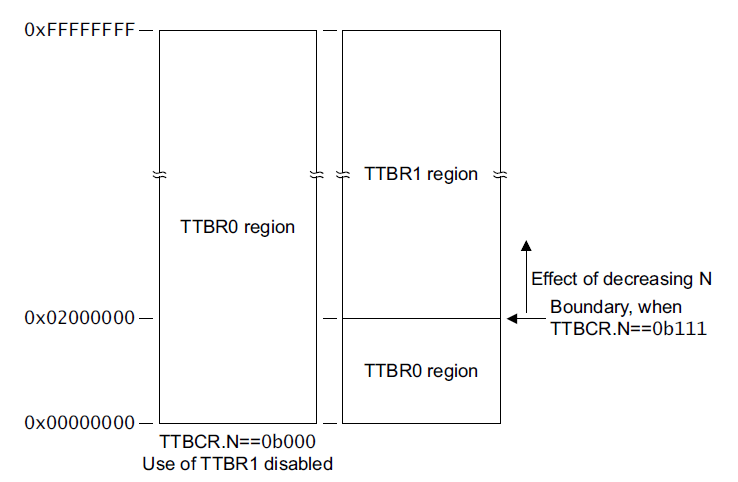

El registro TTBCR le permite dividir todo el espacio de direcciones en 2 partes entre TTBR0 y TTBR1. Cada uno de ellos transmitirá su parte de las direcciones. Los bits [2: 0] se utilizan para establecer el tamaño. El número registrado (de 0 a 7 decimales) enmascara la parte más antigua de las direcciones virtuales. Si su valor es "0", todas las direcciones se transmiten a través de TTBR0. Si "1", las direcciones de 31 bits están enmascaradas y los 2 GB más bajos de espacio virtual pasan a través de TTBR0, los superiores a través de TTBR1. "2": se enmascaran 31 y 30 bits y se obtiene la división en 1 GB y 3 GB, respectivamente. Por lo tanto, la parte inferior de las direcciones se puede usar para aplicaciones de usuario, sobrecargando el registro TTBR0 para un nuevo proceso, y la parte superior se puede dejar para las necesidades del sistema.

Fig. 6 espacio de direcciones dividido

Fig. 6 espacio de direcciones divididoLos bits [5: 4] son responsables del comportamiento de falta de TLB: busque en tablas de páginas o una excepción.

El registro ContextID contiene el campo ASID para el proceso actual. Debe cambiarse junto con el contenido del registro TTBR0 al cambiar el contexto.

Traducción de direcciones

El algoritmo para convertir direcciones virtuales a físicas es el siguiente:

- Busque la dirección virtual solicitada y el ASID en el búfer TLB

- Si el TLB no tiene la dirección requerida, se realiza una búsqueda de hardware en las tablas de páginas

Si el núcleo solicitó previamente una página virtual, se almacena en el TLB. En este caso, la MMU lo saca del caché y no se necesita hacer nada. Si la página se solicita por primera vez (o si se forzó a salir de allí, el TLB no es muy grande), se realiza la búsqueda en las tablas L1-L2. Por lo tanto, la asignación de las direcciones virtuales y físicas es la siguiente:

- En el registro TTBR0 \ TTBR1, se busca la dirección de la tabla L1.

- Los 10 bits superiores de la dirección virtual forman un índice en la tabla.

- a) Si el registro corresponde a la sección (supersección), se verifican los atributos de la sección y, si todo está bien, la dirección física resultante se compone de la dirección base de la sección (supersección) y los 20 (24) bits inferiores de la dirección virtual.

Encabezado de spoiler Fig. 7 Traducción de direcciones en supersección

Fig. 7 Traducción de direcciones en supersección

b) Si el registro es una tabla L2, la búsqueda continúa en él. La parte central de la dirección virtual de la página forma el índice de la tabla.

Encabezado de spoiler Fig. 8 Traducción de direcciones en la Tabla L2

Fig. 8 Traducción de direcciones en la Tabla L2

- Actualización de TLB en progreso

En total, el subsistema de memoria virtual consta de las siguientes partes:

- Múltiples registros de control CP15

- Tablas de páginas que contienen reglas de traducción de direcciones

- TLB: caché de transmisiones exitosas

- MMU es una unidad de traducción de direcciones.

Literatura

Manual de referencia de arquitectura ARM Edición ARMv7-A y ARMv7-R

Guía del programador de la serie ARM Cortex-A