Tecnologías microelectrónicas modernas, como "Diez pequeños indios". El costo de desarrollo y equipamiento es tan grande que con cada nuevo paso hacia adelante, alguien se cae. Después de la noticia de que GlobalFoundries se negó a desarrollar 7 nm, quedaron tres de ellos: TSMC, Intel y Samsung. ¿Y qué son exactamente los "estándares de diseño" y dónde está ese tamaño tan apreciado de 7 nm? ¿Y está él allí en absoluto?

Figura 1. Transistor Fairchild FI-100, 1964.Los primeros transistores MOS seriales entraron al mercado en 1964 y, como los lectores sofisticados pueden ver en el dibujo,

casi no eran diferentes de los más o menos modernos, excepto por el tamaño (mire el cable para ver la escala).

¿Por qué reducir el tamaño de los transistores? La respuesta más obvia a esta pregunta se llama la ley de Moore y establece que cada dos años el número de transistores en un chip debe duplicarse, lo que significa que las dimensiones lineales de los transistores deberían disminuir en un factor de dos. "Debe" - según las observaciones de Gordon Moore (y algunos otros ingenieros) en los años setenta. Según la Ley de Moore, hay muchos otros factores que componen la hoja de ruta de microelectrónica de ITRS. La formulación más simple y dura de los métodos para implementar la ley de Moore (también conocida como la ley de miniaturización de Dennard) es que un aumento en el número de transistores en un chip no debería conducir a un aumento en la densidad del consumo de energía, es decir, con una disminución en el tamaño de los transistores, el voltaje de suministro y la corriente de operación deberían reducirse proporcionalmente.

La corriente a través del transistor MOS es proporcional a la relación de su ancho a la longitud, lo que significa que podemos mantener la misma corriente, reduciendo proporcionalmente ambos parámetros. Además, al reducir el tamaño del transistor, también reducimos la capacitancia de la puerta (proporcional al producto de la longitud y el ancho del canal), haciendo que el circuito sea aún más rápido. En general, en un circuito digital prácticamente no hay razón para hacer que los transistores sean más grandes que el tamaño mínimo. A continuación, comienzan los matices de que, en la lógica, los transistores de canal p suelen ser ligeramente más anchos que los de canal n para compensar la diferencia en la movilidad de los portadores de carga, y en la memoria, por el contrario, los transistores de canal n son más anchos para que la memoria pueda escribirse normalmente a través de una tecla no complementaria, pero realmente matices, y globalmente, cuanto más pequeño es el tamaño del transistor, mejor para los circuitos digitales.

Es por eso que la longitud del canal siempre ha sido el tamaño más pequeño en la topología del microcircuito, y la designación de designación más lógica.

Cabe señalar aquí que el razonamiento anterior sobre el tamaño no es válido para circuitos analógicos. Por ejemplo, en este momento en el segundo monitor de mi computadora hay un par de transistores combinados que usan tecnología de 150 nm, 32 piezas de 8/1 micras de tamaño. Esto se hace para asegurar la identidad de estos dos transistores, a pesar de la variación tecnológica de los parámetros. El área es de importancia secundaria.Los tecnólogos y topólogos tienen el llamado sistema lambda de tamaños de topología típicos. Es muy conveniente para estudiar diseño (y fue inventado en la Universidad de Berkeley, si no me equivoco) y transferir diseños de fábrica a fábrica. De hecho, esta es una generalización de los tamaños típicos y las limitaciones tecnológicas, pero un poco áspera, por lo que funciona exactamente en cualquier fábrica. En su ejemplo, es conveniente observar los tamaños típicos de los elementos en el chip. Los principios básicos del sistema lambda son muy simples:

- Si el desplazamiento de elementos en dos máscaras fotolitográficas diferentes tiene consecuencias catastróficas (por ejemplo, un cortocircuito), entonces el margen de tamaño para evitar inconsistencias debe ser de al menos dos lambdas;

- si el cambio de elementos tiene consecuencias indeseables, pero no catastróficas, el margen de tamaño debe ser al menos una lambda;

- El tamaño mínimo permitido de las ventanas de la máscara de fotos es de dos lambdas.

Del tercer párrafo se deduce, en particular, que lambda en tecnologías antiguas es la mitad de la norma de diseño (más precisamente, la longitud del canal del transistor y las normas de diseño son dos lambdas).

Figura 2. Un ejemplo de una topología realizada por un sistema lambda.El sistema lambda funcionó perfectamente en los viejos estándares de diseño, permitiéndole transferir convenientemente la producción de fábrica a fábrica, organizar proveedores de segundo chip y hacer cosas mucho más útiles. Pero con el aumento de la competencia y la cantidad de transistores en un chip, las fábricas comenzaron a esforzarse por hacer que la topología sea un poco más compacta, por lo que ahora no puede cumplir con las reglas de diseño correspondientes a un sistema lambda "limpio", excepto en situaciones en las que los desarrolladores los enfatizan independientemente, teniendo en cuenta la probabilidad de producción chip en diferentes fábricas. Sin embargo, a lo largo de los años, la industria ha desarrollado una conexión directa "estándares de diseño = longitud del canal del transistor", que existió con éxito hasta que los transistores alcanzaron decenas de nanómetros.

Figura 3. Sección esquemática del transistor.Esta figura muestra una sección MUY simplificada de un transistor plano (plano) convencional, que muestra la diferencia entre la longitud del canal topológico (Ldrawn) y la longitud efectiva del canal (Leff). ¿De dónde viene la diferencia?

Hablando de tecnología microelectrónica, la fotolitografía casi siempre se menciona, pero con mucha menos frecuencia son otras operaciones tecnológicas no menos importantes: grabado, implantación de iones, difusión, etc. etc. Para nuestra conversación con usted, un recordatorio de cómo funcionan la difusión y la implantación de iones no es superfluo.

Figura 4. Comparación de difusión e implantación de iones.Con difusión, todo es simple. Se toma una oblea de silicio sobre la cual se aplica de antemano (con la ayuda de la fotolitografía) un dibujo que cubre con óxido de silicio aquellos lugares donde no se necesita la impureza y se abren aquellos donde se necesita. A continuación, debe colocar la impureza gaseosa en la misma cámara con el cristal y calentar a una temperatura a la que la impureza comience a penetrar en el silicio. Al ajustar la temperatura y la duración del proceso, es posible lograr la cantidad y profundidad de impurezas deseadas.

La desventaja obvia de la difusión es que la impureza penetra en el silicio en todas las direcciones de la misma manera, hacia abajo, en ese lado, reduciendo así la longitud efectiva del canal. ¡Y ahora estamos hablando de cientos de nanómetros! Si bien los estándares de diseño se midieron en decenas de micras, todo estaba bien, pero, por supuesto, este estado de cosas no podía durar mucho y la difusión se reemplazó por la implantación de iones.

Durante la implantación de iones, un haz de iones de impurezas se acelera y se dirige a una oblea de silicio. En este caso, todos los iones se mueven en una dirección, lo que prácticamente elimina su propagación hacia los lados. En teoría, por supuesto. Sin embargo, en la práctica, los iones se separan un poco, aunque a distancias mucho más cortas que durante la difusión.

Sin embargo, si volvemos al patrón del transistor, veremos que la diferencia entre la longitud del canal topológica y efectiva comienza precisamente debido a este pequeño desplazamiento. Ella, en principio, podría ser descuidada, pero no es la única razón de la diferencia. Todavía hay efectos de canal corto. Hay cinco de ellos, y de varias maneras cambian los parámetros del transistor si la longitud del canal se acerca a varias restricciones físicas. No los describiré a todos, me detendré en lo más relevante para nosotros: DIBL (reducción de la barrera inducida por drenaje, disminución inducida por drenaje en la barrera potencial).

Para ingresar al sumidero, un electrón (o agujero) debe superar la barrera potencial de la unión pn del sumidero. El voltaje de la puerta reduce esta barrera, controlando así la corriente a través del transistor, y queremos que el voltaje de la puerta sea el único voltaje de control. Desafortunadamente, si el canal del transistor es demasiado corto, la unión pn de drenaje comienza a influir en el transistor, lo que, en primer lugar, reduce el voltaje de poro (ver la figura a continuación), y en segundo lugar, el voltaje a través del transistor comienza a afectar no solo el voltaje de la puerta , pero también en el drenaje, porque el grosor de la unión pn del drenaje aumenta en proporción al voltaje en el drenaje y, en consecuencia, acorta el canal.

Figura 5. Efecto de reducción de barrera inducida por drenaje (DIBL).

Fuente - Wikipedia.Además, una disminución en la longitud del canal lleva al hecho de que los portadores de carga comienzan a pasar libremente de la fuente al desagüe, evitando el canal y generando una corriente de fuga (mala corriente en la figura a continuación), que también es consumo de energía estática, cuya ausencia fue una de las razones importantes para el éxito temprano de CMOS -tecnologías, más bien inhibitorias en comparación con los competidores bipolares de la época. De hecho, cada transistor en la tecnología moderna tiene una resistencia paralela, cuyo valor es cuanto menor es la longitud del canal.

Figura 6. El aumento en el consumo estático debido a fugas en las tecnologías de canales cortos.

Fuente - Sinopsis.Figura 7. La proporción del consumo de energía estática de los microprocesadores en diferentes estándares de diseño.

Fuente - B. Dieny et. al., "Efecto de transferencia de espín y su uso en componentes espintrónicos", International Journal of Nanotechnology, 2010Ahora, como puede ver en la figura anterior, el consumo estático excede significativamente el dinámico y es un obstáculo importante para crear circuitos de baja potencia, por ejemplo, para dispositivos electrónicos portátiles e Internet de las cosas. En realidad, aproximadamente en el momento en que esto se convirtió en un problema importante, comenzó la comercialización de muhlezh con estándares de diseño, porque el progreso en la litografía comenzó a superar el progreso en la física.

Para combatir los efectos indeseables del canal corto en los estándares de diseño de 800-32 nanómetros, se inventaron muchas soluciones tecnológicas diferentes, y no las describiré todas, de lo contrario el artículo crecerá a tamaños muy indecentes, pero con cada nuevo paso tuve que introducir nuevas soluciones - adicionales dopaje de áreas adyacentes a uniones pn, dopado en profundidad para evitar fugas, transformación local de silicio en transistores en silicio-germanio ... No se hizo un solo paso para reducir el tamaño de los transistores. oh asi

Figura 8. La longitud efectiva del canal en tecnologías de 90 nm y 32 nm. Los transistores se disparan a la misma escala. Los semicírculos en las figuras son una forma de emparejamiento débil adicional de drenajes (LDD, drenaje ligeramente dopado), hecho para reducir el ancho de las uniones pn.

Fuente - Sinopsis.Los tamaños de metalización típicos y las distancias entre elementos durante la transición de 90 nm a aproximadamente 28 nm disminuyeron en proporción a una disminución en el código de diseño, es decir, el tamaño típico de la próxima generación fue 0.7 del anterior (de modo que, según la ley de Moore, para obtener una reducción de dos veces en el área). Al mismo tiempo, la longitud del canal disminuyó en el mejor de los casos a 0.9 de la generación anterior, y la longitud efectiva del canal prácticamente no cambió en absoluto. Se ve claramente en la figura anterior que las dimensiones lineales de los transistores no cambiaron tres veces en absoluto de 90 nm a 32 nm, y todos los juegos de los tecnólogos se centraron en reducir la superposición del obturador y las áreas dopadas, así como alrededor del control de fugas estáticas, que no se permitieron. El canal es más corto.

Como resultado, dos cosas quedaron claras:

- ir por debajo de 25-20 nm sin un avance tecnológico no funciona;

- Se ha vuelto cada vez más difícil para los vendedores pintar una imagen del progreso de la tecnología con la ley de Moore.

La ley de Moore es generalmente un tema controvertido, porque no es una ley de la naturaleza, sino una observación empírica de algunos hechos de la historia de una empresa en particular, extrapolada al progreso futuro de toda la industria. En realidad, la popularidad de la ley de Moore está indisolublemente ligada a los especialistas en marketing de Intel, quienes la convirtieron en su bandera y, de hecho, impulsaron a la industria hacia adelante durante muchos años, obligándola a cumplir con la ley de Moore donde, quizás, valdría la pena esperar un poco.¿Cuál es la forma en que los vendedores descubrieron la situación? Muy elegante

La longitud del canal del transistor es buena, pero ¿cómo puede estimar la ganancia en el área a partir de él, lo que da la transición a nuevos estándares de diseño? Hace bastante tiempo, la industria usaba el área de una celda de memoria de seis transistores, el bloque de construcción de microprocesador más popular. Son estas celdas que generalmente consisten en una memoria caché y un archivo de registro que pueden ocupar medio cristal, y es por eso que el esquema y la topología de una celda de seis transistores siempre se lamen cuidadosamente hasta el límite (a menudo personas especiales que hacen esto), por lo que esta es una muy buena medida Densidad de embalaje.

Figura 9. Esquema de una celda de memoria estática de seis transistores.Figura 10. Diferentes opciones de topología para una celda de memoria estática de seis transistores. Fuente - G. Apostolidis et. al., "Diseño y simulación de arquitecturas de células SRAM 6T en tecnología de 32 nm", Journal of Engineering Science and Technology Review, 2016Por lo tanto, durante mucho tiempo en las descripciones de las tecnologías, el número de estándares de diseño estuvo acompañado por la segunda figura: el área de la celda de memoria, que, en teoría, debería derivarse de la longitud del canal. Y luego hubo una interesante sustitución de conceptos. En un momento en que el escalado directo dejó de funcionar y la longitud del canal dejó de disminuir cada dos años de acuerdo con la ley de Moore, ¡los especialistas en marketing adivinaron que era posible no derivar el área de la celda de memoria de las normas de diseño, sino deducir el número de normas de diseño del área de la celda de memoria!

Es decir, naturalmente “antes teníamos una longitud de canal de 65 nm y un área de celda de memoria de X, y ahora la longitud del canal es de 54 nm, pero exprimimos la metalización, y ahora el área de celda se ha convertido en X / 5, que corresponde aproximadamente a una transición de 65 a 28 nm. Entonces, ¿podemos decirle a todos que tenemos estándares de diseño de 28 nm y que no le diremos a nadie sobre la longitud del canal de 54 nm? Para ser justos, la "metalización punzante" también es un logro importante, y durante algún tiempo después del comienzo de los problemas con la miniaturización de los propios transistores, el ancho mínimo de metalización, el tamaño del contacto con el transistor o alguna otra figura en la topología correspondió con los estándares de diseño establecidos. Pero luego los bailes comenzaron con los transistores FinFET, en los que las dimensiones clave no tenían nada que ver con la resolución de la litografía, las tasas de miniaturización de los transistores y todo lo demás finalmente divergieron, y el área de la celda de memoria siguió siendo la única figura normal, sobre la base de la cual ahora se nos informa sobre "10", " 7 "y" 5 "nanómetros.

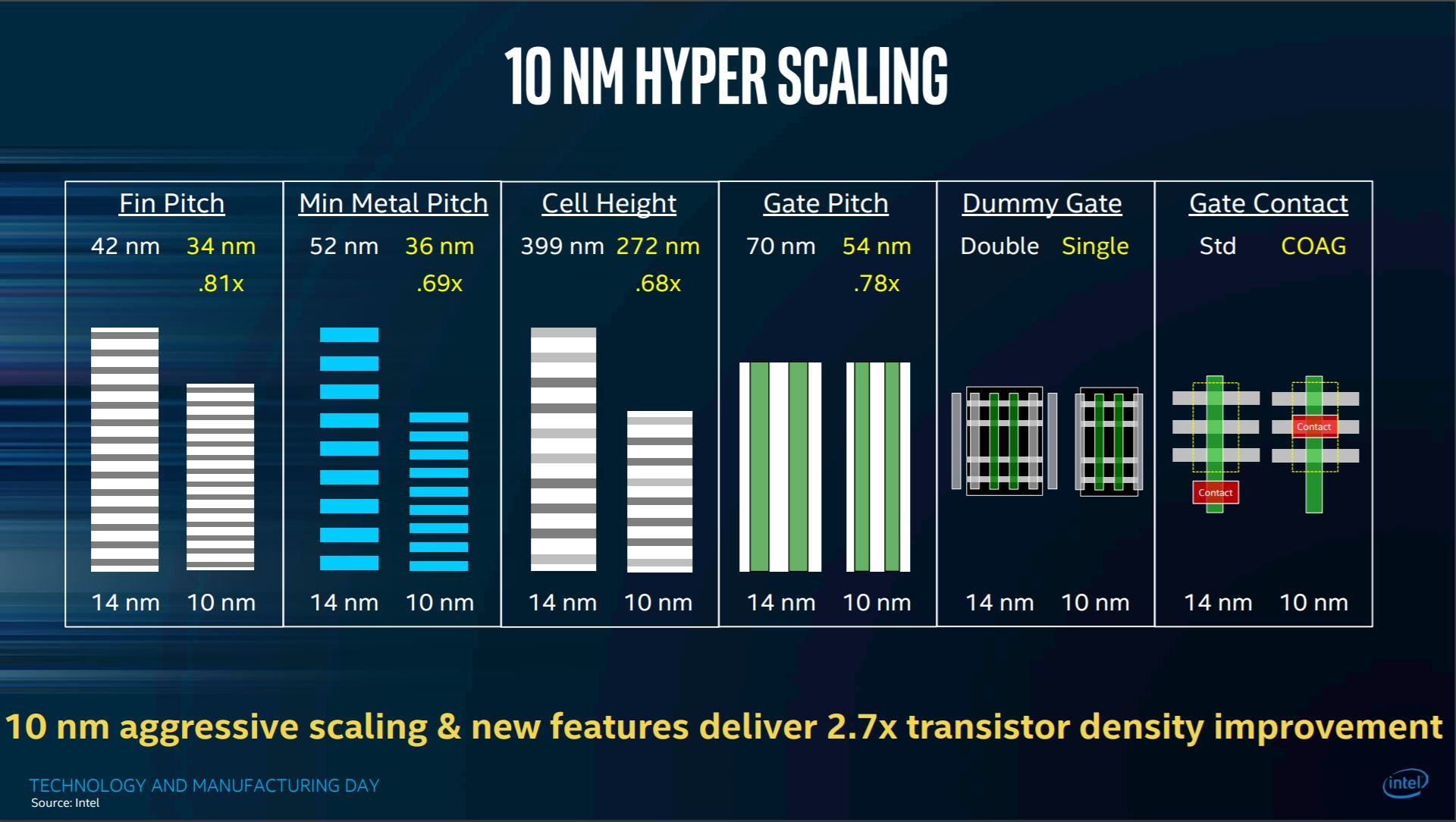

Fuente: Intel.Aquí hay un gran ejemplo de esta "nueva escala". Se nos muestra cómo han cambiado los tamaños característicos en la celda de memoria. ¡Muchos parámetros, pero ni una palabra sobre la longitud y el ancho del canal del transistor!

¿Cómo resolvieron el problema de la imposibilidad de reducir la longitud del canal y controlar la pérdida de tecnología?

Encontraron dos formas. El primero está en la frente: si la causa de las fugas es una gran profundidad de implantación, reduzcamosla, preferiblemente radicalmente. La tecnología de silicio en un aislador (SIC) se conoce desde hace mucho tiempo (y se ha utilizado activamente durante todos estos años, por ejemplo, en procesadores AMD de 130-32 nm, procesador de decodificador Sony Playstation 3 de 90 nm, así como en radiofrecuencia, potencia o electrónica espacial), pero Con una disminución en los estándares de diseño, tuvo un segundo viento.

Figura 12. Comparación de los transistores realizados con tecnologías volumétricas convencionales y FDSOI (SOI totalmente agotado).

Fuente - ST Microelectronics .Como puede ver, la idea es más que elegante: ¡el óxido se encuentra debajo de una capa activa muy delgada, eliminando la corriente de fuga dañina en la vid! Al mismo tiempo, debido a una disminución en la capacidad de las uniones pn (se eliminaron cuatro de los cinco lados del cubo de drenaje), la velocidad aumenta y el consumo de energía disminuye. Es por eso que ahora la tecnología FDSOI 28-22-20 nm se anuncia activamente como una plataforma para Internet de microchips de cosas: el consumo se reduce realmente varias veces, si no por un orden de magnitud. Y, sin embargo, este enfoque permite en el futuro escalar el transistor plano convencional a un nivel de 14-16 nm, que la tecnología volumétrica ya no permitirá.

Sin embargo, FDSOI no cae especialmente por debajo de 14 nm, y la tecnología también tiene otros problemas (por ejemplo, el terrible alto costo de los sustratos SOI), en relación con los cuales la industria llegó a otra solución: los transistores FinFET. La idea de un transistor FinFET también es bastante elegante. ¿Queremos que la mayor parte del espacio entre el drenaje y la fuente sea controlada por el obturador? ¡Así que rodeemos este espacio con un obturador en todos los lados! Bueno, no todos, tres serán suficientes.

Figura 13. Estructura FinFET.

Fuente: A. Tahrim et.al., "Diseño y análisis de rendimiento de células de sumador completo FinFET de 1 bit para la región del umbral inferior a la tecnología de proceso de 16 nm", Journal of Nanomaterials, 2015Figura 14. Comparación del consumo de energía de diferentes opciones de sumador realizadas en transistores planos y en FinFET.

Fuente: A. Tahrim et.al., "Diseño y análisis de rendimiento de células de sumador completo FinFET de 1 bit para la región del umbral inferior a la tecnología de proceso de 16 nm", Journal of Nanomaterials, 2015En FinFET, el canal no es plano y está ubicado directamente debajo de la superficie del sustrato, sino que forma una aleta vertical (Fin es la aleta), que sobresale por encima de la superficie y está rodeada por un obturador en tres lados. Por lo tanto, todo el espacio entre el drenaje y la fuente está controlado por un obturador, y las fugas estáticas se reducen considerablemente. Los primeros FinFET que se produjeron en serie fueron Intel con estándares de diseño de 22 nm, el resto fueron retirados por otros fabricantes importantes, incluido un apologista de KNI como Global Foundries (ex AMD).

La verticalidad del canal en FinFET, entre otras cosas, le permite ahorrar en el área de la celda, porque FinFET con un canal ancho es bastante estrecho en proyección, y esto, a su vez, ayudó nuevamente a los especialistas en marketing con sus historias sobre el área de la celda de memoria y su doble disminución con cada nueva paso "estándares de diseño", ya no está vinculado a las dimensiones físicas del transistor.Figura 15. Topologías de diferentes opciones para celdas de memoria (5T-9T) en tecnología con FinFET. Fuente - M. Ansari et. al., "Una celda SRAM 7T de umbral cercano con altos márgenes de escritura y lectura y bajo tiempo de escritura para tecnologías FinFET de menos de 20 nm", VLSI Journal on Integration, Volumen 50, junio de 2015.Aquí hay ejemplos de diferentes opciones para celdas de memoria en la tecnología con FinFET. ¿Ves cómo el ancho geométrico del canal es mucho más pequeño que la longitud? También puede ver que, a pesar de todas las perturbaciones, el sistema lambda entre los topólogos todavía se usa para estimaciones cuantitativas. ¿Y qué hay de los números absolutos?Figura 16. Algunos tamaños de transistores en tecnologías de 14-16 nm.

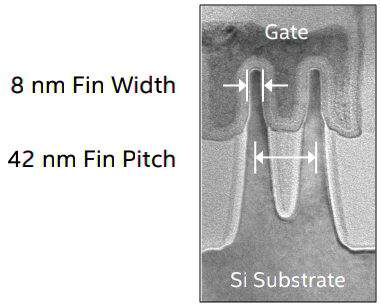

Fuente: actas de la conferencia ConFab 2016.Como se puede ver en la figura, la longitud del canal topológico en las tecnologías FinFET de 16 nm es aún mayor que 20-25 nm, que se mencionaron anteriormente. Y esto es lógico, porque la física no puede ser engañada. Pero otra conclusión más interesante se puede extraer de la misma figura: si se mira de cerca, queda claro que el tamaño mínimo disponible en los transistores no es la longitud del canal, sino el ancho de la aleta. Y aquí nos espera un descubrimiento divertido: el ancho de la aleta en la tecnología de proceso Intel de 16 nm es (¡tambor!) OCHO nanómetros. Figura 17. Dimensiones de la aleta en la tecnología de proceso Intel de 14 nm.

Figura 17. Dimensiones de la aleta en la tecnología de proceso Intel de 14 nm.

Fuente - wikichip.orgComo puede ver, aquí los especialistas en marketing, vinculados al tamaño de la celda de memoria, se engañaron a sí mismos y ahora se ven obligados a expresar la cifra más de lo que podrían. De hecho, por supuesto, en condiciones de un cambio fundamental en la estructura del transistor y la expectativa de los usuarios de escuchar algún tipo de métrica, el uso de una métrica que refleje la densidad de empaque fue probablemente la única decisión correcta, y los vendedores en última instancia tenían razón, aunque esto a veces conduce a situaciones divertidas cuando los mismos estándares de diseño en diferentes compañías se llaman de manera diferente. Por ejemplo, al leer las noticias de que TSMC ya lanzó 7 nm e Intel está demorando nuevamente el inicio de la producción de 10 nm, vale la pena recordar que TSMC de 7 nm y Intel de 10 nm son en realidad los mismos estándares de diseño en términos de y densidad de empaque, y el tamaño de los transistores individuales.Que sigue

De hecho, nadie lo sabe. La ley de Moore se ha agotado hace bastante tiempo, y si hace diez años la respuesta a la pregunta "¿qué sigue?" podría encontrarse en los informes de los centros de investigación, ahora se escucha cada vez más que los desarrollos prometedores deben abandonarse, ya que resultan ser excesivamente difíciles de implementar. Esto ya ha sucedido con las obleas con un diámetro de 450 milímetros, esto es en parte el caso de la litografía EUV (que los científicos solían recorrer durante veinte años), y esto probablemente sucederá con los transistores en grafeno y nanotubos de carbono. Se necesita otro avance tecnológico, pero el camino hacia él, lamentablemente, aún no es visible. Llegó al punto en que el nuevo director de TSMC Mark Liu llamóLa dirección más prometedora en el desarrollo de la tecnología microelectrónica no es la reducción del tamaño de los transistores, sino la integración 3D. La integración 3D "verdadera", en lugar de combinar varios chips en un paquete, será un gran hito en el desarrollo de la microelectrónica, pero la ley de Moore como la ley de reducir el tamaño de los transistores parece haber muerto por completo.