Quad Data Rate (QDR-IV) es un estándar de memoria de alto rendimiento para aplicaciones de red y es ideal para la próxima generación de dispositivos de red, equipos de comunicaciones y sistemas informáticos.

QDR-IV SRAM tiene una unidad de detección y corrección de errores (ECC) incorporada para garantizar la integridad de los datos. Esta unidad es capaz de procesar todos los errores de memoria de un solo bit, incluidos los causados por los rayos cósmicos y las partículas alfa. Como resultado, los módulos de memoria tendrán una tasa de error de programa (SER) de no más de 0.01 fallas / MB. QDR-IV está equipado con una función de paridad de dirección programable que garantiza la integridad de los datos en el bus de direcciones.

Características distintivas de la memoria QDR SRAM:

- El módulo de corrección de errores integrado garantiza la integridad de los datos y elimina los errores de software.

- Los módulos están disponibles en dos versiones: QDR-IV HP (velocidad de datos 1334 Mtrans / s) y QDR-IV XP (velocidad de datos 2132 Mtrans / s)

- Dos puertos de datos de memoria DDR1 bidireccionales independientes

- Función de inversión de bus para reducir el ruido al conectar las líneas de entrada y salida

- El esquema de negociación integrado (ODT) reduce la complejidad de la junta

- Incline el entrenamiento para mejorar el tiempo de captura de señal

- Intensidad de la señal de E / S: 1.2V a 1.25V (lógica del transceptor de alta velocidad (HSTL) / lógica terminada (SSTL)), 1.1V a 1.2V (POD2)

- Paquete de 361 pines FCBGA3

- Ancho del bus: x18, x36 bit

Introduccion

El DDRx Wizard es una herramienta fácil de usar en HyperLynx que le permite controlar por lotes las formas de onda temporales y analizar la integridad de la señal de los protocolos DDR JEDEC estándar. El DDRx Wizard se puede iniciar tanto en la etapa de análisis pre-topológico de acuerdo con el escenario "qué pasaría si", como en un tablero completamente trazado. Además, la herramienta le permite importar la mayoría de los formatos de modelos creados por los principales proveedores de chips.

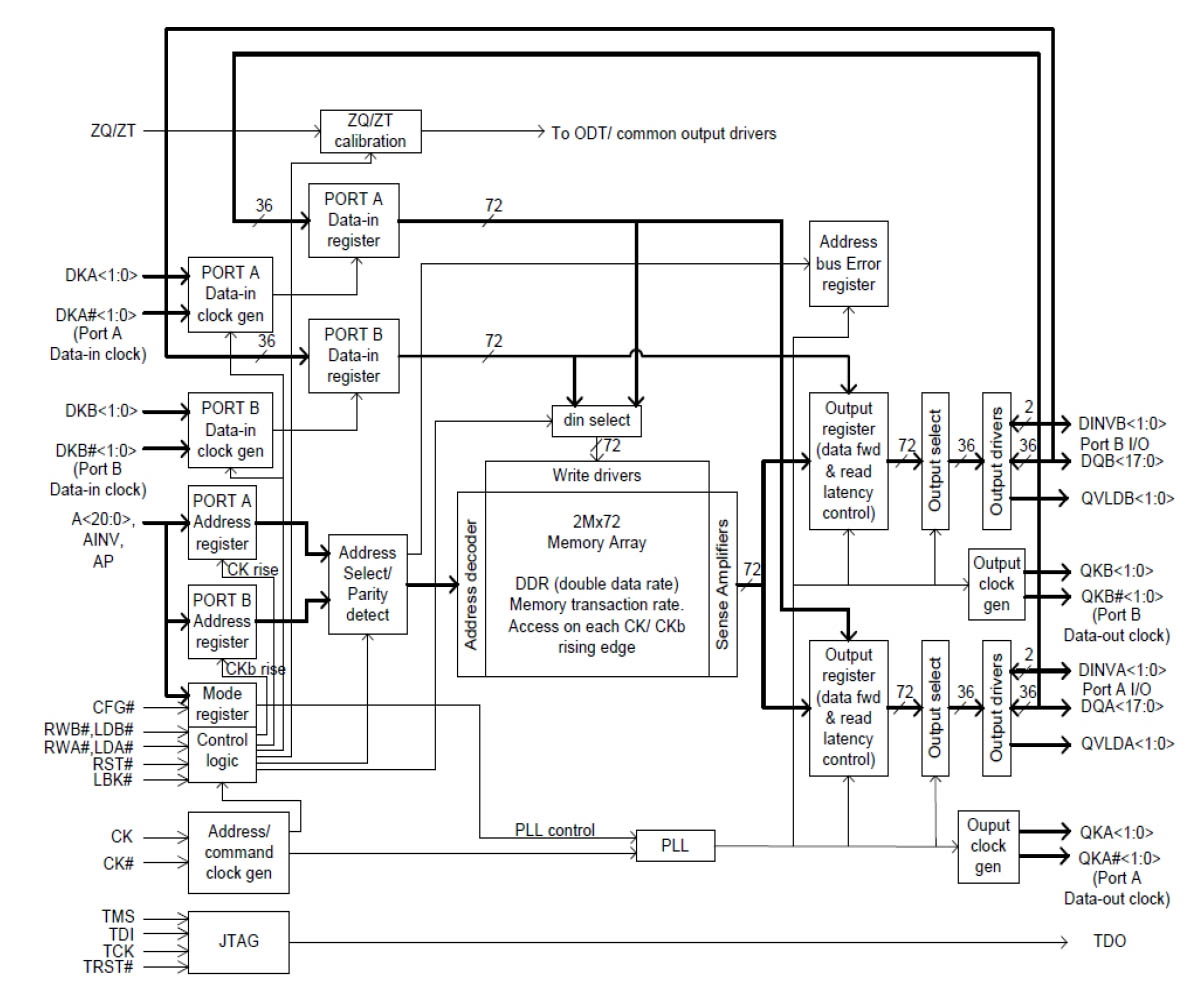

DDRx Wizard le permite verificar todos los bits del bus de memoria para verificar el cumplimiento de la integridad de la señal, así como para cumplir con los requisitos de sincronización entre señales. Este artículo detallará el uso del asistente interactivo para analizar proyectos que implementan el protocolo QDR4 (Fig. 1).

Fig. 1. La arquitectura interna de QDR en el ejemplo del módulo CY7C4142KV13 (se puede hacer clic)

Fig. 1. La arquitectura interna de QDR en el ejemplo del módulo CY7C4142KV13 (se puede hacer clic)Primer vistazo a QDR-IV en HyperLynx DDRx WIZARD

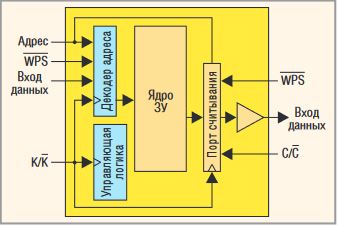

El protocolo QDR-IV define dos pares unidireccionales de una señal estroboscópica de datos: uno para leer datos, el otro para escribir, que admiten operaciones independientes entre sí y operaciones de lectura y escritura simultáneas, y los puertos pueden operar a diferentes frecuencias (Fig.2). Por lo tanto, el riesgo de un mal funcionamiento se elimina por completo.

Fig. 2. Disponibilidad de puertos de lectura y escritura separados en la arquitectura QDR SRAM

Fig. 2. Disponibilidad de puertos de lectura y escritura separados en la arquitectura QDR SRAMPara este protocolo, el DDRx Wizard usará puertas separadas para leer y escribir datos. QDR IV generalmente se implementa usando un bus x36 o x18 bit (ver Fig. 3a y 3b).

El DDRx Wizard habilita la simulación QDR-IV en tres pasos:

- Verificación de lectura de datos

- Comprobación de registro de datos

- Dirección / Control de bus de control

Dado que las comprobaciones del bus de dirección / control pueden realizarse independientemente de las comprobaciones de lectura / escritura de datos, esto puede ahorrarle tiempo al combinar este paso con cualquiera de los pasos de prueba de datos. A continuación se describen los tres escenarios para estas pruebas.

Características tecnológicas

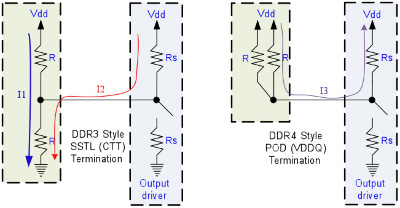

QDR-IV admite la tecnología de drenaje seudo abierto (POD) y la lógica de terminación de lógica terminada de la serie Stub (SSTL) (Figura 4).

Fig. 4. Diferencias entre POD y SSTL

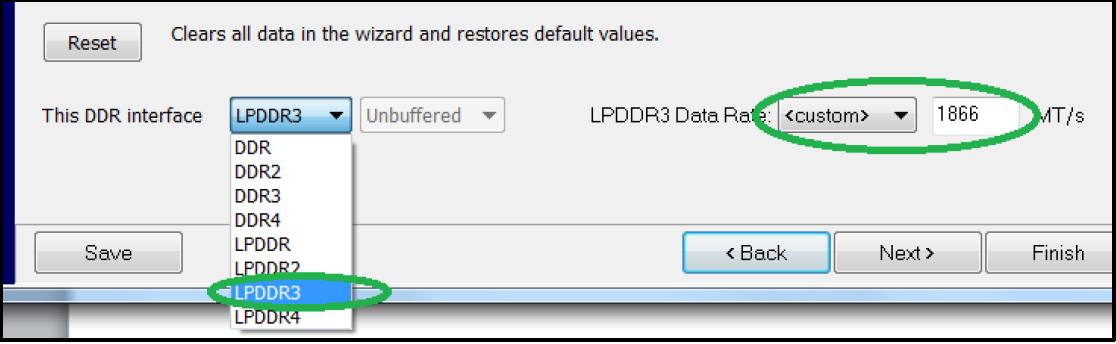

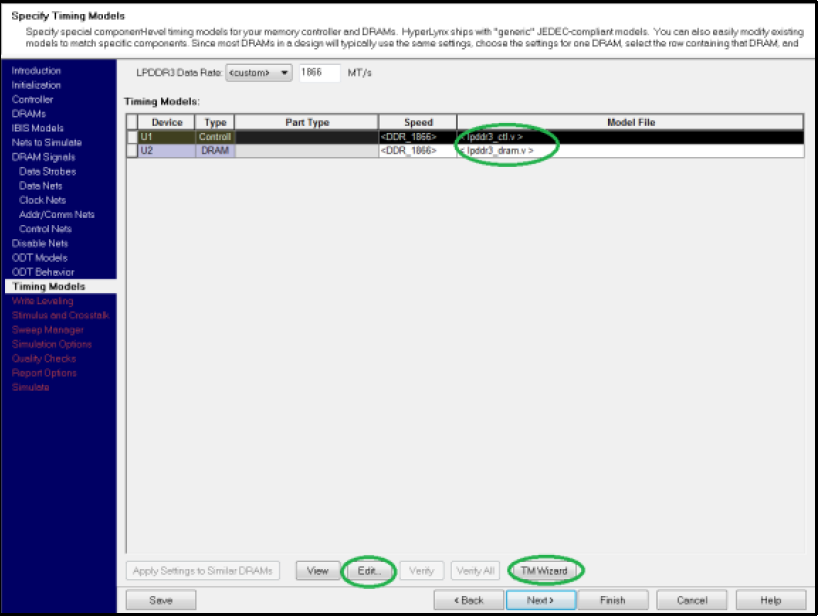

Fig. 4. Diferencias entre POD y SSTLIndependientemente del estándar lógico utilizado, seleccione

LPDDR3 como tecnología (Fig. 5), ya que no hay soporte para el

entrenamiento Vref , como es el caso con el módulo POD del DDR4. En su lugar, se utilizan valores fijos Vref y Vinh / Vinl, similares a DDR3 y LPDDR3. Dado que QDR-IV usa una velocidad de datos dual para señales de dirección como LPDDR3, se recomienda que seleccione esta opción. Luego, ingrese la velocidad de transferencia de datos del usuario, por ejemplo, 1866 MT / so 2133 MT / s, donde MT / s es el número de megatransfers por segundo (megatransfers por segundo).

Fig. 5. La elección de la lógica estándar

Fig. 5. La elección de la lógica estándarSeñal de datos: operación de lectura

Para las operaciones de lectura de señal de datos, DRAM controlará las señales DQ junto con las señales QK estroboscópicas diferenciales. Por lo tanto, la configuración se centra en la operación de lectura de datos y asigna los circuitos (señales) necesarios a la puerta QK correspondiente.

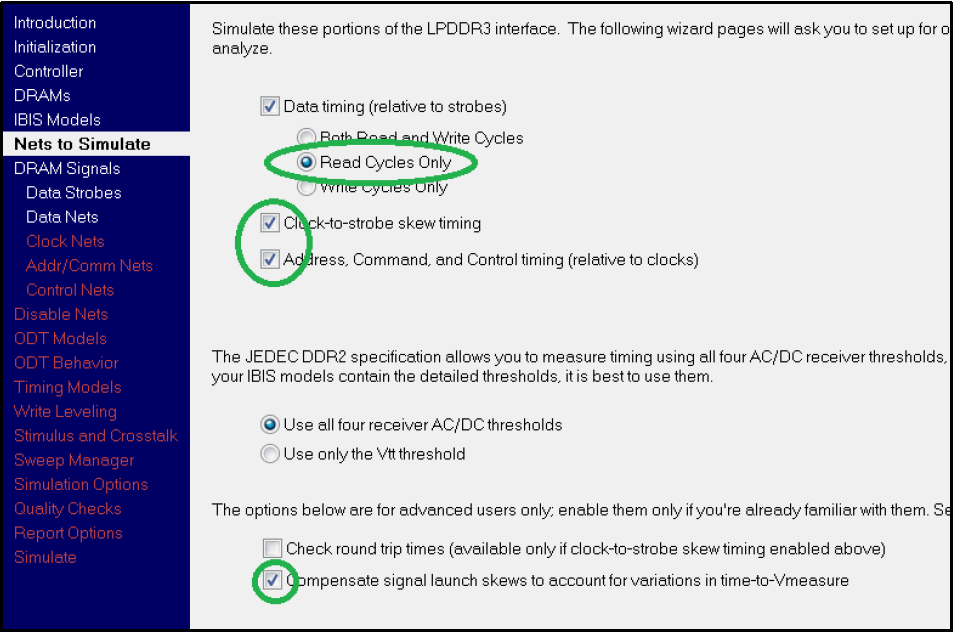

En la sección

Redes para simular (Figura 6), marque la casilla “

Solo ciclos de lectura ”. Las

casillas de verificación Reloj a luz estroboscópica y Dirección son opcionales.

Además, marque la instalación de la

compensación de inicio de señal de compensación para tener en cuenta las variaciones en la casilla de verificación de tiempo de medición .

Fig. 6. Lectura de datos

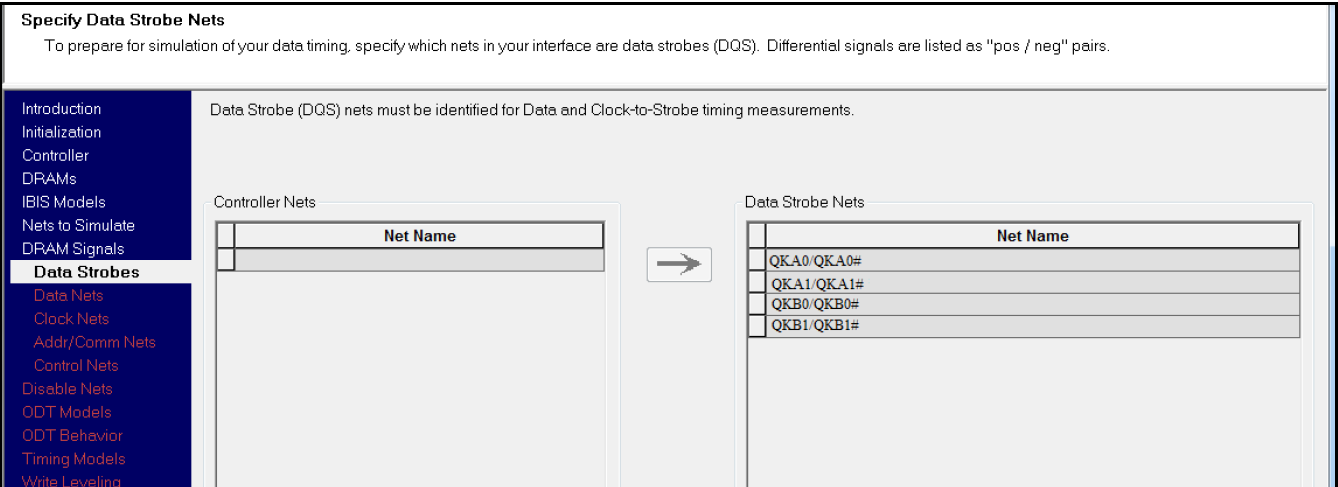

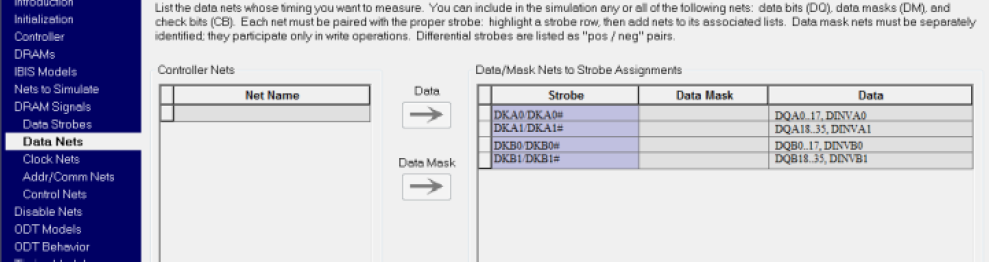

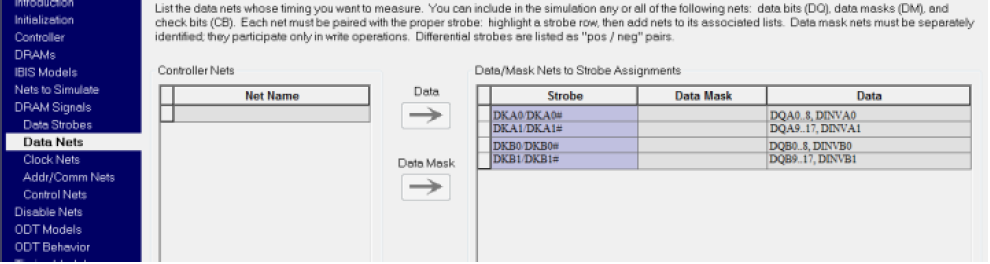

Fig. 6. Lectura de datosAsegúrese de que todas las luces estroboscópicas de datos necesarias estén seleccionadas (Figura 7).

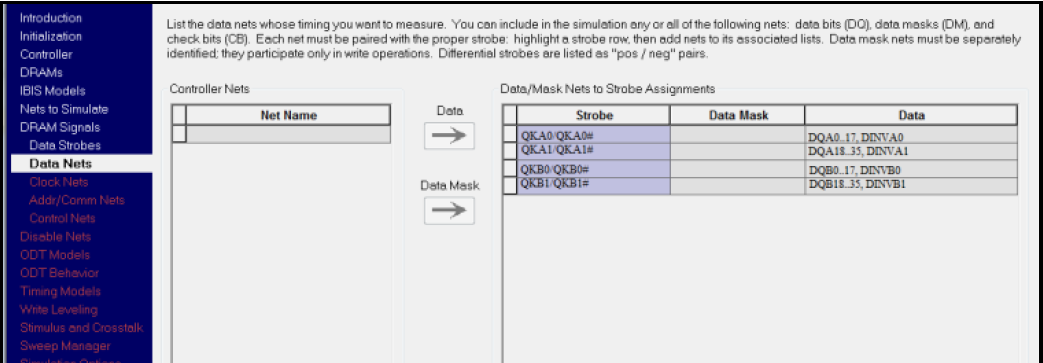

En la sección

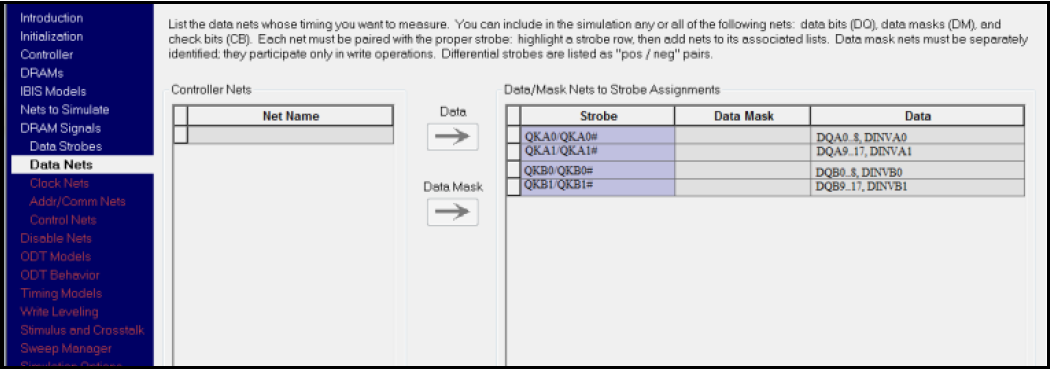

Redes de datos , verifique que cada señal coincida con cada puerta correctamente. Tenga en cuenta que las señales son diferentes para los buses x18 y x36 bit, así que asegúrese de que el pinout sea el adecuado para su caso particular (Fig. 8a y 8b).

Fig. 7. Lectura de datos estroboscópicos

Fig. 7. Lectura de datos estroboscópicos Fig. 8a. Grupo de señal para bus de 36 bits

Fig. 8a. Grupo de señal para bus de 36 bits Fig. 8b. Grupo de señales para el bus de 18 bits.

Fig. 8b. Grupo de señales para el bus de 18 bits.La prueba del bus paralelo generalmente se realiza ajustando / manteniendo el tiempo entre la luz estroboscópica y la señal. Todos estos requisitos, además de otros valores temporales, son requeridos por el Asistente DDRx para verificar los resultados. Estos valores pueden diferir de un microchip a un microchip; por lo tanto, se recomienda ingresar valores que se apliquen a un dispositivo de memoria específico. Además, la información de temporización predeterminada para LPDDR3 no es compatible con QDR-IV. Por lo tanto, toda la información de temporización para QDR-IV debe ingresarse y coincidir con la documentación de su chip.

Esto se puede hacer utilizando el

Asistente de sincronización (Fig. 9), que solicita al usuario que complete varios formularios para la generación posterior de valores temporales, o puede editar los archivos de sincronización .V que corresponden a su controlador y DRAM.

Fig. 9. Establecer valores de tiempoTenga en cuenta que,

Fig. 9. Establecer valores de tiempoTenga en cuenta que, dado que la simulación se realiza en modo

LPDDR3 , los resultados deben interpretarse en consecuencia.

Señal de datos: operación de escritura

La operación de escritura de datos y su análisis es similar al análisis para la operación de lectura descrita anteriormente. Pero hay dos diferencias clave que ahora consideraremos. Con la excepción de estos dos matices, los pasos tomados para la operación de lectura de datos se pueden repetir para simular la escritura de datos.

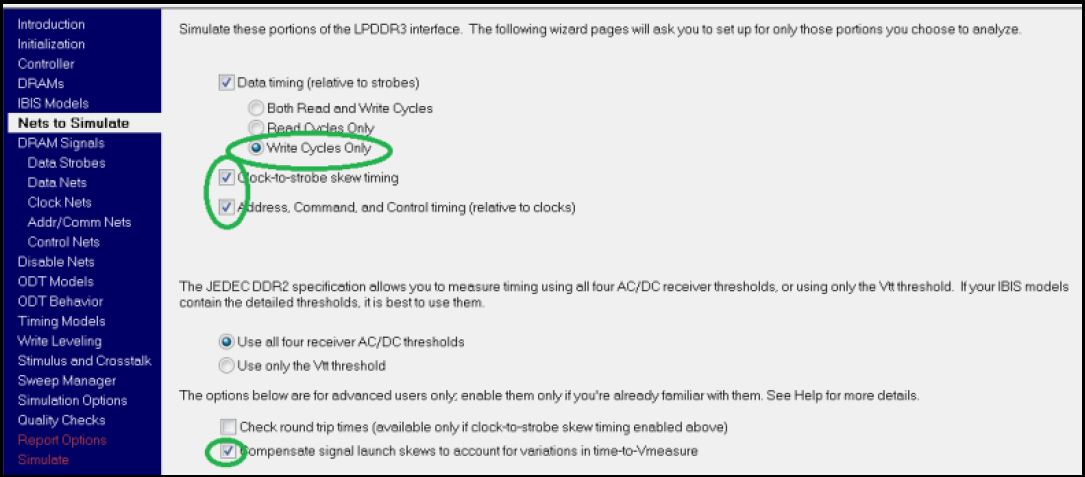

En la sección

Redes para simular (Figura 10), asegúrese de que la

opción Escribir solo ciclos esté seleccionada.

También es posible simular

operaciones de escritura de señal de dirección . Y no olvide asegurarse de que la

casilla de verificación Compensar sesgo para tener en cuenta las variaciones en el tiempo de verificación de la casilla de verificación marcada esté marcada .

Fig. 10. Grabación de datos

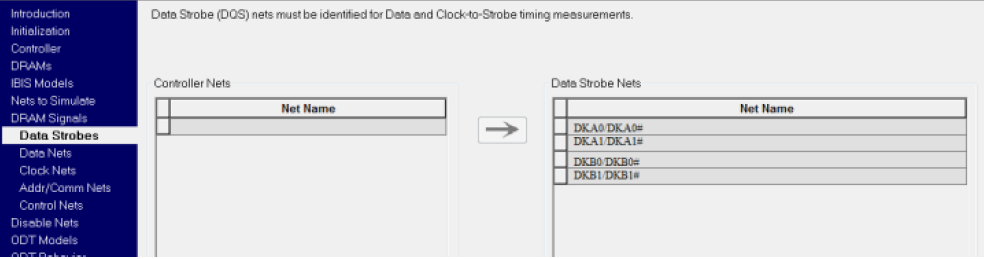

Fig. 10. Grabación de datosAsegúrese de que se seleccionen las puertas correctas en la sección

Strobe de datos (Figura 11). La diferencia clave entre una transacción de lectura y una transacción de escritura es la luz estroboscópica utilizada para sincronizar los datos; esta luz estroboscópica es diferente de la luz estroboscópica utilizada para la operación de lectura de datos (Fig. 12 y 13).

Fig. 11. Puertas de datos de registro

Fig. 11. Puertas de datos de registro Fig. 12. Grupos de señales estroboscópicas de señal (bus de 36 bits)

Fig. 12. Grupos de señales estroboscópicas de señal (bus de 36 bits) Fig. 13. Grupos de señales estroboscópicas de señal (bus de 18 bits)

Fig. 13. Grupos de señales estroboscópicas de señal (bus de 18 bits)Dirección de bus, comando y control

El QDR-IV utiliza bloqueos diferenciales CK / CK # para seleccionar señales de control, dirección y señales de comando. El borde anterior de la señal CK se usa para ingresar información sobre el puerto A, y el borde posterior se usa para seleccionar información sobre el puerto B.

Teniendo en cuenta la integridad de la señal, las formas de onda para las líneas de dirección deben cumplir con los requisitos de instalación y los retrasos de los bordes inicial y final de la señal del reloj. Esto es muy similar al comportamiento de LPDDR3.

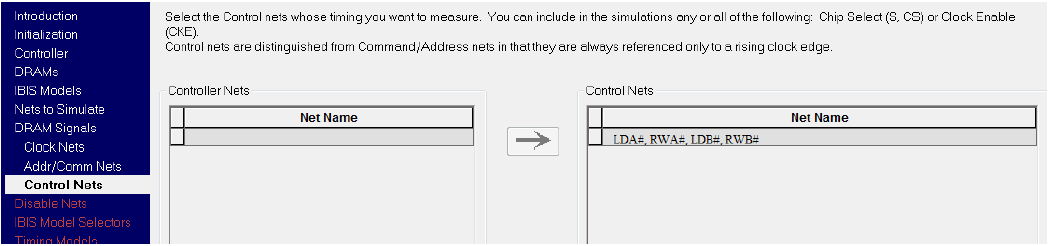

Las señales

LDA #, LDB #, RWA # y RWB # se sincronizan a la misma velocidad de datos (velocidad de datos única). Esto significa que estas señales se sincronizan solo en uno de los dos frentes de los pulsos del reloj. Las señales LDA # y RWA # están sincronizadas en el flanco ascendente del reloj, y las señales LDB # y RWB # están en el flanco descendente.

Los bloques son en gran parte simétricos: el diferencial delantero no es muy diferente del trasero. Esto significa que para garantizar la integridad de la señal, los valores de temporización para

LDB # y RWB # deben ser casi los mismos, si no idénticos, cuando se muestrea en los

bordes ascendente o

descendente del reloj. Las señales de control LPDDR3 también se sincronizan solo en el flanco ascendente.

Los siguientes pasos son específicos para la simulación de bus de dirección, comando y bus de control utilizando QDR-IV.

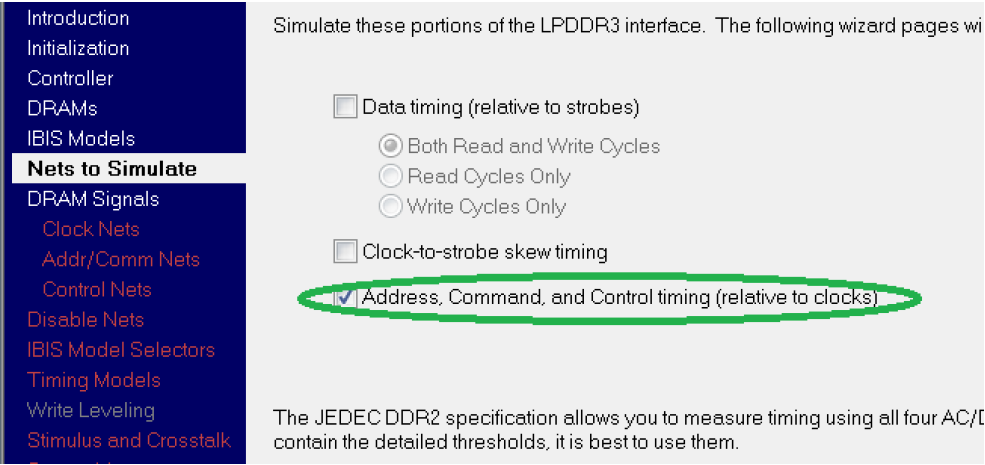

Asegúrese de que en la sección

Redes para simular esté

seleccionada la casilla de verificación

Dirección, Comando y Control de tiempo (en relación con los relojes) (Fig. 14).

Fig. 14. Marque la casilla Dirección, tiempo de comando y control

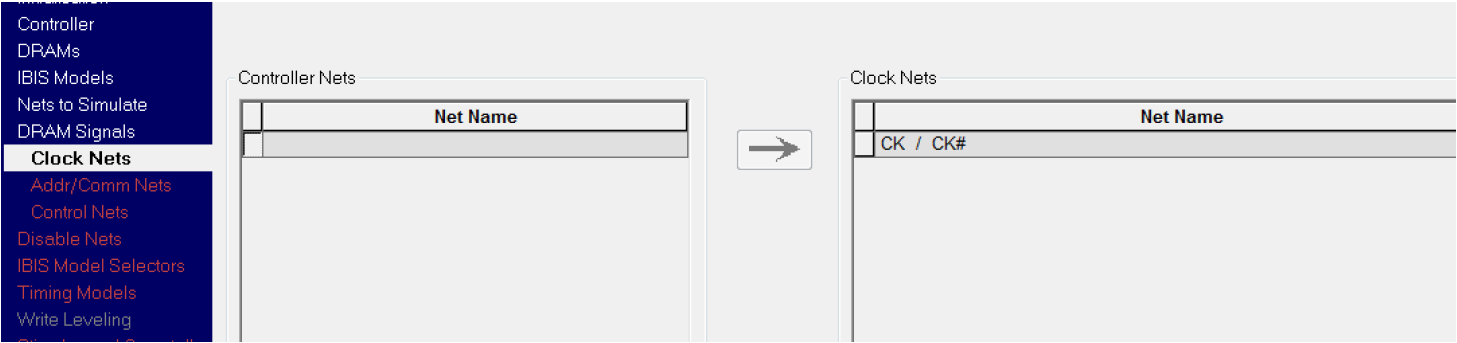

Fig. 14. Marque la casilla Dirección, tiempo de comando y controlEn la sección

Redes de reloj , asegúrese de que esté seleccionado el par diferencial de señales de reloj CK / CK # (Fig. 15).

Fig. 15. La elección del reloj diferencial

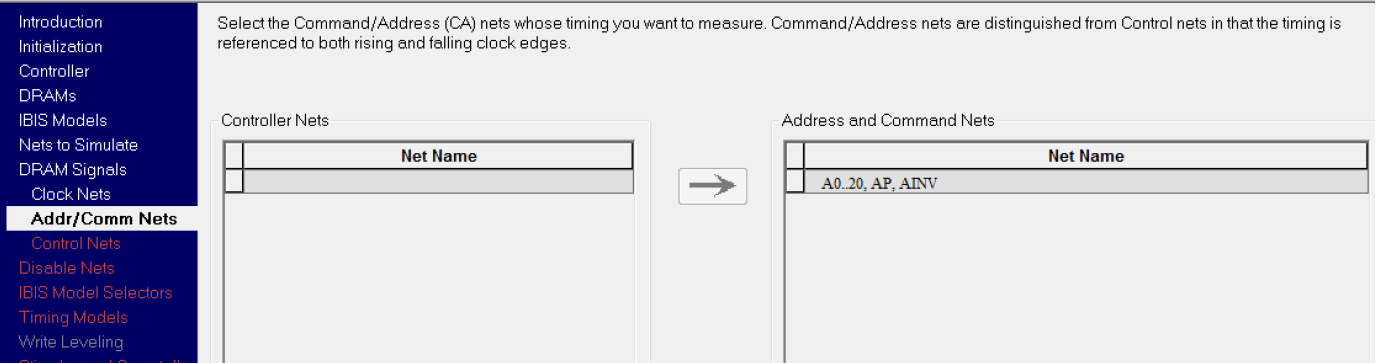

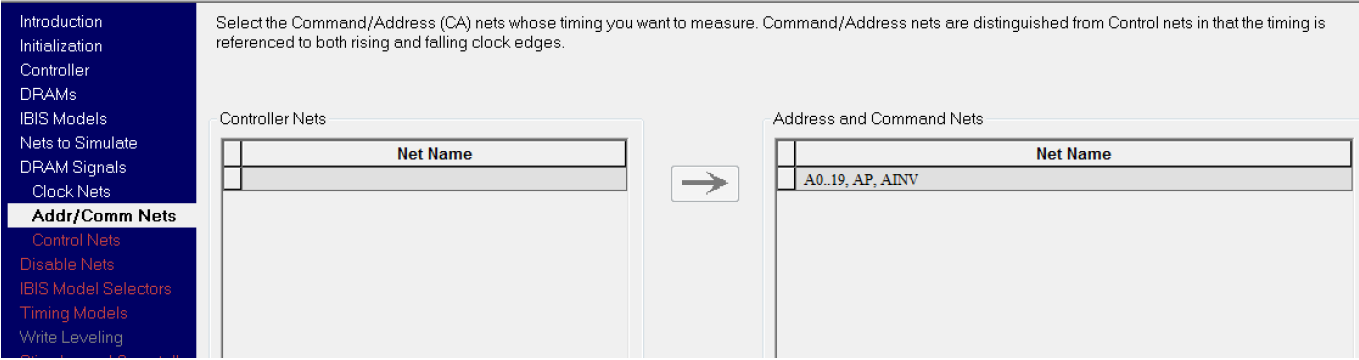

Fig. 15. La elección del reloj diferencialEn la sección

Addr / Comm Nets , asegúrese de que los bits

A [20: 0] estén seleccionados para dispositivos con x36 bits y los bits

A [19: 0] estén seleccionados para dispositivos con x18 bits. Además, configure las

señales AP y AINV (Fig. 16 y 17).

Fig. 16. Configuraciones para buses x36-bit

Fig. 16. Configuraciones para buses x36-bit Fig. 17. Configuraciones para buses x18-bit

Fig. 17. Configuraciones para buses x18-bitEn la sección

Redes de control , seleccione las señales LDA #, LDB #, RWA # y RWB # (Figura 18).

Fig. 18. Señales de control

Fig. 18. Señales de controlAl igual que con el modelado de una señal de datos, asegúrese de estar utilizando los archivos correctos con los parámetros de tiempo. El resto del modelado y evaluación de los resultados es similar a LPDDR3.

"Interpretación de los resultados del informe HyperLynx DDRx"Conclusión

Siguiendo las sencillas instrucciones de este artículo, puede beneficiarse y utilizar el paquete auxiliar DDRx Wizard para simular y probar los buses QDR-IV.

Espero que este manual sea útil para alguien.

Atentamente, Filipov Bogdan (

pbo ).

Aprovechando esta oportunidad, quiero invitar a los desarrolladores de REU a un seminario organizado por Nanosoft y Mentor Graphics:

"Una nueva generación de soluciones de diseño de dispositivos electrónicos de Mentor Graphics"