Saludos, Habr! Mi nombre es Daniil Smirnov, estoy estudiando en la escuela de posgrado de la Universidad ITMO, donde nuestro equipo se dedica a la electrónica programable para proyectos relacionados con sensores de fibra óptica en el laboratorio de programación y modelado. Como base de hardware para sensores, se utilizan FPGA: matriz de puerta programable de campo. Hace un par de años, supimos que los fabricantes de FPGA están llevando a cabo competencias entre los estudiantes de desarrollo. Desde entonces, cada año se forma un equipo de nosotros para participar en este evento, y desde este año resultó ser especial, decidimos compartir cómo era todo desde adentro.

Entrada

Era octubre de 2017, realicé una verificación de rutina semanal: un análisis de las conferencias en curso sobre temas que se están implementando en nuestro departamento. En un momento, recibo un boletín de Terasic: una

nueva competencia está comenzando

en el desarrollo de proyectos utilizando paneles de depuración en el FPGA , ahora en todo el mundo. La experiencia de la misma competencia del año pasado pasa por mi cabeza y recuerda: postergar hasta las últimas dos semanas del mes, depurar y ajustar largos algoritmos y emitir todos los canales al monitor y una promesa de no posponerlo hasta el último día.

Fue una experiencia genial, durante la cual aprendimos mucho sobre una plataforma como SoC FPGA: la interconexión de una gran variedad de elementos lógicos y el procesador Cortex-A9, así como su interacción entre ellos y con los periféricos en la placa de depuración.

Nueva competencia: nuevas reglas, nuevos requisitos, un nuevo nivel. Ahora la competencia se lleva a cabo en varias etapas: primero, las etapas regionales y luego la final en San José; el tablero se envía a todos los participantes del mismo modo,

DE10-Nano , y además ahora puede elegir no solo los tres módulos básicos, sino también una versión grande de los tableros de Analog Devices. Sin embargo, a diferencia de los concursos de años anteriores, esta vez es necesario firmar una garantía del proyecto y, en caso de incumplimiento, los participantes deben devolver las tarifas. Es bastante justo, teniendo en cuenta las estadísticas de los últimos años:

<...> 71 equipos de 20 países europeos registraron el concurso <...> 25 jueces de Industria (ALTERA) y Academia (CNFM) en Francia revisaron los 32 proyectos [1].

El asesor científico, como los estudiantes que querían participar en este trabajo, ya estaba bajo una gran carga en varios proyectos, pero la emoción durante la competencia y la motivación para aprender muchas cosas nuevas se convirtieron en argumentos de peso para participar en la competencia nuevamente. Quedaba por llegar a un proyecto con el que puede aplicar.

Idea para un proyecto

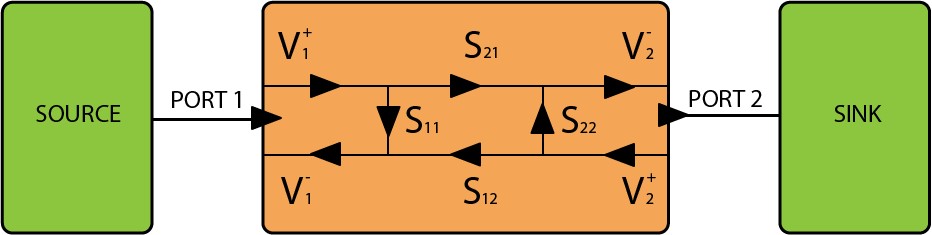

Para que el proyecto no se hiciera a un lado, se decidió implementar un dispositivo útil para el departamento, que luego podría desarrollarse y mejorarse fácilmente. Según las áreas de actividad del departamento, había varias opciones: un reflectómetro óptico, un osciloscopio estroboscópico, etc. Al observar rápidamente las aplicaciones existentes y las placas adicionales disponibles, se reveló que el reflectómetro ya se había anunciado, pero no se podía ensamblar un osciloscopio estroboscópico en dichos elementos. La única idea que permanece viva es el analizador de red vectorial. El otro día se trajeron un par de bobinas al laboratorio, para el cual no había documentación. La tarea consistía en determinar al menos las características aproximadas de estas bobinas. Se sabía que el circuito oscilatorio estaba montado en ellos, por lo que la tarea principal era encontrar la frecuencia de resonancia. En tales tareas, un analizador de red vectorial (VAC o VNA - Vector Network Analyzer) puede encontrar la aplicación. VNA le permite definir una matriz de dispersión, también conocida como matriz de parámetros S. En este método, el elemento en estudio se considera una caja negra, en la que se analizan las señales incidentes y reflejadas de los puertos de este dispositivo. Entonces, para un sistema de dos puertos, la matriz es la siguiente:

Donde V1 + V2 + son ondas electromagnéticas que llegan a los puertos;

V1- V2- - ondas electromagnéticas que salen de los puertos;

Sij son elementos de la matriz de dispersión multitrayecto. [2]

Esquema de medición de parámetros S de un multipolar

Esquema de medición de parámetros S de un multipolarNo pudimos examinar los componentes y el circuito usando una radiografía (al menos por la radiografía del metro), por lo que el siguiente circuito se ensambló en las rodillas: las frecuencias se configuraron alternativamente con un paso a través del circulador a la entrada de la bobina usando un generador, el segundo puerto del circulador se conectó a la entrada de la bobina, y la tercera entrada a un osciloscopio que tiene en su software el modo de análisis de amplitud-frecuencia. Tal circuito hace posible medir el parámetro S11, es decir reflejo Al final, después de mucha angustia y calibración, logré eliminar esta característica, pero ¿a qué costo? El departamento había esperado durante mucho tiempo la adquisición de un analizador de red vectorial para tales tareas (medir el AFC de los dispositivos electrónicos), pero esta compra siempre se retrasó de alguna manera.

Después del alboroto con las bobinas, se decidió ensamblar su propio analizador de circuitos con visualización y ajuste cómodo. No es difícil encontrar emoción y un deseo de aprender algo nuevo para usted de los estudiantes y estudiantes graduados que trabajan en el departamento, por lo que el equipo se formó rápidamente de un ingeniero electrónico, un programador-desarrollador de sistemas en un chip, yo y dos mentores.

Apenas dicho que hecho! Después de numerosas discusiones sobre la banda de frecuencia, los algoritmos de procesamiento y otros parámetros del proyecto, la aplicación contenía lo siguiente:

- El proyecto reclamado es un analizador de circuito vectorial basado en SoC FPGA en una placa DE10-Nano;

- Tarjetas adicionales solicitadas: una tarjeta con un generador de frecuencia programable, un mezclador de alta frecuencia y una tarjeta con un ADC;

- Rango de frecuencia de funcionamiento: de acuerdo con los parámetros presentados de placas adicionales;

- Posibilidades de expansión rápida del número de puertos conectados;

- La salida del componente de amplitud y fase a la pantalla;

- Otras funciones básicas de entrada / salida para el analizador de red vectorial.

Para pasar a la siguiente etapa, era necesario que la página del proyecto obtuviera un número suficiente de "me gusta" de los usuarios que se registraron en el sitio. Al principio, todo salió bien, pero luego algunos proyectos dudosos comenzaron a ganar valores poco realistas y contrastantes de me gusta y puntos de vista en comparación con otros proyectos. Resultó que el sitio del concurso era demasiado vulnerable a las trampas.

Después de un tiempo, los organizadores informaron que el panel de jueces aún elegiría a los finalistas, por lo que los gustos de los usuarios, de hecho, perdieron peso. El 31 de enero, nuestro equipo apareció en las listas de los que pasaron a la siguiente etapa y comenzamos a pensar en nuestro proyecto con más detalle antes de la depuración.

Dura realidad

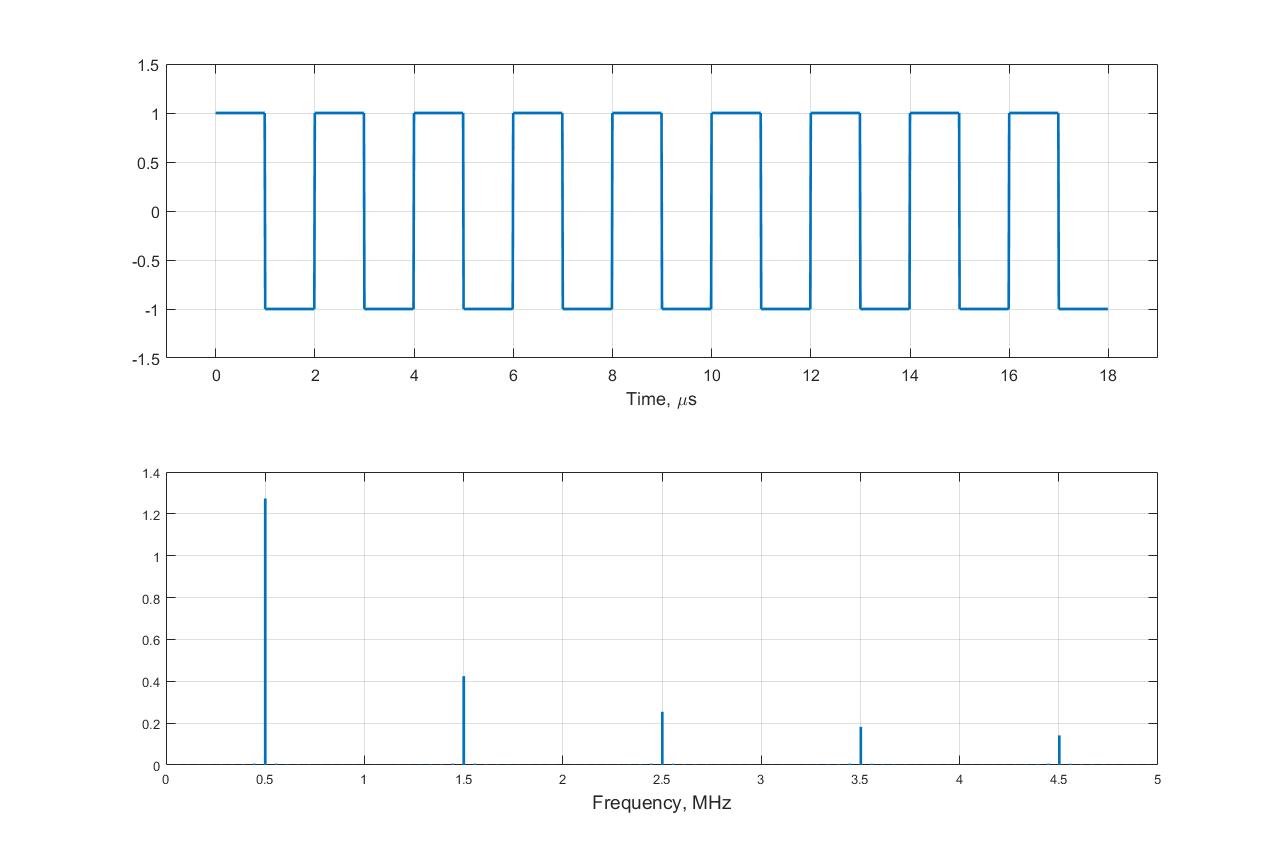

El primero fue el tablero DE10-Nano. Agradable, pero un poco extraño: esperaban que las tablas se unieran. Unos días más tarde, se recibe una llamada de la aduana: las tarifas llegaron, todas juntas superaron el umbral de precio, por lo que debe pagar el despacho de aduanas una cantidad aproximadamente igual al costo de estas tarifas. Tal situación nos molestó, pero no nos convenía: rechazamos los consejos. En presencia de mezcladores y generadores que no teníamos, es necesario encontrar nuevas soluciones. Que hacer Lo primero que se me ocurrió no fue la solución más precisa, sino más bien inusual: use la pata GPIO habitual y genere un meandro a partir de ella. Se instala un filtro analógico de paso bajo en la salida de este pie con una banda de corte ligeramente más grande que la frecuencia máxima de meandro. Para empezar, se propuso incluir un análisis de 1 MHz (por ejemplo): luego, después del filtro, obtendríamos un seno más o menos puro (el filtro cortaría los armónicos más altos), y así sucesivamente hasta que la frecuencia caiga a aquella en la que la señal después del filtro Habrá dos armónicos. El meandro es la suma de los armónicos impares, y la contribución proporcional de cada armónico se conoce de antemano [3].

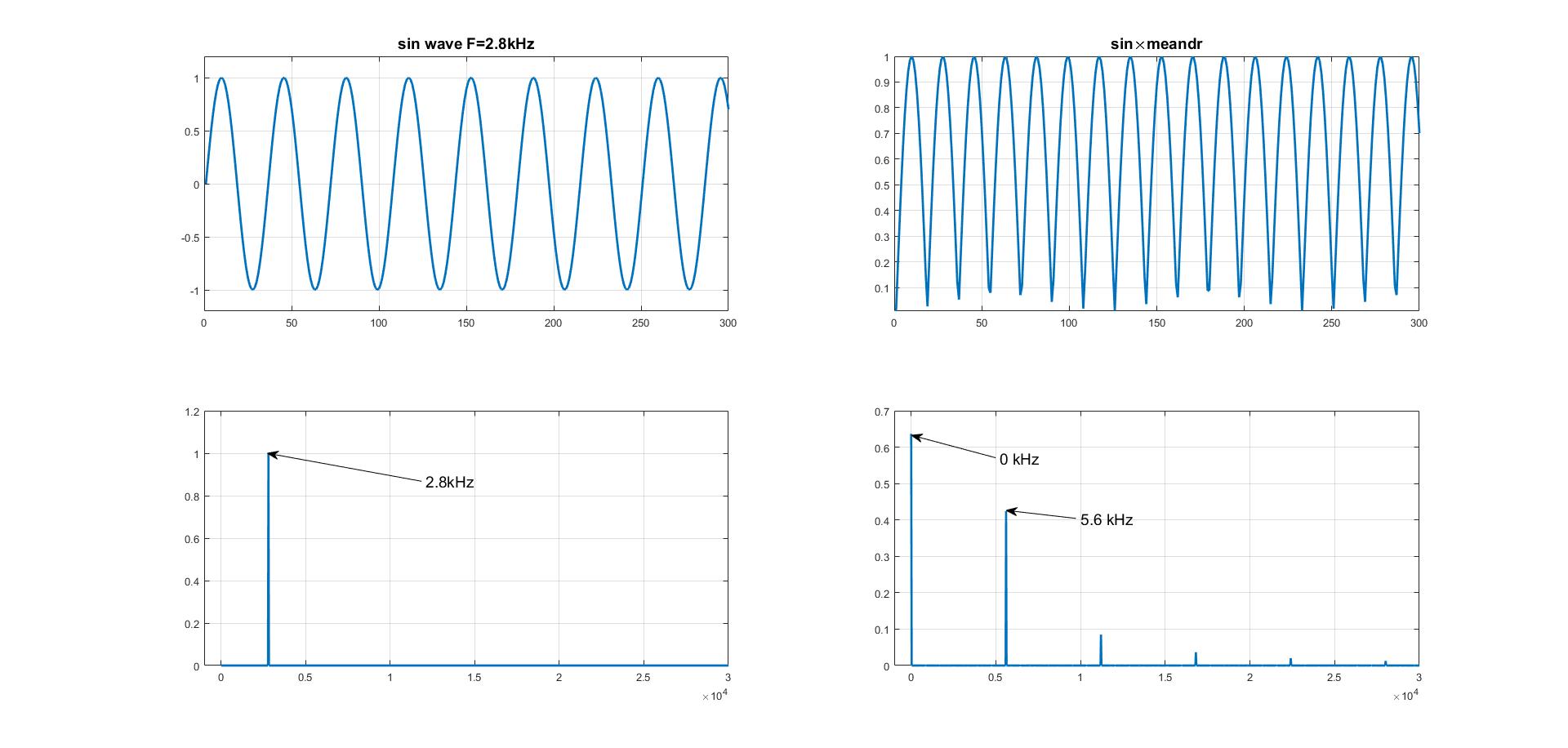

Un ejemplo de un meandro en los dominios de tiempo y frecuencia: los componentes de la señal armónica a 500 kHz, 1,5 MHz, etc. son visibles en el espectro.

Un ejemplo de un meandro en los dominios de tiempo y frecuencia: los componentes de la señal armónica a 500 kHz, 1,5 MHz, etc. son visibles en el espectro.Con un filtro con una frecuencia de corte de 1 MHz, puede bajar a 33. (3) kHz. Después de esta frecuencia, deberíamos obtener la suma de dos senos detrás del filtro. Se conoce la relación proporcional de sus amplitudes (función sinc), la respuesta del dispositivo medido a una frecuencia de 1 MHz (primer armónico impar), por lo que debemos componer una ecuación con una desconocida y calcular la característica de respuesta a una frecuencia de 33, (3) kHz. Al principio, esta solución parecía demasiado simple, por lo que para empezar se le dijo a todos con la esperanza de que alguien encontrara un error. No se encontraron errores, pero se descubrieron varias limitaciones a medida que avanzaba la discusión:

- El pie GPIO no es la mejor fuente de meandro, especialmente con frecuencia creciente;

- Soldar un filtro compacto en los componentes disponibles será una tarea no trivial;

- Incluso si se pueden eludir estas limitaciones, surge un problema de sincronización para la detección de fase.

Supongamos que hemos resuelto todos los problemas en el lado analógico; programáticamente, surgen otros dos:

- Con una frecuencia decreciente, el error de cada detección y cálculo previo contribuirá a la medición posterior;

- Con una frecuencia decreciente, el tiempo para calcular las características aumentará significativamente.

Y finalmente, por último pero no menos importante. El circuito descrito se puede usar si el elemento medido se puede describir mediante una función de transferencia lineal. Sin embargo, si medimos un cuadro negro con características no lineales, la idea tiene más problemas que buenos. No quedaba mucho tiempo (el primer resultado debería mostrarse dos meses después de que llegara el tablero), por lo tanto, después de algunas deliberaciones, decidimos verificar nuestros suministros contra los tableros de depuración existentes, ¡y encontramos un

DAC de 14 bits a 125 Msps ! No es la solución más elegante, pero no hay otra opción, la usamos como generador de señal de salida.

Primer concepto

El DAC seleccionado como generador recibe datos en la entrada del bus paralelo y lo enclava con una señal de reloj proveniente del FPGA. Tal circuito es ideal para la sincronización en nuestro circuito. Sin embargo, quedaban preguntas con la detección.

Sí, en la misma placa hay un ADC de 14 bits a 65 Msps. Pero solo las capacidades del generador son potencialmente más altas, y de acuerdo con el teorema de Kotelnikov, este ADC ya no funcionará a frecuencias máximas.

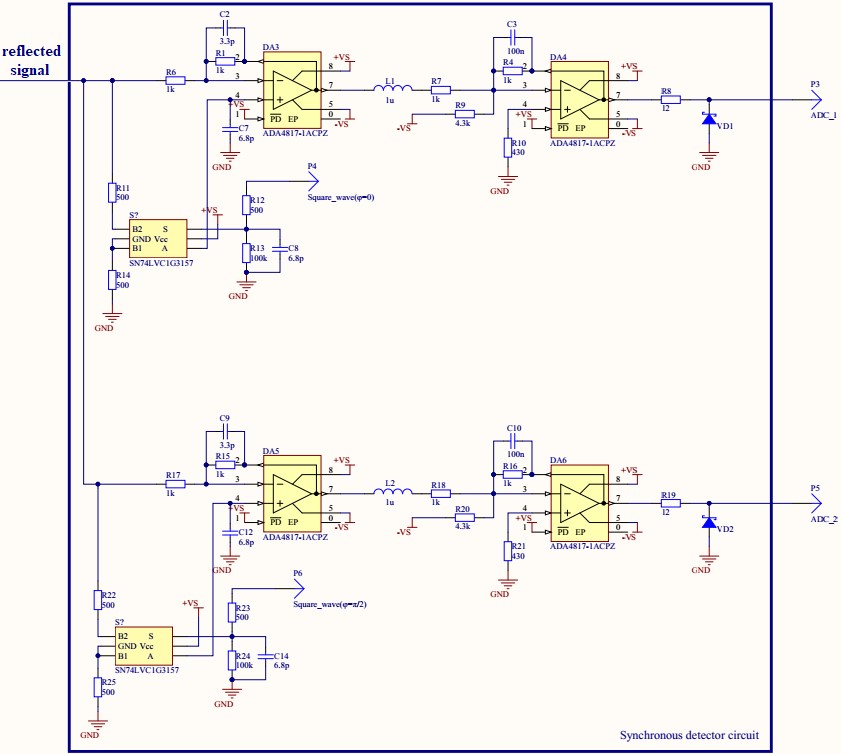

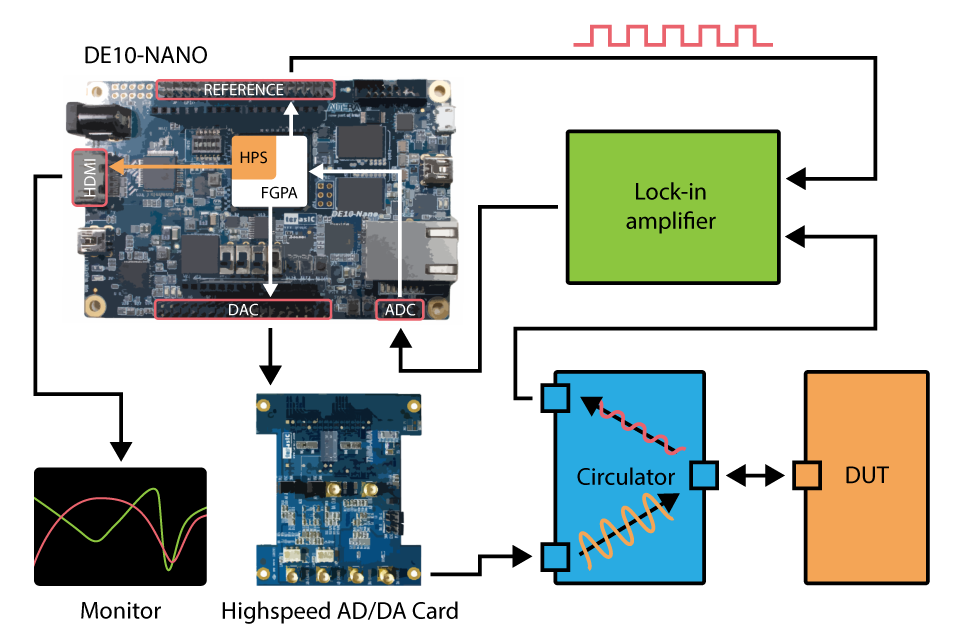

La solución se encontró durante una discusión de este problema con ingenieros electrónicos experimentados. Resultó que para nuestra tarea podemos usar un circuito amplificador de bloqueo: la salida de dicho detector es de dos valores constantes, componentes de fase y cuadratura, de los cuales puede obtener la amplitud y fase de la señal, y dado que son constantes, pueden detectarse incluso con el ADC lento instalado en el DE10-Nano! Se decidió modelar primero el circuito en LTSpice, y solo luego seleccionar los componentes y ensamblar el circuito, teniendo en cuenta que la entrada del detector es una señal del circulador, y las salidas están conectadas al ADC en la placa DE10-Nano.

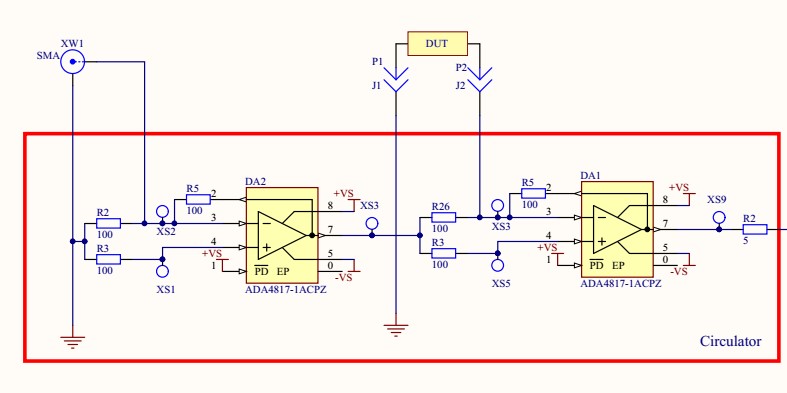

Sobre detector sincrónico y circuladorUn detector sincrónico también se utiliza en el procesamiento de señales digitales para detectar varias señales en un contexto de ruido. Zurich Instruments tiene una buena descripción [4], en nuestro caso la detección es la siguiente: la señal reflejada de frecuencia conocida se multiplica por el meandro utilizando un interruptor de alta frecuencia y un amplificador operacional:

El circuito de detección de reflexión

El circuito de detección de reflexiónDe hecho, la multiplicación se implementa al cambiar el modo de funcionamiento del amplificador operacional, y el cambio se controla mediante dos meandros provenientes de la placa DE10-Nano: uno de ellos está en fase con la señal original (recibida en la entrada del dispositivo) y el otro con un retraso de fase de 90 grados.

El resultado de la multiplicación es la transferencia de la señal útil al componente DC, y todas las frecuencias anteriores ya no son interesantes y, por lo tanto, se pueden filtrar:

Espectro de señal antes y después de la multiplicación: en la salida del amplificador operacional, puede ensamblar un filtro de paso bajo simple para aislar solo el componente de CC

Espectro de señal antes y después de la multiplicación: en la salida del amplificador operacional, puede ensamblar un filtro de paso bajo simple para aislar solo el componente de CCUn circulador en amplificadores operacionales (amplificadores operacionales) es un circuito de conexión en serie de amplificadores operacionales cerrados en un anillo. Los circuladores OA se utilizan para muchos fines, en particular, para sintonizar antenas, amplificadores, generadores, Gigabit Ethernet, etc. en el rango de frecuencia de hasta cientos de megahercios. Al crear el VAC, se utilizó un circuito circulador creado en base a dos amplificadores operacionales [5].

Diagrama de circuito para conectar el dispositivo medido

Diagrama de circuito para conectar el dispositivo medido  Concepto de proyecto actualizado

Concepto de proyecto actualizadoLas señales sinusoidales con una frecuencia de 1 Hz a 1 MHz con pasos establecidos a unos pocos Hz se enviaron al primer puerto del circulador. El dispositivo estudiado se conectó al segundo puerto, dependiendo de la respuesta de frecuencia de la cual cambió el coeficiente de reflexión de la señal. La señal reflejada se alimentó al puerto 3, donde se ensambló un circuito detector sincrónico para determinar las características de frecuencia y fase. Para un funcionamiento correcto, los puertos del circulador se combinaron con una impedancia de 100 ohmios, lo que se asoció con la resistencia de salida del DAC y la elección de los dispositivos en estudio.

Quedaba menos de un mes antes de que se completara el proyecto, y al final de la fecha límite era necesario preparar materiales de informe: una descripción detallada del proyecto en la página de la competencia, un proyecto publicado en GitHub en el dominio público y un video informe sobre el trabajo realizado.

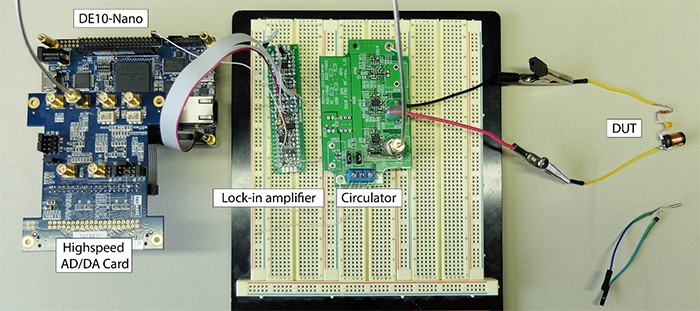

Como ahora entendíamos qué datos irían a las entradas y salidas, comenzamos a trabajar en un proyecto para el SoC FPGA. Vimos que el proyecto se implementaba de la siguiente manera: el usuario establece el rango de frecuencia en el que se planifica la medición, el FPGA comienza a generar armónicos en un intervalo específico a su vez utilizando el DAC, el ADC recibe los componentes de cuadratura y fase en la entrada, convirtiéndolos a los valores de amplitud y fase en la frecuencia actual , los valores obtenidos se muestran en tiempo real en el monitor conectado a la placa de depuración. Ya hubo logros en la visualización de información en el monitor, por lo que la parte principal fue la representación correcta de los datos en tiempo real y la salida de la imagen a HDMI. Estamos desagrupados. El primer grupo asumió tareas en el programa para el procesador, para comprender con más detalle las inicializaciones necesarias, preguntas sobre la visualización de datos. También les pedimos que aumentaran la resolución de la pantalla a 1024x768 [6]. El segundo grupo dejó detalles sobre la implementación de la parte en el FPGA, que luego se debe suministrar al procesador a través del bus de interfaz ligero_h2f, así como una prueba de la operabilidad del primer prototipo de detector síncrono. Después de eliminar las deficiencias y medir con éxito las características de varios elementos, no quedaba mucho tiempo, por lo que los siguientes dos días se dedicaron a conectar los sistemas, agregar informes y editar el video.

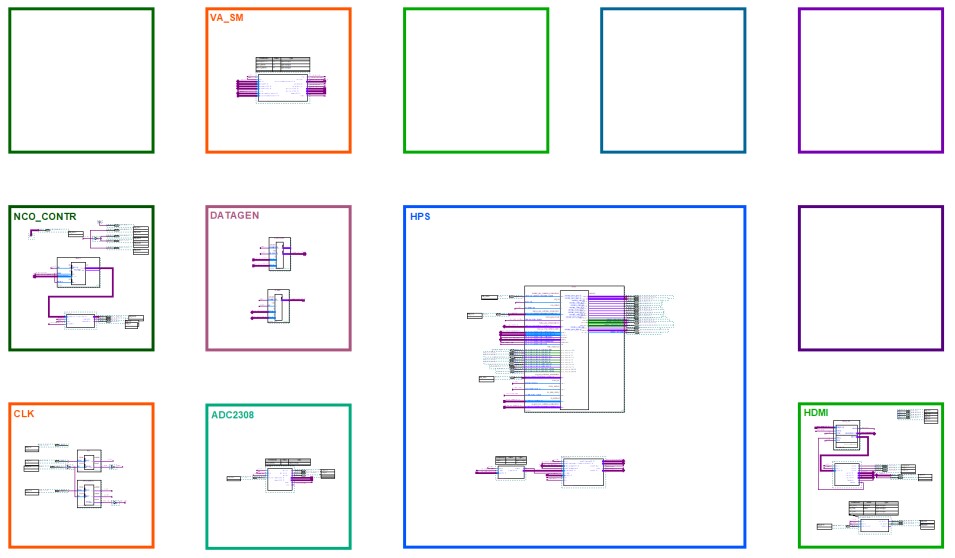

Apariencia del archivo de nivel superior en Quartus II

Apariencia del archivo de nivel superior en Quartus IIUltimos minutos

Después de pasar más de un par de días libres en el laboratorio, armamos todo el sistema. No funcionó para todo el rango de frecuencia potencial, midió solo el parámetro S11 y reflejó las características medidas de fase y amplitud del dispositivo conectado en el monitor. El dispositivo ensamblado externamente todavía no se veía muy atractivo: tres placas separadas conectadas por cables de un solo núcleo, pero este es un prototipo que

funciona y puede ponerse un marafet en la siguiente etapa. Escribimos el texto, ilustramos las etapas de implementación, filmamos un video, subimos todo al sitio y comenzamos a esperar.

Por supuesto, enviamos algunos enlaces de amigos a estos materiales para agregar vistas ligeramente. Sin embargo, en un día, las opiniones comenzaron a crecer, como si alguien hubiera fusionado esto en una promoción. Después de un pequeño análisis resultó: nuestro proyecto se notó en hackaday.io [7] y la gran mayoría de las vistas eran de allí. Fue interesante ver las primeras respuestas a nuestro proyecto. Inspirados, comenzamos a esperar los resultados.

Sin embargo

Este no es el primer año de nuestra participación en la competencia. Este proyecto fue para nosotros el más reflexivo entre el trabajo estudiantil implementado previamente. Pero no creció juntos: no pasamos a la siguiente etapa. Quizás esto se deba a un malentendido entre nosotros y los jueces. Quizás el proyecto simplemente no entra completamente en el área de las tendencias actuales para FPGA (criptografía, computación paralela, redes neuronales, etc.). Pero para nosotros, este es un gran paso en el desarrollo de SoC FPGA, una nueva rama de desarrollo y, lo más importante, experiencia.

Ps

¡Felicitaciones a los representantes rusos que obtuvieron el segundo lugar en la final del concurso!

Agradezco a mis colegas del proyecto Danila Nikiforovsky y

Yevgeny Vostrikov y a los líderes

Ivan Deineku ,

Philipp Shuklin y Artem Aleinik por su activa participación y apoyo.

Referencias

[1] Concurso Innovate Europe 2015

www.innovateeurope.org/eu/2015winner.html[2] Guía del ingeniero para pruebas automatizadas de interfaz de alta velocidad, Jose Moreira, Hubert Wekmann, 2010, Apéndice F, página 503

[3] El espectro de la secuencia periódica de pulsos rectangulares,

en.dsplib.org/content/fourier_series_pimp/fourier_series_pimp.html[4] Principios de detección de bloqueo y el estado del arte, Zurich Instruments

www.zhinst.com/applications/principles-of-lock-in-detection[5]

Circulador / aislador de baja frecuencia sin ferrita e imán

www.cqham.ru/oth9.htm[6] Proyecto VAC para la placa DE10-Nano

github.com/tvShushtov/em078_vector_analyzer[7] Artículo sobre el VAC en Hackaday

hackaday.com/2018/05/09/vector-network-analyzer-uses-soc-fpga