Intel desarrolló el chip 8087 en 1980 para mejorar el rendimiento de las PC con procesadores de línea 8086/8088 (como la PC de IBM) al realizar operaciones de punto flotante. Dado que los primeros microprocesadores fueron diseñados para realizar operaciones con números enteros, la ejecución de operaciones con números de coma flotante fue lenta, es decir, sobre el desempeño de operaciones trascendentales, como funciones trigonométricas o logaritmos. El coprocesador 8087 aumentó significativamente la velocidad de ejecución de tareas de punto flotante; todo se hizo casi 100 veces más rápido. La arquitectura 8087 también se implementó en procesadores Intel posteriores, y las instrucciones 8087 todavía se usan en las PC modernas x86. Intel introdujo el chip 8087 en 1980, diseñado para mejorar el rendimiento de la computación de punto flotante en los procesadores 8086 y 8088.

Debido a que los primeros microprocesadores solo funcionaban con números enteros, la aritmética de punto flotante era lenta, y las operaciones trascendentales como disparadores o logaritmos parecían aún peores. Agregar el coprocesador matemático 8087 al sistema nos permitió acelerar las operaciones de punto flotante 100 veces. La arquitectura 8087 se convirtió en parte de los procesadores Intel posteriores, y las instrucciones 8087 (aunque desactualizadas) siguen siendo parte de los modernos escritorios x86.

El chip 8087 proporcionó una aritmética de coma flotante rápida para la PC original de IBM y se convirtió en parte de la arquitectura x86 utilizada hoy en día. Una de las características inusuales del 8087 es una ROM de varios niveles (memoria de solo lectura), capaz de almacenar dos bits por transistor, que es el doble de la densidad de una ROM convencional. En lugar de almacenar datos binarios, cada celda en la ROM 8087 guardó uno de cuatro valores diferentes, que luego fueron decodificados en dos bits. Como el 8087 necesitaba una gran cantidad de ROM para el microcódigo (1) y la cantidad de transistores en el chip era muy limitada, Intel utilizó una tecnología inusual para resolver el problema. En este artículo, explicaré cómo Intel implementó esta ROM en capas.

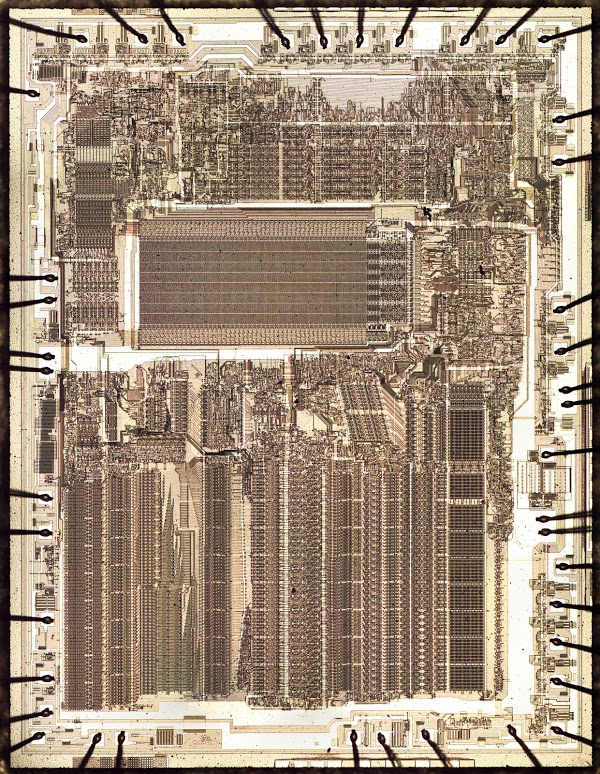

Abrí el chip 8087 y lo fotografié con un microscopio, obteniendo la foto de abajo. En la foto, indiqué los principales bloques funcionales basados en mi propia ingeniería inversa (haga clic para ampliar la imagen). La matriz del procesador 8087 es bastante compleja, con 40,000 transistores (2). El 8087 utiliza números de coma flotante de 80 bits: 64 bits están reservados para la mantisa, 15 bits para el exponente y otro bit con signo. (Ejemplo de un número con una base de 10: entre 6.02 × 1023, 6.02 es la mantisa y 23 es el exponente). En la parte inferior de la fotografía, la palabra "procesamiento de fracciones" marca parte del esquema para la mantisa. De izquierda a derecha, esto incluye: almacenamiento constante, desplazamiento de 64 bits, sumador / sustractor de 64 bits y pila de registros. Un poco más alto es el esquema para procesar el exponente.

La ejecución de la instrucción en 8087 requirió varios pasos, y en algunos casos más de 1000. El firmware 8087 usó un microcódigo para determinar operaciones de bajo nivel en cada paso: cambios, incrementos, muestras de memoria, constantes de lectura, etc. Puede percibir el microcódigo como un programa simple, escrito en forma de microcomandos, en el que cada microcomando genera señales de control para varios componentes del chip. La foto de arriba muestra una ROM con el programa de microcódigo 8087. La ROM ocupa una gran parte del chip, mostrando claramente por qué era necesaria una ROM compacta de varios niveles. A la izquierda de la ROM está el "motor" en el que se lanzó el programa de microcódigo, de hecho, un procesador simple.

El 8087 funcionó como coprocesador con el procesador 8086. Cuando el 8086 detectó una instrucción especial de coma flotante, el procesador la ignoró y permitió que el 8087 ejecutara la instrucción en paralelo. No explicaré en detalle el funcionamiento interno de 8087, pero, en resumen, las operaciones de coma flotante se implementaron utilizando operaciones de suma / resta y desplazamiento de enteros. Para sumar o restar dos números de coma flotante, 8087 realizó un desplazamiento en bits del número hasta que los delimitadores binarios (es decir, el separador decimal es una coma, pero en el sistema binario) son iguales, y luego sumaron o restaron la mantisa. La multiplicación, división y raíz cuadrada se realizaron mediante cambios repetidos, sumas o restas. Las operaciones trascendentales (bronceado, arctan, registro, potencia) utilizaron algoritmos CORDIC, que utilizan cambios y la adición de constantes especiales, procesando un bit a la vez. 8087 también encontró muchos casos especiales: infinito, desbordamiento, NaN (no un número), números desnormalizados y varios modos de redondeo. El microcódigo almacenado en la ROM controlaba todas estas operaciones.

Implementación de ROM

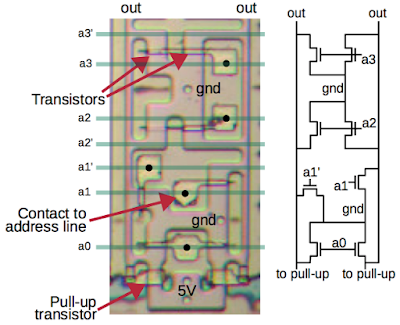

El chip 8087 consiste en una pequeña matriz de silicio en la que el silicio se impregna de impurezas en algunos lugares para obtener las propiedades deseadas de los semiconductores. El polisilicio (un tipo especial de silicio) se aplica a la superficie del silicio, que forma cables y transistores. Y finalmente, una capa de metal sobre silicona completa el circuito eléctrico de trabajo. En la foto a continuación, en el lado izquierdo, se muestra una pequeña parte del chip, ya que es visible bajo el microscopio, mostrando un cableado de metal amarillento. En el lado derecho de la foto, el metal se eliminó con ácido, exponiendo polisilicio y silicio. Cuando el polisilicio cruza el silicio, se forma un transistor. Las áreas rosadas son de silicio dopado, y las delgadas líneas verticales son de polisilicio. Los círculos pequeños son los contactos entre las capas de silicio y metal, que los conectan entre sí.

Estructura ROM en Intel 8087 FPU. La capa de metal se muestra a la izquierda y el polisilicio y el silicio a la derecha.Aunque hay muchas formas de construir ROM, la forma estándar es crear una cuadrícula de "celdas" donde cada celda almacena un bit. Cada celda puede tener un transistor (que significa 0 bits) o no tener un transistor, que significa 1 bit. En la imagen de arriba, puede ver una cuadrícula de celdas con transistores (donde se aplica polisilicio al silicio) y transistores faltantes (donde hay espacios en el silicio). Para leer información de la ROM, se activa una línea de selección de columna (basada en la dirección) para seleccionar los bits almacenados en esta columna y obtener un bit de cada fila en la salida. Puede ver las líneas verticales de selección de columna (líneas de selección de columna) de polisilicio y las filas horizontales de metal en la foto de arriba. Las líneas verticales de silicio dopado están conectadas a tierra.

El diagrama a continuación (correspondiente al segmento ROM 4x4) explica cómo funciona la ROM. Cada celda tiene un transistor (negro) o no tiene un transistor (atenuado). Cuando se aplica voltaje a la línea de selección de la columna de polisilicio, los transistores en esta columna se encienden y conectan a tierra las filas de metal correspondientes. (en este caso, el transistor NMOS es como una puerta que está abierta si la entrada es 0 y cerrada si la entrada es 1.) Las "filas" metálicas del circuito emiten los datos almacenados en la "columna" seleccionada.

Esquema del segmento ROM 4x4Las señales de selección de columna son generadas por un circuito decodificador. Dado que este circuito está construido con válvulas NOR, primero explicaré el diseño de las válvulas. El siguiente diagrama muestra una puerta NOR de cuatro entradas construida con cuatro transistores y una resistencia pull-up (aunque, de hecho, un transistor especial realiza la función de la resistencia). En el lado izquierdo del circuito, todas las entradas son 0, por lo que todos los transistores están apagados y la resistencia pull-up mantiene la señal de salida en un nivel "alto". En el lado derecho, 1 se aplicó a una de las entradas, activando el transistor. El transistor está conectado a tierra, por lo que la señal de salida ahora tiene un nivel "bajo". Por lo tanto, si alguna entrada es alta (1), la salida es baja (0). Entonces este circuito implementa la válvula NOR.

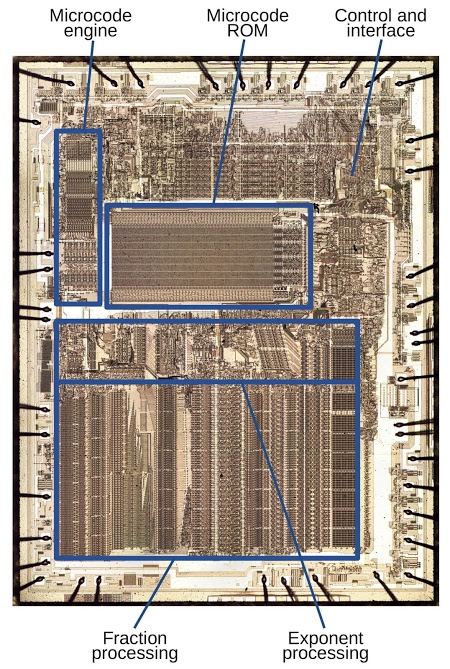

Puerta NOR de 4 vías construida con transistores NMOSEl circuito decodificador de selección de columna recibe los bits de dirección entrantes y activa la línea de selección correspondiente. El decodificador contiene una puerta NOR de 8 entradas para cada columna, es decir, una puerta NOR para cada dirección. La foto muestra dos elementos NOR que generan señales de selección de columna (por simplicidad, mostraré solo cuatro de las 8 entradas). Cada columna utiliza una combinación diferente de líneas de dirección y líneas de dirección rellenadas como entrada, eligiendo una dirección diferente. Las líneas de dirección están en una capa de metal, que se elimina en la foto a continuación; las líneas de dirección se resaltan en verde. Para determinar la dirección asociada con la columna, observe los pines cuadrados asociados con cada transistor y observe qué líneas de dirección están conectadas. Si todas las líneas de dirección conectadas a los transistores de una columna están en un nivel bajo (0), la puerta NOR seleccionará esa columna.

La foto a continuación muestra una pequeña parte del decodificador ROM con las 8 entradas para puertas NOR. Puede leer direcciones binarias examinando cuidadosamente las conexiones en la barra de direcciones. Observe el patrón binario: a1 une los valores de cambio en cada columna, a2 une alterna cada dos columnas, a3 une cada cuatro columnas, etc. A0 se fija porque este circuito decodificador selecciona columnas impares; un circuito ROM similar selecciona direcciones pares (tal separación era necesaria para que el decodificador encajara en el chip, ya que cada columna del decodificador es dos veces más ancha que la celda ROM).

Parte del decodificador de direcciones para el microcódigo ROM 8087. El decodificador convierte la dirección de 8 bits en señales de selección de columnaEl último componente de la ROM es un conjunto de multiplexores que reduce 64 líneas de salida a 8 líneas. Cada multiplexor 8 a 1 selecciona una de sus 8 entradas en función de la dirección. El siguiente diagrama muestra uno de los multiplexores de línea del procesador 8087, construido con ocho transistores de paso grandes, cada uno de los cuales está conectado a una de las líneas de "línea". Todos los transistores están conectados a la salida, por lo que cuando se activa el transistor seleccionado, transfiere su entrada a la salida. Los transistores multiplexores son mucho, mucho más grandes que los transistores en la ROM para reducir la distorsión de la señal de la ROM. Un decodificador (similar al considerado anteriormente, pero más pequeño) genera ocho líneas de control multiplexor a partir de tres líneas de dirección.

Uno de los multiplexores de 8 filas en ROM. Aquí puede ver capas de (poli) silicio, con compuestos metálicos pintados en naranja.Para resumir, ROM almacena bits en una cuadrícula. Utiliza ocho bits de dirección para seleccionar una columna en la cuadrícula. Luego, tres bits de la dirección seleccionan las ocho salidas deseadas de las "líneas".

ROM en capas

Hasta ahora, he explicado un dispositivo ROM típico que almacena un bit por celda. Entonces, ¿cómo pudo el 8087 almacenar dos bits por celda? Si observa detenidamente, el microcódigo ROM 8087 contiene cuatro tamaños diferentes de transistores, si considera la ausencia de un transistor como uno de los tamaños (6). Con cuatro opciones para cada transistor, una celda puede codificar dos bits, duplicando aproximadamente la densidad (7). La sección actual explica cómo los cuatro tamaños de transistores generan cuatro corrientes diferentes, y cómo los circuitos analógicos y digitales del chip convierten estas corrientes en dos bits.

Una micrografía del microcódigo ROM 8087 muestra cuatro tamaños diferentes de transistores. Esto permite que la ROM almacene dos bits por celda.El tamaño del transistor controla la corriente a través del transistor (8). Un factor geométrico importante son los diferentes anchos de silicio (rosa), donde se cruza con el polisilicio (líneas verticales), creando transistores con diferentes anchos de compuerta. Dado que el ancho de la puerta controla la corriente a través del transistor, los cuatro tamaños del transistor generan cuatro corrientes diferentes: el transistor más grande pasa la mayor parte de la corriente y no fluye corriente si no hay transistor.

La corriente ROM se convierte en bits en unos pocos pasos. Primero, una resistencia pull-up convierte la corriente en voltaje. Luego, tres comparadores comparan el voltaje con el voltaje de referencia para generar señales digitales, determinando qué voltaje es mayor / menor. Finalmente, las puertas lógicas convierten las señales de salida del comparador en dos bits de salida. Este patrón se repite ocho veces, generando un total de 16 bits en la salida.

Esquema para leer dos bits de una celda ROMEl diagrama anterior realiza estos pasos de conversión. Como resultado, uno de los transistores ROM es seleccionado por la línea de selección de "columna" y el multiplexor (discutido anteriormente) que genera una de las cuatro corrientes. Luego, una resistencia pull-up (12) convierte la corriente del transistor en voltaje, como resultado de lo cual el voltaje depende del tamaño del transistor seleccionado. Los comparadores comparan este voltaje con tres voltajes de referencia y la salida 1 si el voltaje de la ROM es mayor que el voltaje de referencia. Los comparadores y los voltajes de referencia requieren un diseño cuidadoso, ya que los voltajes ROM pueden diferir en solo 200 mV.

Los voltajes de referencia están en el medio entre los valores de voltaje esperados de la ROM, lo que permite algunas fluctuaciones de voltaje. El voltaje ROM "bajo" es más bajo que todos los voltajes de referencia, por lo que todos los comparadores emitirán 0. El segundo voltaje ROM es más alto que Ref 0, por lo que el comparador más bajo genera 1. En el tercer voltaje ROM, los dos comparadores más bajos emiten 1, y al máximo el voltaje ROM en la salida de los tres comparadores 1. Por lo tanto, los tres comparadores producen cuatro patrones de salida diferentes, dependiendo de la ROM del transistor. Los elementos lógicos luego convierten la salida del comparador en dos bits de salida (10).

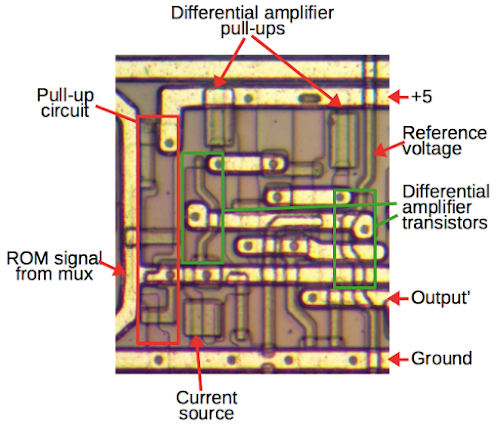

El diseño del comparador es interesante porque es un puente entre los mundos analógico y digital, produciendo 1 o 0 si el voltaje de la ROM es mayor o menor que el voltaje de referencia. Cada comparador contiene un amplificador diferencial que amplifica la diferencia entre el voltaje ROM y el voltaje de referencia. La salida del amplificador diferencial acciona una puerta que estabiliza la salida y la convierte en una señal de nivel lógico. El amplificador diferencial (abajo) es un circuito analógico estándar. La fuente actual (símbolo a continuación) proporciona corriente continua. Si uno de los transistores tiene un voltaje de entrada más alto que el otro, la mayor parte de la corriente pasa a través de este transistor. La caída de voltaje a través de las resistencias hará que la salida correspondiente sea más baja y la otra salida más alta.

Un diagrama que muestra el funcionamiento de un par diferencial. La mayor parte de la corriente pasará a través de un transistor con un voltaje de entrada más alto, dando como resultado una señal de salida más baja. El siguiente símbolo de doble círculo es una fuente de corriente continua ILa foto a continuación muestra uno de los comparadores en un chip; capa de metal en la parte superior, transistores debajo. Consideraré solo los puntos principales de este complejo esquema; Ver nota 12 para más detalles. La señal de la ROM y el multiplexor se suministra a la izquierda. Un circuito pull-up 12 convierte la corriente en voltaje. Dos transistores amplificadores diferenciales grandes comparan el voltaje de la ROM con el voltaje de referencia (entrada desde arriba). Las salidas del amplificador diferencial van al circuito del obturador (disperso en la fotografía); la salida del obturador está en la esquina inferior derecha. La fuente de corriente del amplificador diferencial y las resistencias pull-up están hechas de transistores de modo de agotamiento. Se utilizan tres comparadores de salida en cada circuito de salida, lo que da un total de 24 comparadores.

Cada voltaje de referencia es generado por un transistor de tamaño cuidadosamente seleccionado y un circuito pull-up. El circuito de referencia de voltaje está diseñado para estar lo más cerca posible del circuito de señal de la ROM, de modo que cualquier cambio en la fabricación de chips afectará a ambos elementos por igual. El voltaje de referencia y la señal ROM utilizan el mismo circuito de carga. Además, cada circuito de voltaje de referencia incluye un transistor muy grande, idéntico al transistor multiplexor, aunque no hay multiplexación en el circuito de señal de referencia, solo para garantizar la "coincidencia" de los circuitos. Los tres circuitos de voltaje de referencia son idénticos, excepto por el tamaño del transistor de referencia (9).

Un circuito que genera tres voltajes de referencia. Los tamaños de los transistores de referencia están entre los tamaños de los transistores ROM. La capa de óxido no se eliminó por completo de esta parte de la matriz, debido a qué remolinos de color aparecieron en la fotoPara armar todo el rompecabezas, la foto a continuación muestra la ubicación de los componentes del microcódigo ROM en el chip (12). La parte principal del circuito ROM consiste en transistores que almacenan datos. El circuito del decodificador de columna se encuentra arriba y debajo de los datos de la ROM. La mitad de los decodificadores de selección de columna están en la parte superior y la mitad en la parte inferior, para un mejor diseño. El circuito de salida está a la derecha. Ocho multiplexores cortan 64 líneas de líneas a ocho. Luego, ocho líneas entran en los comparadores, generando 16 bits en la salida de la ROM a la derecha. El circuito de referencia sobre los comparadores genera tres voltajes de referencia. En la parte inferior derecha, un pequeño decodificador de línea controla los multiplexores.

ROM de firmware de Intel 8087 FPU etiquetada con los componentes principalesAunque inicialmente puede parecer que una ROM multinivel será la mitad de una ROM convencional, el efecto no es tan notable debido al circuito adicional de los comparadores, y al hecho de que los transistores en sí mismos son ligeramente más grandes, debido a la necesidad de usar varios tamaños. A pesar de esto, una ROM multinivel ahorró aproximadamente el 40% del espacio que ocuparía una ROM normal.

Ahora que entiendo la estructura de la ROM, puedo simplemente (pero tediosamente) leer el contenido de la ROM, solo mirando el tamaño de cada transistor bajo un microscopio. Pero, sin conocer el conjunto de instrucciones de microcódigo, los contenidos de la ROM son inútiles.

Conclusiones

8087 « » . Intel 1981 iAPX 432.11 , 1980- . , - , , , , , , (14).

, , -. - (13). - 4 ( 16 ) , (QLC, quad-level cell). , 1980- , .

, @kenshirriff 8087. RSS-. 8087.

- 8087 1648 ( ), 16 , 26368 . , Intel .

- 8087: Intel , 40 000 , , 45 000. . , , PLA , , «» , . , .

- 8086 8087 ; . , 8087 8086 , 8087. , 8086 , . , 8087 8086 ( 8088), , 8086. , 8086, . 8087 , 8086. , 8086 8087, , . , 8087 , , . 8087 , , . 8087 8087, .

- , , , , , . , ROM, , . , 8 1/8 , 1/8 . , , (, 1 × 16) , . , «» . , Intel ; 1405 512 . , «» - 20 .

- IBM : ( , ), (link). , Xerox Alto, . , . , .

- , Hacker News , 8087 . , , .

- 1980- . Mostek : . , . Intel, ( ), . ( ) . ( ), , . Z-80 «», , , , . , , Z-80 , , , .

- . ( — .) ( , ) , . MOSFET . Wikipedia

- , -. , . , Reference 0 , . , , . : , , , . - , , , .

- : = 00, = 01, = 11, = 10. ; , , . (. «Two Bits Per Cell ROM», Stark).

- Intel iAPX 43203 (1981) , 8087. «The interface processor for the Intel VLSI 432 32 bit computer,» J. Bayliss et al., IEEE J. Solid-State Circuits, vol. SC-16, . 522-530, 1981 . 43203 - iAPX 432. Intel iAPX 432 1975 , «», Intel 1980- . iAPX 432 , Intel 8086 , 1978 . Intel 8086 , x86, iAPX 432 1986 .

- ( «Multiple-Valued ROM Output Circuits») . . (T3, T4, T5) . 4 5 , 3, ( ). ( ) T6, . ().

- - SLC ( single level cell — ), MLC (multi level cell — ), TLC (triple level cell — ) QLC (quad level cell — ). , - , , - .

- «Electronics» «Four-State Cell Doubles ROM Bit Capacity» (. 39, 9 1980 .), Intel, . Intel « » COMPCON (. 209-212, 1981 .). Intel «Multiple-valued ROM output circuits» (Proc. 14th Int. Symp. Multivalue Logic, 1984). , , — « A Survey of Multivalued Memories » («IEEE Transactions on Computers», 1986 ., . 99–106) « A review of multiple-valued memory technology » (IEEE Symposium on Multivalued Logic, 1998).

, . ¿Te gustan nuestros artículos? ¿Quieres ver más materiales interesantes?

Apóyenos haciendo un pedido o recomendándolo a sus amigos, un

descuento del 30% para los usuarios de Habr en un análogo único de servidores de nivel de entrada que inventamos para usted: toda la verdad sobre VPS (KVM) E5-2650 v4 (6 núcleos) 10GB DDR4 240GB SSD 1Gbps de $ 20 o cómo dividir el servidor? (las opciones están disponibles con RAID1 y RAID10, hasta 24 núcleos y hasta 40GB DDR4).

VPS (KVM) E5-2650 v4 (6 Cores) 10GB DDR4 240GB SSD 1Gbps 1 ,

.

Dell R730xd 2 veces más barato? Solo tenemos

2 x Intel Dodeca-Core Xeon E5-2650v4 128GB DDR4 6x480GB SSD 1Gbps 100 TV desde $ 249 en los Países Bajos y los EE. UU. Lea sobre

Cómo construir un edificio de infraestructura. clase utilizando servidores Dell R730xd E5-2650 v4 que cuestan 9,000 euros por un centavo?