El diseño de dispositivos electrónicos que utilizan módulos de memoria SDRAM DDR rápidos requiere especial atención a la integridad de la señal. El artículo habla sobre una herramienta de modelado moderna para resolver tales problemas.Hoy, casi todos los dispositivos electrónicos modernos están equipados con módulos de memoria. Los servidores, las computadoras, los teléfonos inteligentes, las consolas de juegos, los navegadores GPS y la mayoría de los otros dispositivos están diseñados en base a procesadores y FPGA. Dichos dispositivos requieren una memoria de alta velocidad con un ancho de banda de canal grande o memoria de memoria de doble frecuencia (DDR). Con cada nueva generación de DDR SDRAM (memoria dinámica sincrónica con acceso aleatorio y velocidad de transferencia de datos duplicada), se reduce la velocidad de intercambio de datos, la capacidad y el consumo de memoria.

Al diseñar las placas de circuito impreso de dispositivos con memoria DDR, pueden surgir una serie de dificultades, una de las cuales es el problema de la integridad de la señal. Este artículo aborda los problemas de garantizar la integridad de las señales en dispositivos que utilizan memoria DDR.

Ruido y jitter de la señal de datos digitales.

Al recibir / transmitir la señal de reloj del bus de memoria desde el controlador al microcircuito, pueden producirse diversas interferencias debido a la propia fluctuación de fase de los transmisores y receptores, pérdidas en las líneas de transmisión, ruido e interferencia. Todo esto lleva a la aparición de jitter y distorsión de la forma de la señal de la interfaz digital.

Cualquier energía no deseada añadida a una señal ideal puede considerarse como ruido. Puede ser causada por la interferencia de las líneas vecinas, el canal de transmisión mal diseñado, la impedancia inconsistente y otros factores que conducen al desenfoque del frente del pulso. En ausencia de ruido, la señal real es idéntica a la ideal.

Cualquier desviación de la forma de onda ideal afecta su integridad. Las desviaciones de tiempo (fluctuación de fase) y las desviaciones de amplitud / voltaje (ruido) también afectan el rendimiento del sistema. Si no garantiza la integridad de las señales, el sistema DDR utilizará la información incorrecta, lo que aumentará significativamente la intensidad de los errores de bit BER (tasa de error de bit). Finalmente, el sistema funcionará de manera incorrecta e ineficiente.

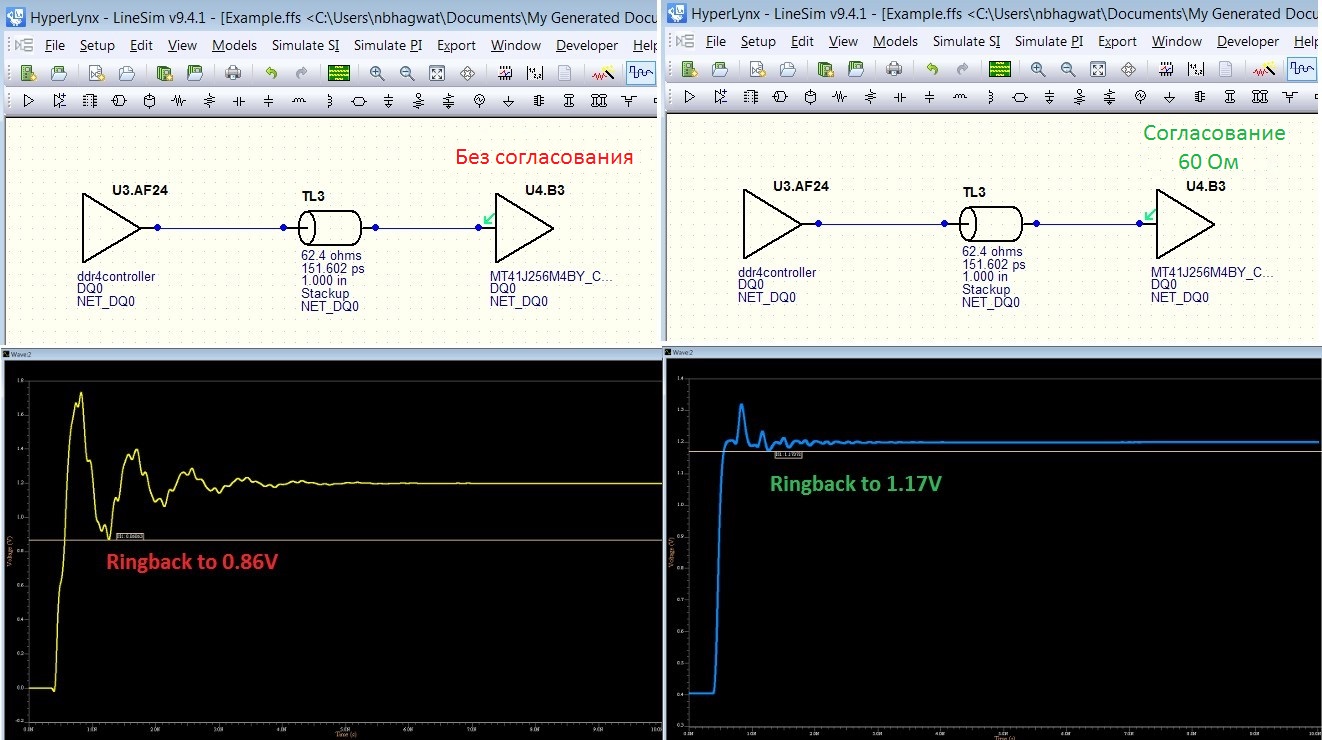

Considere un ejemplo específico. Si el ingeniero conecta el transmisor a un receptor inconsistente ubicado a cierta distancia de él, la forma de onda será similar a la que se muestra en la Figura 1a: aquí puede ver claramente el "timbre" en el nivel de 0.86 V y las emisiones espurias crecientes en el nivel de 1.75 V a una señal de 1.2 V. Todo esto puede conducir a un mal funcionamiento de la lógica DDR4 y, si la placa de circuito está diseñada con dicha topología, se producirán errores de probabilidad del 100% en el flujo de datos, lo que, a su vez, puede conducir a un funcionamiento incorrecto del sistema .

Teóricamente, es posible resolver problemas con "timbres" y emisiones reduciendo la longitud de la línea de transmisión, pero, desafortunadamente, esto rara vez funciona en la práctica. La forma más efectiva es hacer coincidir el receptor / transmisor por impedancia, como resultado de lo cual el nivel de ruido disminuye y la forma de la señal mejora mucho (ver Fig. 1b).

Fig. 1. Una topología que tiene problemas con la calidad de la señal: a) antes de la coordinación b) después de la coordinación

Fig. 1. Una topología que tiene problemas con la calidad de la señal: a) antes de la coordinación b) después de la coordinaciónA este respecto, surge la pregunta de qué índice de aprobación usar y cómo calcularlo, porque incluso un pequeño cambio en el índice puede afectar significativamente el rendimiento del sistema. La única forma de resolver este problema es simulando, en particular, utilizando los asistentes de reconciliación interactivos utilizados en HyperLynx.

Problemas de tiempo en DDRx

Dado que los buses paralelos que operan a frecuencias de gigahercios, como DDR3 / 4, se utilizan cada vez más en el diseño de placas de circuito impreso, los problemas de integridad de la señal son especialmente graves. DDR3 SDRAM, por ejemplo, difiere significativamente en términos de velocidad y rendimiento de frecuencia de DDR2: la frecuencia de reloj máxima de DDR2 es de 800 MHz, y la frecuencia máxima de DDR3 es de 1600 MHz. Debido a la reducción del voltaje de suministro de las células, los creadores del nuevo tipo de RAM lograron reducir su consumo de energía hasta en un 15%, lo que, dado el impresionante rendimiento de DDR2, se puede llamar un verdadero avance. DDR3 utiliza una topología de bus de comando / dirección / control de red "fly-by" con coincidencia intramódulo (ODT). Al mismo tiempo, DDR3 crea nuevos problemas de integridad de señal, en particular, asociados con circuitos ODT, velocidades de datos más altas y distorsión de tiempo.

A pesar del hecho de que hay controladores que realizan la calibración automática de lectura / escritura, optimizando los intervalos de tiempo, el desarrollador debe garantizar la sincronización correcta. Los límites de tiempo en las interfaces DDR3 son tan pequeños que el enfoque empírico para la optimización ya no es suficiente, y para garantizar el funcionamiento de la interfaz a altas velocidades, es necesario un análisis detallado del circuito.

Tales relaciones temporales complejas son difíciles de analizar sin la ayuda de herramientas adicionales. Para identificar y eliminar problemas potenciales en general o para calcular relaciones temporales complejas, los ingenieros deben analizar las relaciones causa-efecto, que es una tarea compleja y que requiere mucho tiempo.

Tales problemas de diseño a menudo conducen a demoras en la planificación del proyecto y, como resultado, aumentan significativamente el tiempo que tarda el producto terminado en ingresar al mercado. Las herramientas de simulación avanzadas y potentes pueden ayudar a los ingenieros a encontrar y corregir errores rápidamente al optimizar las señales a un nivel aceptable de BER.

Análisis de integridad de la señal de los sistemas DDR SDRAM

El Comité de Normalización de Ingeniería de Semiconductores de JEDEC ha aprobado una lista de requisitos que deben seguirse al desarrollar productos de calidad. Es fundamental que las SDRAM DDR cumplan estos requisitos para garantizar un funcionamiento adecuado y evitar problemas de integridad de la señal. Sin embargo, llevar a cabo todas las mediciones y cálculos necesarios a menudo está lleno de muchas dificultades.

A veces, estos cálculos se pueden evitar por completo siguiendo estrictamente las instrucciones de diseño proporcionadas por el proveedor del controlador. Pero, ¿qué pasa si tales recomendaciones no se pueden implementar debido a varias limitaciones en proyectos específicos? ¿Qué hacer si toma mucho tiempo asegurarse de que el proyecto cumpla con todas las recomendaciones y requisitos? En tales situaciones, debe usar herramientas para verificar rápidamente el proyecto antes de ponerlo en producción.

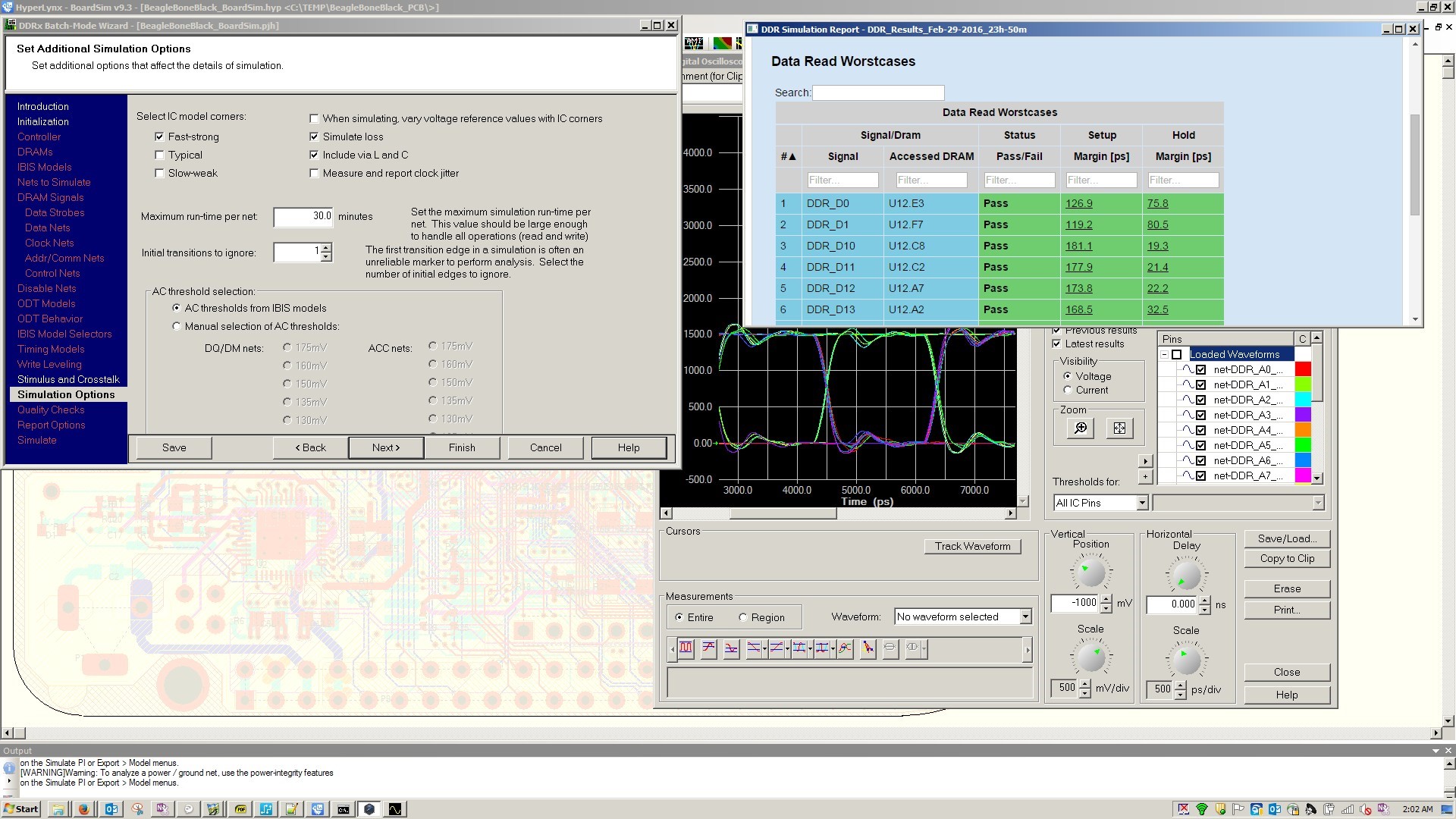

Usando HyperLynx DDR (ver Figura 2), puede simular todo el canal DDR en una iteración. Para hacer esto, solo necesita vincular los modelos de dispositivo apropiados que están disponibles en los sitios web de los fabricantes. Después de eso, el tiempo de configuración para la simulación tomará solo diez minutos, lo que permitirá un mayor modelado sin demora.

Fig. 2. Modelado con el ayudante interactivo HyperLynx DDR

Fig. 2. Modelado con el ayudante interactivo HyperLynx DDREl proceso de configuración es intuitivamente simple, ya que el asistente solicita todos los parámetros necesarios para configurar la simulación de forma interactiva. El usuario simplemente ingresa información relevante, como la elección de modelos IBIS para controladores y dispositivos de memoria, tasas de transferencia para ciclos de lectura / escritura, ODT, etc. Todas las configuraciones creadas se pueden guardar para uso futuro, lo que reducirá el tiempo de configuración en proyectos futuros. Las simulaciones se pueden realizar antes o después del rastreo, lo que ayuda a determinar los requisitos para la pila de PCB.

Análisis de resultados de simulación.

La simulación incluye análisis de integridad de señal y sincronización de todo el bus DDR. Al finalizar el proceso de simulación, se crea un informe que incluye datos sobre el paso (no paso) de las verificaciones, de acuerdo con la información de configuración y los datos que se ingresaron en el asistente interactivo. Los resultados se pueden filtrar y organizar adecuadamente para un estudio cuidadoso de los problemas de temporización e integridad de la señal en los ciclos de lectura / escritura de datos, en buses de dirección y comando o circuitos diferenciales. Todos los resultados del informe están vinculados a los datos de simulación correspondientes, para un acceso rápido a la herramienta para ver formas de onda gráficas de señales.

Los datos de simulación en modo por lotes creados por el asistente DDRx se pueden guardar en el disco, lo que le permite utilizar el osciloscopio HyperLynx para simular varios circuitos simultáneamente y estudiar en detalle los problemas de integridad de la señal en modo fuera de línea.

Conclusión

DDR SDRAM abre nuevas posibilidades en el desarrollo de dispositivos electrónicos. Al igual que con otras interfaces de alta velocidad, el uso de la memoria DDR tiene varias características. El problema de la integridad de la señal debe estudiarse cuidadosamente para evitar iteraciones innecesarias y costosas en la fabricación de productos. El modelado es una excelente manera de resolver este problema, ya que le permite tener en cuenta los efectos a nivel de la placa, como los cambios en la impedancia y los retrasos, proporcionando un control completo sobre la interfaz de memoria. Las potentes herramientas de análisis ayudarán a garantizar que los proyectos cumplan con las recomendaciones de JEDEC y garantizarán que el producto final funcionará con alto rendimiento y confiabilidad.

HyperLynx DDR puede ser compartido por muchas empresas de diseño de PCB CAD, incluidos PADS y Xpedition.

Este artículo fue publicado en la revista MODERN ELECTRONICS No. 7, 2018 (www.soel.ru)